数制、码制、逻辑运算

基本逻辑符号

半加器

用与非门实现

全加器

编码器

编码就是将信息装换成独特的代码或信号输出的电路

普通编码器:任何时候只允许输入一个有效编码信号,否则输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信号。当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码。

译码器

译码是将二进制码翻译成代表某一特定含义的信号。(即电路的某种状态)

常见的唯一地址译码器

1.二进制译码器 :2-4线74HC139,3-8线74HC138

2.二——十进制译码器:7442

3.显示译码器:CMOS七段显示译码器74HC4511

数据选择器

能实现数据选择功能的逻辑电路。它的作用相当于多个输入的单刀多掷开关,又称“多路开关”。

也就是说,它可以从多个输入信号中选择一个并将其输出。

特点:并入串出

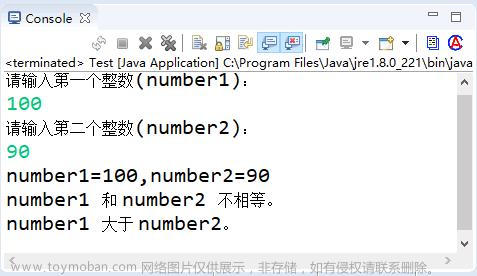

数值比较器

对两个二进制数字进行比较(A、B),以判断其大小的逻辑电路。

看真值表比较清晰明了

对比图

推荐博客:数字电路学习笔记(七):经典组合逻辑器件(上) - 知乎

时序逻辑和组合逻辑区别

组合逻辑电路:它是一种没有存储元件或状态(也就是无记忆)的逻辑电路。它的输出仅由输入决定,不依赖于任何时钟等外部信号。组合逻辑电路的特点是:输出只与当前的输入有关;它可以实现各种基本的逻辑运算,如与、或、非、异或、多路选择器等。典型的应用包括算术逻辑单元、编码器/译码器、加法器、比较器等。

时序逻辑电路:它是一种具有存储元件或状态(也称为有记忆)的逻辑电路。它的输出既依赖于当前的输入,也依赖于前一时刻的状态。时序逻辑电路的动态行为受到时钟信号控制,每当时钟信号发生变化时,它的状态才会更新或者转移。常见的时序逻辑电路包括:触发器、计数器、状态机等。

区别:组合逻辑电路是一种组合多个逻辑门进行的简单逻辑运算的电路,其输出由输入数值决定,并且不受之前任何状态或电路模块的影响。时序逻辑电路则是另一种类型,具有状态和输出两个属性,在每个时钟脉冲到来时,其状态会根据先前状态以及输入信号更新,使得输出与状态相关。在应用方面,时序逻辑电路通常用于实现计数器、定时器、开关模式控制器等需要存储状态或需要特定时序行为时使用;而组合逻辑电路通常用于构建数学操作电路和编码解码电路。

锁存器与触发器

锁存器---对脉冲电平敏感的存储电路,在特定输入脉冲电平(高或低电平)作用下改变状态。

触发器---对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

同步清零与异步清零

异步清零是指与时钟不同步,即清零信号有效时,无视触发脉冲,立即清零,不需要时钟配合;

同步清零是时钟触发条件满足时检测清零信号是否有效,有效则在下一个时间周期的触发条件下,执行清零,需要时钟配合。

举个例子:从0000开始计数, 反馈清零的信号是1010,那么异步清零的芯片74X161计算模时1010不算有效状态(时间过短不稳定),M = 10;而在同步清零74X163芯片中,1010算一个有效状态,M = 11,和同步置数计算模过程一样。

串行和并行

串行通信

缺点:传输速度较慢

优点:传输线少、连线简单,特别适合多位数据的长距离通信;

并行通信

缺点:若数据位数较多、传送距离较远时,则线路复杂,成本较高且干扰大,不适合远距离传送。

优点:传送数据速度很快,传输效率高,

(别和计组混在一起)

各芯片真值表

8421BCD编码器

8-3线 优先编码器CD4532

EO为允许输出控制端,GS为组选信号输入端。

允许多个输入信号同时有效,输出时对优先级别高的输入信号进行编码

3-8译码器 74HC138

能将3位二进制信号输入转换为8条输出线之一

CMOS七段显示译码器74HC4511

用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路,能提供较大的拉电流,可直接驱动LED显示器,有拒绝伪码的特点。

能够将4位二进制输入信号转换为相应的七段LED数字输出

低电平有效,高电平锁存

74LS151 8选1数据选择器

能将8个输入信号中的任何一个输出到单个输出线上

74LS153 2个四选一数据选择器

1G、2G为两个独立的使能端;B、A为公用的地址输入端;1C0~1C3和2C0~2C3分别为两个4选1数据选择器的数据输入端;Y1、Y2为两个输出端。

① 当使能端1G(2G)=1时,多路开关被禁止,无输出,Y=0。

② 当使能端1G(2G)=0时,多路开关正常工作,根据地址码B、A的状态,将相应的数据C0~C3送到输出端Y。

74HCT194 (双向移位寄存器)

它是四位移位寄存器,能够在各种数字信号处理应用中实现数据的输入、输出和传递等操作

74VC161(异步清零)

低电平有效,立即清零

低电平有效,下个时钟上升沿到来置数

其中有一个是低电平时,保持

1.异步清零端优先级一般是最高的

2.CR为清零,PE为预置 TC终止计数端(与最大计数信号(如1111)同步产生)

CP = CET*Q3*Q2*Q1*Q0 = 1

CO是表示进位输出信号 CET是错误检测输出信号

3.Q: CR为什么一定要接1端,悬置不是也是高电平吗?

A: CR端悬空时处于不定状态。因CMOS电路的输入电阻很大,悬空的输入端很容易感应外界 的电磁干扰,导致输入端电平忽高忽低,如果出现了低电平将导致整个电路不受时钟控制。

(这件事告诉我们不要随便悬空,除非你有充分理由可以这么干)

1100-->1101-->1110-->1111这四个部分是游离态,这种现象是自启动现象,一个正确的时序系统前提条件是具备自启动特性

用74VC161组成256进制计数器(需要两片74VC161)

同一时钟源

TC信号与最大计数信号同步产生,也就是说TC产生信号是在第十五个脉冲的上升沿,而进位要求满16才进一,TC消失的时候才是第十六个脉冲信号到来的时候。经过一个非门后,TC第十五个脉冲的下降沿就可以给高位进位信号

拓展 :

1.怎么用74VC161组成160进制计数器?

可以使用级联法实现,160不是质数可以转换成10*16,16位为低位,10位为高位,然后用反馈置数or清零

2.怎么用74VC161组成质数进制计数器?

质数不能拆解,所以不能用级联法实现,只能用反馈法实现

级联法:可以实现大模非质数值

反馈法:可以实现任何模数

74LS90

R0A、R0B:清零端

S9A、S9B:异步置9端

R0A、R0B优先级一样,其中一个工作时,另一个要设置成无效,S9A、S9B同理

R0A、R0B同时为高电平,清0;

S9A、S9B同时为高电平,置9;

又叫2-5-10进制异步计数器

最大模值为10

下降沿有效

8421BCD计数

CP1接Q0的时候为8421BCD码计数,有n个90芯片进制就可以到达99...9进制(n个9)

Q:怎么看进制?

A:拿两个90芯片级联为例,如果想要24进制,那么高位芯片需要2(0010),低位芯片需要4(0100)

那么只要拿出高位芯片的Q2端和地位芯片的Q3进行与门,结果接到两个芯片的两个R端清零端即可实现

注:QA~QD = Q0~Q3

五-二进制计数

文章来源:https://www.toymoban.com/news/detail-456363.html

文章来源:https://www.toymoban.com/news/detail-456363.html

注意5421BCD的真值表顺序是Q0 Q3 Q2 Q1 文章来源地址https://www.toymoban.com/news/detail-456363.html

到了这里,关于数字逻辑(计科专业)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!