累加器实验

实验环境

计算机组成原理实验环境

实验目的

- 理解累加器的概念和作用。

- 连接运算器、存储器和累加器,熟悉计算机的数据通路。

- 掌握使用微命令执行各种操作的方法。

实验要求

- 做好实验预习,读懂实验电路图,熟悉实验元器件的功能特性和使用方法。在实验之前设计好要使用的微命令,填入表 6-2 、表 6-3 和表 6-4 表中。

- 按照实验内容与步骤的要求进行实验,对预习时填写好的微命令进行验证与调试,遇到问题请冷静、独立思考,认真仔细地完成实验。

- 写出实验报告。

实验电路

本实验使用的主要元器件有:4 位算术逻辑运算单元 74LS181 ,8 位数据锁存器 74LS273 。8 位正沿触发寄存器 74LS374 、三态输出的总线收发器 74LS245 ,2Kx8 静态随机存储器 6116 ,时序发生器,与非门、与门、开关、指示灯等。各芯片详细说明请见附录。

图 1 为本实验数据通路总框图,其中 ALU 由 2 片 74LS181 构成,DR 1、DR2 和 AR 均为一片 74LS273 ,RAM 为一片 6116 芯片,R0 寄存器为一片 74LS374 芯片,△ 表示三态门 74LS245 ,时序发生器为虚拟实验系统提供的虚拟组件。

实验电路中涉及的主要控制信号如下:

- M :选择 ALU 的运算模式( M=0 ,算术运算;M=1 ,逻辑运算)。

- S3,S2,S1,S0:选择 ALU 的运算类型。如 M=0 时,设为 1001 表示加法运算。

- Cn:向 ALU 最低位输入的进位信号, Cn=0 时有进位输入, Cn=l 时无进位输入。

- LDDR1:DR1的数据加载信号,与 T4 脉冲配合将总线上的数据打入 DR1 中。LDDR1 和 T4 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDDR1=1 时在 T4 的上升沿将数据锁存到 DR1 。

- LDDR2:DR2 的数据加载信号,与 T4 脉冲配合将总线上的数据打入 DR2 中。LDDR2 和 T4 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDDR2=1 时在 T4 的上升沿将数据锁存到 DR2 。

- MR:芯片 74LS273 的清零信号,低电平有效.本实验恒置为 1 。

- ALU-BUS :ALU 输出三态门使能信号,为 0 时三态门打开,ALU 运算结果输出到总线。

- SW-BUS :开关输出三态门使能信号,为 0 时三态门打开,SW7 ~ SW0 上的数据传送到总线。

- CE:6116 片选信号。为 0 时 6116 正常工作。

- OE:存储器读信号, CE=0、 OE=0 为读操作,在实验中将其接地,恒置为0。

- WE:存储器写信号。与 T3 脉冲配合实现存储器写操作。WE 和 T3 通过与非门进行与非运算之后连接到 6116 芯片的 WE 引脚, 引脚低电平有效。在 CE=0、 OE=0 的条件下,当 WE=1 且 T3=l 时进行写操作,否则进行读操作。

- LDAR: AR 的地址加载信号,与 T3 脉冲配合将总线上的地址打入 AR 中。LDAR 和 T3 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDAR=1 时在 T3 的上升沿将地址锁存到 AR 。

- R0-BUS:R0 芯片的输出控制信号,连接 74LS374 芯片的 OE 引脚,为 0 时将 R0 中的数据输出到总线,为 1 时输出高阻态。

- LDR0:R0 的数据载入信号,与 T4 脉冲配合将总线上的数据打入 R0 中。LDR0 和 T4 通过与门进行与运算之后连接到 74LS374 芯片的 CP 引脚,当 LDR0=l 时在 T4 的上升沿将数据存入 R0 。

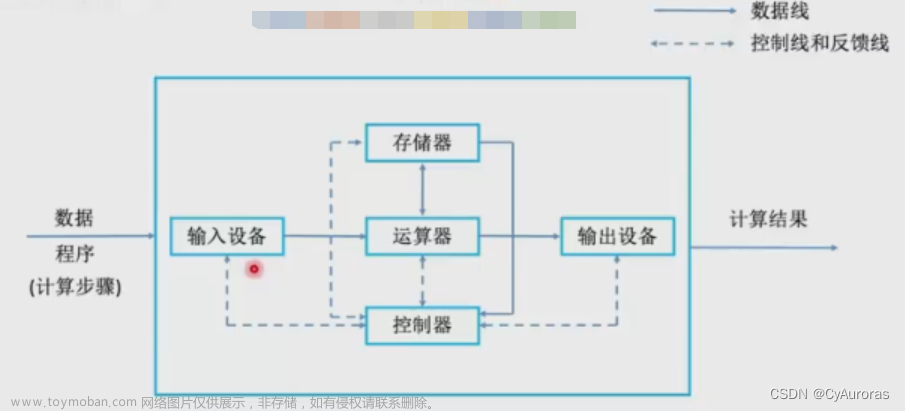

实验原理

实验所用电路如图 6-1 所示,累加器、运算器、存储器、数据开关等通过总线相连。在数据开关(SW7 ~ SW0)上设置的数据或地址可经三态门发送至总线。DR1 和 DR2 从总线上接受数据并传送到 ALU 进行运算,运算结果经三态门送回总线。地址寄存器 AR 从总线上获取地址并送至存储器,存储器按地址进行读写。存储器在读操作时,将读出的数据发送至总线,在写操作时从总线获取数据并写入。R0从总线上获取数据并保存起来,需要时再把存入的数据输出到总线上。数据显示灯与总线相连,流经总线的所有数据和地址都将显示在数据灯上。

累加器是一种寄存器,用于存放算术逻辑运算的操作数或中间结果。本实验把 R0 作为累加器,完成一次简单的算术运算。为了调动各功能部件完成预定任务,就要确定在每一个 CPU 周期,要对每一个功能部件发出什么样的控制信号。

为方便进行实验,将图 6-1 中的所有控制信号归纳到表 6-1 中。实验的主要任务就是确定这些控制信号在每一个 CPU 周期的取值。

实验内容与步骤

本实验将 R0 用作累加器,完成一次加法运算。其中,被加数由数据开关输入,加数存放在存储器中,其地址也从数据开关输入.运算结果存入存储器中,存入的地址由数据开关设置。

- 运行虚拟实验系统,导入实验电路图,在电路中加入一个 74LS374 芯片作为累加寄存器 R0 ,将 R0 的数据线与总线相连.

- 按照表 6-1 中列出的所有控制信号线,并仔细检查一遍,确保连接正确。连接好的电路如图 6-2 所示。

- 进行电路预设置。将 DR1 、DR2 和 AR 的 置1, 时序发生器的 Step 置 1 。

- A→R0,A 从数据开关输入。具体步骤如下:

(1)设计要使用的微命令,填入表 6-2中。

(2) 打开电源。

(3) 设置控制信号1:数据开关→R0():将数据开关设置为 A(00000011) ;单击时序发生器的 Start 按钮,等待一个 CPU 周期。 - 进行累加运算 B+R0→R0 , B 为存储器操作数,B 的地址由数据开关输入,运算结果存入 R0 。具体步骤如下:

(1)设计好要使用的微命令,填入表 6-3 中。

(2)设置控制信号2:存储器操作数→DR2 ( ):将数据开关设为 B 的地址(00001000);单击 Start 按钮。等待一个 CPU 周期后,B 的值已存入 DR2 。

(3)设置控制信号3:R0→DR1 ( ):单击 Start 按钮,等待一个 CPU 周期后,R0 的值已存入 DR1 。

(4)设置控制信号4:DR1+DR2→R0( );单击 Start 按钮。等待一个 CPU 周期后,运算结果已存入 R0。 - 存储 R0→存储单元 C,C 为存储单元地址,从数据开关输入。具体步骤如下:

(1)设计好要使用的微命令,填入表 6-4 中。

(2)设置控制信号5:存储单元地址→AR ( );将数据开关设置为 C (00001001) : 单击 Start 按钮。等待一个 CPU 周期后,地址 C 已存入 AR 。

(3)设置控制信号6:R0→存储单元( ):单击 Start 按钮。等待一个 CPU 周期后,运算结果已存入存储单元。

(4)单击菜单中的 “工具/存储器芯片设置” ,查看存储单元 09H 的值。

实验验证

参考总线与微命令

在原先基础上另加一个 R0 寄存器

加上 R0 寄存器的总线路图

预设置电路和设置微命令

打开电源

右上角按钮分别对应

S3、 S2、 S1、 S0、 M、 Cn、 CE、 WE、 LDAR、 LDDR1、 LDDR2、 ALU-BUS、 SW-BUS、LDR0、R0-BUS、

设置控制信号1

数据开关→R0( ):将数据开关设置为A(00000011);单击时序发生器的Start按钮,等待一个CPU周期。

设置控制信号2

存储器操作数→DR2( ):将数据开关设为 B 的地址(00001000);单击 Start 按钮。等待一个 CPU 周期后,B 的值已存入 DR2 。

设置控制信号3

R0→DR1( ):单击 Start 按钮,等待一个 CPU 周期后,R0 的值已存入 DR1 。

设置控制信号4

DR1+DR2→R0( );单击 Start 按钮。等待一个 CPU 周期后,运算结果已存入R0 。

设置控制信号5

存储单元地址→AR( );将数据开关设置为 C (00001001):单击 Start 按钮。等待一个 CPU 周期后,地址 C 已存入 AR 文章来源:https://www.toymoban.com/news/detail-456406.html

文章来源:https://www.toymoban.com/news/detail-456406.html

设置控制信号6

R0→存储单元( ):单击 Start 按钮。等待一个 CPU 周期后,运算结果已存入存储单元。 文章来源地址https://www.toymoban.com/news/detail-456406.html

文章来源地址https://www.toymoban.com/news/detail-456406.html

思考与分析

- 什么是累加器?它的作用是什么?

- 什么是微指令?微指令与微命令的关系是什么?

到了这里,关于计算机组成原理 累加器实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!