关注+星标公众号,及时获取更多技术分享~

作者 | 冰茶奥利奥

微信公众号 | 嵌入式电子创客街

这两年项目上提国产化的越来越非常严格,尤其是今年,军工项目更加特殊,总体单位直接提百分百纯国产化。这百分百国产化器件中,有外资控股的企业不能选,企业家是外籍华人的不能选。像思瑞浦之类的。直接又把百分之八十的国产化企业淘汰了。

最近项目上用到了复旦微的FPGA,之前也没有用过复旦微的产品,只知道复旦微的产品大都是正向抄袭的Xilinx,然后就开始踩坑。

这次遇到的问题是,一部分板子有大概率问题不能正常加载程序。最后定位问题是DC-DC的3.3V出的非常缓慢,大概20ms左右才能达到3.3V的水平。那这样会给FPGA的配置带来什么问题呢?

我们知道,7系列FPGA的上电时序是1.0V->1.8V->3.3V。在1.8V出来后,当3.3V达到一个阈值,FPGA就已经可以开始程序的配置了。

我们量了一下复旦微芯片的CFG_STA引脚,它大概在3.3V上升到1.5V的时候就已经拉高为高电平了。这个引脚一旦是高,FPGA就开始从Nor Flash读取数据了。但是此时Nor Flash的3.3V电还没有达到要求的水平,读取就有可能出问题了。

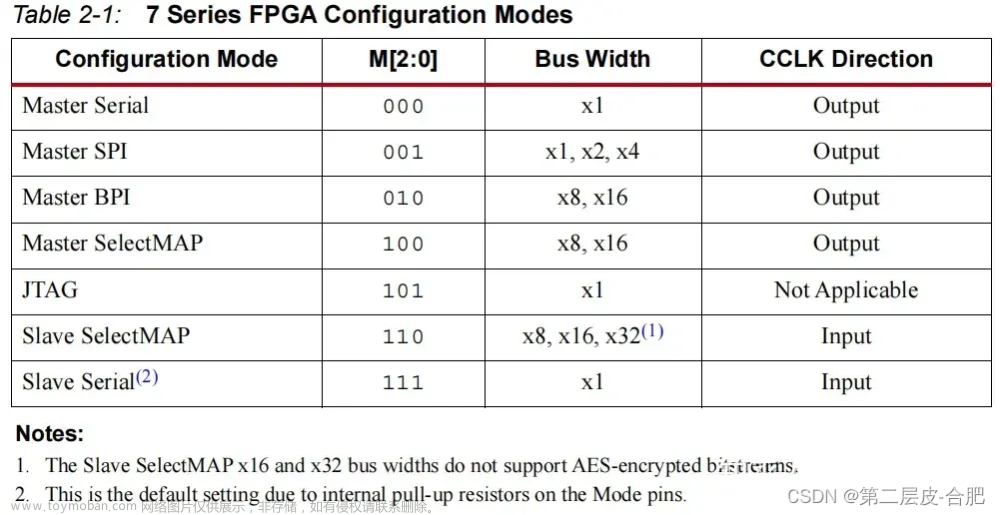

于是我研究了一下Xilinx的手册中对这部分功能的描述,想看看FPGA的上电时序究竟是个什么样子的。下面这个图是从UG470手册里面截取出来的,7系列FPGA SPI x1配置模式的时序。

我们看见INIT_B这个引脚的上升沿后跟着一根线,过了一段时间后配置时钟CCLK就开始发数了,那么这个等待的时间是多少呢?我们看看它下面跟着的解释。看我红色框出来的内容,大概意思就是图中波形代表事件的相对顺序,不按比例,具体的时间需要查看SPI Flash的手册。所以这里是没有指出来这个时间是多少的。我们再查查其他的说明。似乎和Program_B和INIT_B两个信号有关。

我们直接找PROGRAM_B和INIT_B这两个信号的说明。下面是PROGRAM_B这个信号。有一个note,说即便把这个引脚拉低也不能保持FPGA处于复位状态,可以考虑的是,使用INIT_B引脚可以延后调整芯片的上电配置时间。

那我们就具体看看这个INIT_B引脚。

有一个关键信息。可以看到这个INIT_B引脚本身是个开漏(OD)的引脚,也就是三态门,可做输入也可做输出。当FPGA启动完成后,这个引脚被配置为高阻态,这时候驱动状态就交由外部的上拉电阻,外部上拉电阻可以把这个引脚拉高。当FPGA检测到这个引脚被拉高后,就开始进行程序配置。因此,这种状态下,INIT_B这个引脚完全可以由用户外部去一直拉低,如果一直拉低,FPGA就会一直等待配置。一旦被拉高,就会开始从SPI FLash读取程序。

因此,我们可以设想怎样改进下当前的电路设计。我们可以把3.3V的PG(power good)信号引到这个引脚上,当3.3V完全输出的时候,PG信号输出高电平,此时INIT_B引脚也被它拉高,然后才开始读取SPI Flash开始程序的配置。

如果您觉得这篇文章帮到了你,请点赞或者留下您的评论,您的鼓励是我前进的动力~

关注博主公众号 “嵌入式电子创客街” 获取更多及时技术分享~

关注+星标公众号,及时获取更多技术分享~ 文章来源:https://www.toymoban.com/news/detail-456880.html

文章来源地址https://www.toymoban.com/news/detail-456880.html

到了这里,关于关于Xilinx、复旦微 7系列 FPGA “Init_B”引脚的深入探讨的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!