1 简介

在一些大电压、大电流的产品中,上电的瞬间通常会有较大的电流冲击,下图是一款产品上电过程中波形。最大的电流达到14.2A,这种过流有可能损坏电子元器件。

电流过充波形

解决上述问题,通常采取的策略是在电源的入口增加缓启动电路,也成为软起动。缓启动就是电源缓慢开启,限制电源启动时的浪涌电流。

缓启动电路的目的主要有两个:

- 延迟单元电源的上电时间;

- 较小上电的冲击电流。

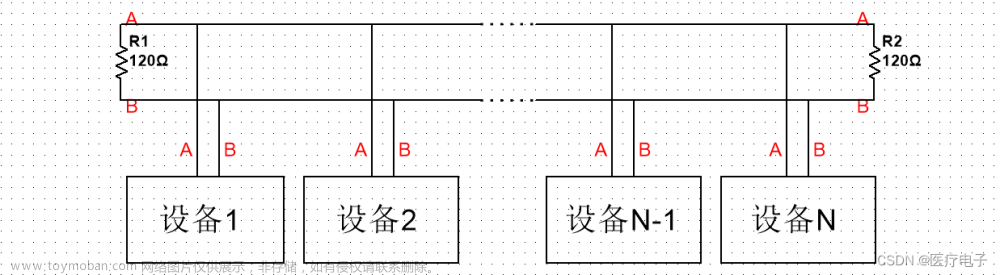

2 电路说明

电路的主要组成部分包含了R1、R2、C1、Q1组成,通过简单元器件就可以使用缓启动功能。电源的输出是由PMOS的打开和关闭控制,缓启动的实质就是让PMOS管的打开的时间变得缓慢,此处我们采取的措施是在栅极和源极之间增加一个电容C1,是PMOS的导通时间变得缓慢。导通的时间于R1、R2、C1的参数是强相关的。

缓启动电路

下面就是有、无缓启动时,电压随时间变化的示意图:

缓启动对照图

从图中可以明显的看出,增加缓启动电路后,电压起来的时间周期更改,能避免上电过程中的冲击电流。

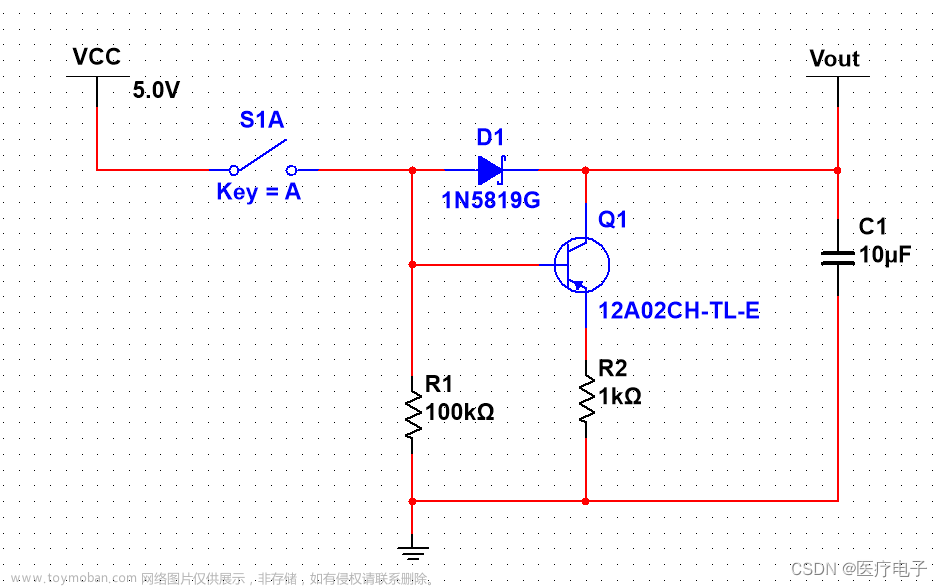

部分单板的电源需要外部的使能信号进行控制,可以新增一个三极管进行控制,具体电路

带控制缓启电路

3 原理图分析

针对电容相关的计算公式

电荷量 = 电容容量 * 电容两端电压:

Q = C * U

电荷量 = 电流 * 时间

Q = I * t

因此:I = (CU)/t

分析:当电容容量越大,电压越高,时间越短,电流就会越大,从而形成冲击电流。

缓启动电路

在缓启动电路中,电阻R1、电阻R2和电容C1构成分压式RC时间常数电路,,C1并联在Q1的GS极之间,也就是Vc1=Vgs。当12V电源刚加到单板时,C1未充电,Vgs=0,MOS不导通,电源模块不供电。随后,12V通过R1,R2向C7充电,当C1的电压达到Vth时,MOS开始导通,这一阶段,完成的是延时上电的作用.

4 参数设定

在电路的设计过程中,应该考虑三极管的参数,特别是ID通常裕量至少为30%。此处我们以FQD8P10TM-F085为例,不同温度下允许的电流不同。在25℃时,电流不能超过4.62A;100℃时,电流不能超过2.94A。否则MOS管可能会被烧毁。

FQD8P10TM-F085规格书

5 总结

- 缓启动的时间常数电路必须确保电容充电完成后其电压不能大于15V,因为一般大功率MOS管的G,S间击穿电压在20V左右,电压过高,会损坏MOS管。

- 缓启动的延迟时间不能太长。

🗡延迟太长,热拔插时,单板接口信号线已连接,而电源仍未上电,会造成接口器件闩锁损坏;文章来源:https://www.toymoban.com/news/detail-457554.html

🗡缓启动关键器件MOS管在从截止到导通转换的过程中瞬间功耗是非常大的,如果电容充电过于缓慢,造成边沿时间太长,MOS管将因为功耗过大而损坏。延时一般取几十毫秒。文章来源地址https://www.toymoban.com/news/detail-457554.html

到了这里,关于数字电路硬件设计系列(三)之缓启电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!