0 🍺实验目的

(1)熟悉触发器的逻辑功能及特性。

(2)掌握集成D和JK触发器的应用。

(3)掌握时序逻辑电路的分析和设计方法。

1 🍺实验仪器及材料

2 🍺实验内容及步骤

用D触发器(74LS74)组成二分频器、四分频器

74LS74是双D触发器(上升沿触发的D触发器),其管脚图和功能表如下:

每个74LS74芯片有两个D触发器,每个D触发器有D输入端,CLK时钟输入端(上升沿有效),CLR直接复位端(低电平有效) , PR直接置位端(低电平有效),Q、Q'输出端。D触发器的特性方程为:

(1)用一个D触发器组成二分频器

1)电路图

2)二分频器时序图

用逻辑分析仪观察时钟信号(CLK)和二分频输出(Q)的时序图(逻辑分析仪用法见后附注意事项)

Q的周期是CLK的二倍,Q的频率是CLK的½,所以输出Q是时钟信号CLK 的二分频。

(2)用一片74LS74组成四分频器

参考一个D触发器组成二分频器的方法,用两个D触发器(一片74LS74)组成四分频器,并用逻辑分析仪观察时序图

1)电路图

2)四分频器时序图

用逻辑分析仪观察时钟信号(CLK)和四分频输出(Q)的时序图

用JK触发器(74LS73)组成同步十进制加法计数器

74LS73是双JK触发器(下降沿触发的JK触发器),其管脚图和功能表如下:

每个74LS73芯片有两个JK触发器,每个JK触发器有J、K输入端,CLK时钟输入端(下降沿有效),CLR直接复位端(低电平有效),Q、Q'输出端。JK触发器的特性方程为:

设计方法:

(1)逻辑抽象

十进制计数器有10个稳定状态,最少应由4个触发器组成。触发器的输出分别记为Q3Q2Q1Q0,按十进制加法的计数规律编码,作状态转换表如下所示:

状态转换图如图所示:

(2)

根据状态转换表,作出次态Q'3Q'2Q'1Q'0和输出C的卡诺图:

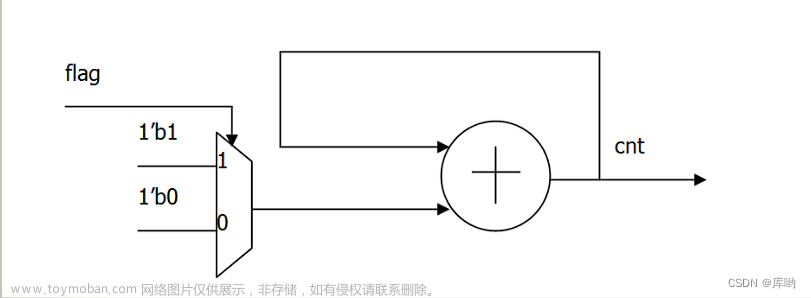

卡诺图分解并化简,得到状态方程:

将1010-1111这6个无效状态分别代入状态方程求其次态,检查电路是否能够自启动,如果不能自启动,需要重新化简状态方程。

(3)将Q'3Q'2Q'1Q'0的状态方程与JK触发器的特性方程Q'=JQ'+K'Q对比,得到每个触发器

对比,得到每个触发器的驱动方程:

(4)根据驱动方程画电路图(替换成自己的电路图),需要用到与门。文章来源:https://www.toymoban.com/news/detail-458191.html

(5)用逻辑分析仪观察并记录CLK、Q0、Q1、Q2、Q3、C的时序图(替换成自己的电路图)用标尺截取10个时钟,观察每个时钟对应的状态,如果状态是按照十进制加法计数器的状态转换图变化,则设计正确,记录时序图。文章来源地址https://www.toymoban.com/news/detail-458191.html

3 🍺实验内容及步骤

数字逻辑实验:内含实验报告,和所用实验软件,还有实验电路图,其中包括七个实验实验报告中的各个实验的答案都已填好!!!-C++文档类资源-CSDN文库

到了这里,关于时序逻辑电路一——数字逻辑实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!