前言

小编是做通信相关的FPGA工程师,在工作当中必然要用到快速傅里叶变换,那么就有必要讲解一下关于Xilinx器件的FFT IP核用法。首先Xilinx器件经过ise到vivado的软件升级,其对应FFT IP核也相应的升级了,由之前的版本升级为现在的aAXI4总线版本。本文着重介绍AXI4总线版本,也会将之前的ISE版本进行介绍。

提示:以下是本篇文章正文内容

一、ISE14.7的FFT使用详解

版本号:Fast Fourier Transform v7.1

该版本FFT IP核是Xilinx公司配套FPGA开发工具ISE14.1推出的,其最大的系统时钟达到550MHz,最大的数据吞吐量达到550Msps,最大输入数据和相位因子位宽为34bit,支持所有的主流Xilinx FPGA芯片。

输入数据按自然顺序显示,输出数据可以按自然顺序显示,也可以按位/数字倒序输出。

FFT核接收复杂的数据样本,但可以通过将所有虚数输入设置位零来对实部数据进行转换。由于有限字长效应,在转换过程中,引入了噪声,导致输出数据不是完全的对称,故建议在执行实值FFT时,使用输出数据的后半部分(N/2+1,N)。

1、IP核配置页面介绍:

- Page 1

- 组件名称:要实例化的核心组件的名称。名称必须以字母开头,由a ~ z、a ~ z、0 ~ 9、_组成。

- 通道数:选择1 ~ 12的通道数。多通道操作可用于三种突发I/O架构。变换长度:选择所需的点大小。从8到65536的2的所有幂都是可用的。

- 实现选项:选择一个实现选项,如第6页架构选项中所述。流水线,流I/O, Radix-2,突发I/O,和Radix-2 Lite,突发I/O架构支持点大小8到65536。Radix-4, Burst I/O架构支持的点大小为64到65536。自动检查选择最小的实现,满足指定的目标数据吞吐量,前提是指定的目标时钟频率是实现FFT核心在FPGA设备上实现。目标时钟频率和目标数据吞吐量只用于自动选择一个实现和计算延迟。核心不保证运行在指定的目标时钟频率或目标数据吞吐量。

- 转换长度选项:选择是否在运行时可配置转换长度。当转换长度不能在运行时配置时,核心使用更少的逻辑资源并具有更快的最大时钟速度。

- Page 2

- 数据格式:选择输入和输出的数据样本是定点格式,还是IEEE-754单精度(32位)浮点格式。当核心处于多通道配置时,浮点格式不可用。

- 精度选项:输入数据和相位因数可以独立配置为8至34位的宽度,包括。当“数据格式”为“浮点型”时,输入数据宽度固定为32位,相位因数宽度可根据所需的噪声性能和可用资源设置为24位或25位。

- 缩放选项:有三个选项,适用于所有架构:未缩放-所有的整数位增长被携带到输出。这可以使用更多的FPGA资源。缩放-一个用户定义的缩放计划决定了数据如何在FFT阶段之间缩放。块浮点——核心决定需要多大程度的缩放才能充分利用可用的动态范围,并将缩放因子报告为块指数。

- 可选引脚:可选引脚有CE (Clock Enable)、SCLR (Synchronous Clear)、OVFLO (Overflow)。如果同时勾选“同步清除”,则会覆盖“时钟启用”。如果不选择该选项,可能会节省一些逻辑资源,并可能获得更高的时钟频率。

- 舍入模式:在蝴蝶的输出时,需要修剪数据路径中的lbs。这些位可以使用收敛舍入截断或舍入,这是一种无偏置舍入方案。当一个数的小数部分正好等于1 / 2时,如果数是奇数,收敛四舍五入;如果数是偶数,收敛四舍五入。收敛舍入可以用来避免直流电偏置,否则将引入截断后的蝴蝶阶段。选择此选项将增加切片使用,并由于额外的延迟而导致转换时间的小幅增加。

- 输出顺序:输出数据选择位/数字反转顺序或自然顺序。基于Radix-2的架构(流水线,流I/O, Radix-2,突发I/O和Radix-2 Lite,突发I/O)提供位反转排序,而基于Radix-4的架构(Radix-4,突发I/O)提供位反转排序。对于流水线、流I/O架构,选择自然顺序的输出顺序会增加核心使用的内存。对于突发I/O架构,选择自然阶输出会增加整体转换时间,因为需要一个单独的卸载阶段。如果输出顺序是自然顺序,可以选择循环前缀插入。循环前缀插入可用于所有体系结构,通常用于OFDM无线通信系统。

- 输入数据时序:在以前版本的Xilinx FFT核心中,输入数据在相应的样本索引之后应用三个周期,以允许处理包含数据样本的块内存。在许多情况下,这是没有必要的,在错误的周期中应用数据会使核心功能不正常。这个计时现在可以配置为向后兼容以前的版本,或者在样本索引和应用数据之间没有延迟(默认)。

- Page 3

- 存储选项:数据和相位因数(突发I/O架构):对于突发I/O架构,块RAM或分布式RAM都可以用于数据和相位因数存储。数据和相位因子存储可以在分布式RAM中存储所有的点大小,包括1024点。

- 数据和相位因子(流水线,流I/O):在流水线,流I/O解决方案中,数据可以部分存储在块RAM中,部分存储在分布式RAM中。每个管道阶段,从输入端计数,使用更小的数据和相位因子存储器比前阶段。用户可以选择使用块RAM进行数据和相位因子存储的管道阶段的数量。后期阶段使用分布式RAM。GUI上显示的默认值在这两者之间提供了很好的平衡。如果输出顺序是自然顺序,用于重排序缓冲区的内存可以是块RAM或分布式RAM。对于点大小小于或等于1024的点,重排序缓冲区可以使用分布式RAM。-当为流水线,流I/O架构选择块浮点时,自然顺序和位倒序输出数据需要RAM缓冲区。在这种情况下,重排序缓冲区选项仍然可用,对于所有小于2048的点,可以选择分布式RAM。

- 混合存储:数据,相位因子,或重新排序缓冲区记忆存储在块内存,如果内存的大小大于一块内存,内存可以由一个混合块公羊和分布式内存,在大多数的数据存储在块公羊和几位剩下存储在分布式RAM。这种混合内存是完全由多个块ram构建内存的替代方案。它减少了块RAM计数,但代价是增加了所使用的片的数量。只有当块RAM用于一个或多个内存,并且混合内存实现所需的片数低于每个内存256个lut的内部阈值时,混合内存才可用。如果满足这些条件,混合存储器就可用,可以选择。

- 优化选项:Complex multiplier:有三个选项可用于定制复杂multiplier的实现:使用CLB逻辑:所有复杂multiplier都将使用切片逻辑构造。这适用于性能要求较低的目标应用程序,或具有少量XtremeDSP片/Mult18x18s的目标设备。-使用3-乘法器结构(资源优化):所有复杂的乘法器将使用3个真正的乘,5个加减结构,其中乘法器使用XtremeDSP片/ multi18x18s。这减少了XtremeDSP切片/Mult18x18计数,但使用了一些切片逻辑。在Spartan-3A DSP、Spartan-6和Virtex-6设备中,这种结构可以利用XtremeDSP片预加器来减少或消除额外的片逻辑,提高性能。-使用4乘法器结构(性能优化):所有复杂的乘法器将使用4个实乘,2个加减结构,利用XtremeDSP片/ multi18x18s。这种结构产生了最高的时钟性能,但牺牲了更专用的乘数。在具有XtremeDSP片的设备中,添加/减去操作是在XtremeDSP片中实现的。在带有Mult18x18s的设备中,添加/减去操作使用切片逻辑。注意:核心可能会在内部覆盖复杂的乘数实现,以确保使用最少的XtremeDSP片/ multi18x18s,而不会影响性能。由于这个原因,在3-multiplier和4-multiplier选项之间切换时,一些核心配置在XtremeDSP slice/Mult18x18的使用上可能没有差异。但是,如果选择使用CLB逻辑,则切片逻辑将始终被使用。

- 蝴蝶算法:有两个选项可用于定制蝴蝶实现:-使用CLB逻辑:所有蝴蝶阶段将使用切片逻辑构建。-使用XtremeDSP片:对于具有XtremeDSP片的设备,该选项强制使用XtremeDSP片中的加法器/减法器实现所有蝶形阶段。

2、IP核主要端口说明

| 信号名称 | 方向 | 说明 |

|---|---|---|

| XN_RE | IN | 输入操作数实部,2进制补码 |

| XN_IM | IN | 输入操作数虚部,2进制补码 |

| START | IN | FFT启动信号,高电平有效,对于突发I/O结构,该电平为高时,开始加载数据和变换计算,对于流水线数据流I/O结构,START开始加载数据,直接进行变换计算 |

| UNLOAD | IN | 输出结果信号,高有效,只在突发I/O时有效 |

| NFFT[4:0] | IN | 变换点数,仅应用于实时可配置时设置变换点数,具体NFFT变换点数参考数据手册 |

| NFFT_WE | IN | NFFT的使能信号,高有效 |

| FWD_INV | IN | 控制信号,=1实现FFT,=0实现IFFT |

| FWD_INV_WE | IN | FWD_INV写使能,高有效 |

| SCALE_SCH | IN | 缩放因子,该端口仅在使用有缩放算法中可用,对于无缩放算法、块浮点或者单精度浮点不可用 |

| SCALE_SCH_WE | IN | SCALE_SCH写使能,高有效 |

| CP_LEN | IN | 循环前缀的长度,从变换结束开始的采样数,在整个变换结果输出之前作为循环前缀初始化输出,仅在有循环前缀插入时可用 |

| CP_LEN_WE | IN | CP_LEN写使能,高有效 |

| CE | IN | 时钟使能,高有效。低电平时将核暂停在当前状态,核内所有逻辑都暂停,当高电平后允许核继续工作 |

| SCLR | IN | 同步清除,高电平有效,该信号为高时,所有输出引脚,内部计数器和状态变量都复位到初始状态,所有加载过程、变换计算和输出过程都停止并重新初始化 |

| CLK | IN | 时钟信号,上升沿有效 |

| XK_RE | OUT | 输出数据实部,有符号数 |

| XK_IM | OUT | 输出数据虚部,有符号数 |

| XN_INDEX | OUT | 输入数据索引 |

| XK_INDEX | OUT | 输出数据索引 |

| RFD | OUT | 准备好接收数据信号,输入数据有效 |

| BUSY | OUT | 核忙信号,在进行FFT转换时为高电平 |

| DV | OUT | 输出数据有效指示信号,高有效 |

| DONE | OUT | FFT完成信号,是脉冲信号,只存在一个时钟,在DONE信号变高后,IP核开始输出计算结果 |

| BLK_EXP[4:0] | OUT | 块指数,表示应用的缩放数,仅对浮点算法有效 |

| EDON | OUT | 提前完成信号,在DONE前一个时钟变高 |

start启动信号:可以是连续为高进行连续FFT变换。当只维持一个时钟时,可以进行非连续FFT变换。

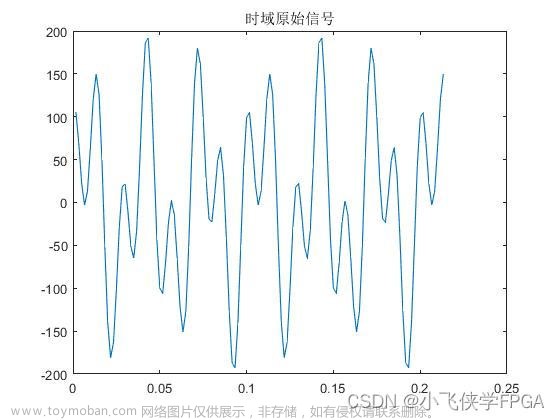

该IP核使用非连续数据流方式插入数据的时序图如图所示。由图中可以看出,第一段FFT转换结果输出滞后于其采样开始时间,而这种延迟随着采样点数的增加,FFT输出数据的延迟也会增加。

连续数据流方式插入数据时序图:

二、FFT IP核使用

如下为小编例化的FFT IP核代码片段:

my_fft my_fft_inst (

.clk (clk ),// input clk

.sclr (!rst_n ),// input sclr

.start (start ),// input start

.xn_re (sig ),// input [7 : 0] xn_re

.xn_im (8'd0 ),// input [7 : 0] xn_im

.fwd_inv (1'b1 ),// input fwd_inv

.fwd_inv_we (1'b1 ),// input fwd_inv_we

.rfd (rfd ),// output rfd

.xn_index (xn_index ),// output [14 : 0] xn_index

.busy (busy ),// output busy

.edone (edone ),// output edone

.done (done ),// output done

.dv (dv ),// output dv

.xk_index (xk_index ),// output [14 : 0] xk_index

.xk_re (xk_re ),// output [23 : 0] xk_re

.xk_im (xk_im ) // output [23 : 0] xk_im

);

1.频谱

如上例化代码,在代码中直接操作实部:xk_re、虚部:xk_im,就可以得到一段波形的频谱了。再根据频率和索引的对应关系,就可以找到FFT积分区间内的频率值。

2.缩放因子的使用

在FPGA实际工程应用当中,使用FFT核就是为了得到频谱图,进而求出频率值。对过程当中的实际数据的准确度要求不严,如果工程中资源紧张,就更需要合理分布资源。故使用FFT缩放因子的功能可以有效降低FPGA实现FFT运算所占用的资源数量。缩放因子参数是压缩比例参数,由于多点运算FFT的计算量比较大,合理设置该参数可以有效减少资源的消耗。

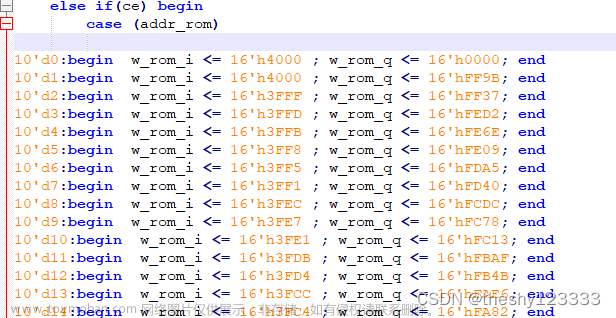

当采样点数N不是4的幂次方时,最后一组只包含一个基2阶,只能用00或者01表示,例如:N = 512时,SCALE_SCH =[00 11 11 11]就是合理的,压缩2^(0+3+3+3) = 2^9=512倍。当SCALE_SCH =[11 11 11 11]就是不合理的。

当采样点数N是4的幂次方是,对最高阶的赋值没有要求。而N点采样最好压缩N倍。

在对scaled进行赋值后,IP核的输出结果可以进行移位还原,即进行如下操作:文章来源:https://www.toymoban.com/news/detail-461233.html

assign xk_re_up = xk_re << 10;

assign xk_im_up = xk_im << 10;

注意:可以将IP核的ovflo信号引出,可以直观的在仿真波形中查看自己的scaled是否合理,如果设置的数值不够大,ovflo会溢出显示为高电平。

在此附上FFT核使用例程:https://download.csdn.net/download/qq_41894385/85535678,欢迎大家前来下载学习。文章来源地址https://www.toymoban.com/news/detail-461233.html

到了这里,关于FPGA中FFT IP核应用(一)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!