本文介绍基于windows系统的vivado安装流程,以及基本使用方法。

安装

打开Xilinx vivado的官方网站,点击进入网站底部的“下载与许可”选项。

在“Version”下可以选择需要下载的版本,更早的版本可以在“Vivado 存档”选项下找到。

选择需要下载的版本,并且选择windows环境下vivado下载器。

第一次下载需要注册AMD账号。注册登录后,需要填写相关信息,此处可以随意填写。完成后即可下载vivado下载器。

打开vivado下载器,输入刚才注册的账号密码,并且选择Vivado HL System Edition进行安装。

等待vivado下载完成。

仿真

打开vivado,选择“Create Project”。

设置项目名称,项目保存的地址。

选择RTL Project。

空项目创建完成后,在“sources”中右键选择“Add Sources”添加源文件。

选择相应的源文件,点击右侧“Run Simulation”进行仿真。

综合与部署

检查过仿真出的波形后,现在需要编译烧写到开发板中。

开发板信息

使用的开发板为NEXYS A7,在综合与部署前,需要查阅相关手册,确定开发板上引脚信息,例如,NEXYS A7中E3引脚对应了板载晶振,在编写约束文件时,需要将引脚和自己编写的顶层文件的输入输出端口对应。

项目信息

编译烧写项目的构建流程和上述仿真类似,不同的是为了后续编译烧写现在需要选择开发板型号,如下图所示,本文采用的NEXYS A7开发板选择的型号为xc7a100tcsg324-1。

编写约束文件

项目创建完毕后,和上述仿真流程一样,导入编写好的verilog文件,同时,需要编写约束文件(constraints),该文件的的后缀为XXX_constraint.xdc,目的是将开发板引脚和自己编写的顶层文件的输入输出端口对应。下图为约束文件示例。

## This file is a general .xdc for the Nexys4 DDR Rev. C

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## Clock signal

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { clock }]; #IO_L12P_T1_MRCC_35 Sch=clk100mhz

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clock}];

## LEDs

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { led }]; #IO_L18P_T2_A24_15 Sch=led[0]

如图所示,设置了用户编写文件中的clock端口和led端口与开发板上引脚的对应关系,PACKAGE_PIN为引脚,IOSTANDARD为电压标准。查阅NEXYS A7手册,开发板上E3对应晶振/时钟,H17对应LED灯,所以将clock端口和E3相连,led端口和H17相连。文章来源:https://www.toymoban.com/news/detail-462172.html

编译与烧写

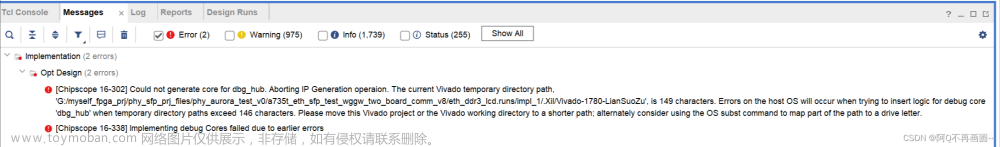

在vivado右侧选择Generate Bitstream,vivado会自动进行综合(Synthesis)和部署(Implementation)。

完成后,将开发板通过USB线连接电脑,在vivado右侧选择Auto Connect连接开发板,并且选择Program device,烧写电路。

文章来源地址https://www.toymoban.com/news/detail-462172.html

文章来源地址https://www.toymoban.com/news/detail-462172.html

到了这里,关于vivado安装、仿真、综合与部署的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!