ZYNQ7020(黑金)纯verilog驱动4.3寸RGB接口TFT液晶屏(AN430)显示彩条

简介

像素(Pixel):像素是指由图像的小方格组成的,这些小方快都有一个明确的位置和被分配的色彩数值,小方格颜色和位置就决定该图像所呈现出来的样子。

分辨率(Resolution):是屏幕图像的精密度,是指显示器所能显示的像素有多少。

像素格式(Pixel Format):将RGB三种颜色进行量化,每种颜色用8Bit表示,RGB共需要24位,即RGB888格式。

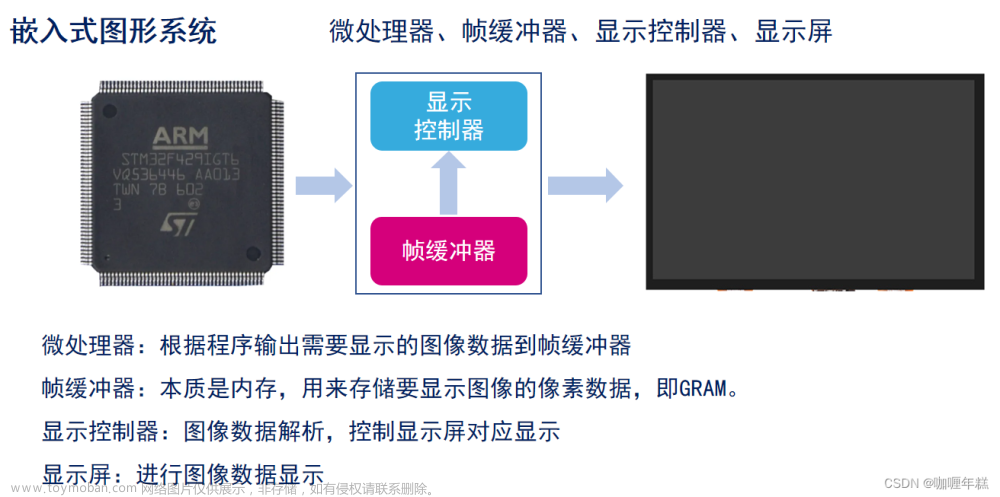

LCD屏幕的接口有RGB、MCU、LVDS、MIPI等。

时序

对于显示屏来说,是在不断的进行像素刷新的,从左往右一行一行的刷新,一行刷新完后接着刷新下一行,整个过程就是从左往右,从上往下进行刷新的。在刷新的过程中每个像素点都赋予不同的颜色,一直刷新到最后一行最后一列时,一帧图像也就显示出来了,然后再重头开始重复刷新。

每个不同尺寸的显示器都有自己对应的有效显示区域(Addressable Video)和无效显示区域(Border)。像素的刷新过程是从无效区域的左上角开始刷新到右下角结束。比如4.3寸屏的真正有效区域为480*272,其余的都是无效区域,但它们会占用刷新时间。

驱动TFT显示屏的关键是正确分析其水平和垂直扫描时序,何时输出的图像才有效。由下面两张图可以很明显的分析

下图中的HSync为行同步信号,它有效时,开始一行的刷新;VSync为场同步信号,它有效时表示一帧刷新的开始。Back Porch:后沿,Front Porch:前沿。

行扫描时序如下,场扫描时序同理,只是对应数值不同。

分析

通过下面的4.3寸屏的管脚图可知,我们设计的显示屏驱动模块的端口数为LCD_RGB、LCD_DCLK、LCD_HSYNC、LCD_VSYNC和LCD_DE。SPI开头的端口是触摸用的,这里只是显示功能可不用管。

可针对行时序和场时序分别使用一个计数器,行时序的计数器范围为0——524,场时序范围为0——285。

顶层文件,需要注的是480*272显示屏的驱动时钟是9Mhz,而我们给的系统时钟是100Mhz,所以需要用到clk_wiz IP核:

module lcd_test(

input clk ,

input rst_n ,

output [7:0] lcd_r ,

output [7:0] lcd_g ,

output [7:0] lcd_b ,

output lcd_dclk ,

output lcd_vsync ,

output lcd_hsync ,

output lcd_de

);

clk_wiz_0 clk_wiz_inst

(

// Clock out ports

.clk_out1(lcd_dclk), // output clk_out1

// Status and control signals

.reset(!rst_n ), // input reset

// Clock in ports

.clk_in1(clk));

lcd_driver lcd_driver_inst

(

.clk (lcd_dclk ),

.rst_n (rst_n ),

.lcd_r (lcd_r ),

.lcd_g (lcd_g ),

.lcd_b (lcd_b ),

.lcd_vsync (lcd_vsync ),

.lcd_hsync (lcd_hsync ),

.lcd_de (lcd_de )

);

endmodule

约束文件,根据J11扩展口和4.3寸TFT显示屏管脚图一一对应分配即可:

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_b[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_g[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {lcd_r[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports lcd_clk]

set_property IOSTANDARD LVCMOS33 [get_ports lcd_de]

set_property IOSTANDARD LVCMOS33 [get_ports lcd_hsync]

set_property IOSTANDARD LVCMOS33 [get_ports lcd_vsync]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

set_property PACKAGE_PIN J18 [get_ports {lcd_r[7]}]

set_property PACKAGE_PIN H18 [get_ports {lcd_r[6]}]

set_property PACKAGE_PIN G19 [get_ports {lcd_r[5]}]

set_property PACKAGE_PIN G20 [get_ports {lcd_r[4]}]

set_property PACKAGE_PIN F19 [get_ports {lcd_r[3]}]

set_property PACKAGE_PIN F20 [get_ports {lcd_r[2]}]

set_property PACKAGE_PIN F16 [get_ports {lcd_r[1]}]

set_property PACKAGE_PIN F17 [get_ports {lcd_r[0]}]

set_property PACKAGE_PIN K19 [get_ports {lcd_g[7]}]

set_property PACKAGE_PIN J19 [get_ports {lcd_g[6]}]

set_property PACKAGE_PIN K17 [get_ports {lcd_g[5]}]

set_property PACKAGE_PIN K18 [get_ports {lcd_g[4]}]

set_property PACKAGE_PIN M19 [get_ports {lcd_g[3]}]

set_property PACKAGE_PIN M20 [get_ports {lcd_g[2]}]

set_property PACKAGE_PIN L19 [get_ports {lcd_g[1]}]

set_property PACKAGE_PIN L20 [get_ports {lcd_g[0]}]

set_property PACKAGE_PIN D19 [get_ports {lcd_b[7]}]

set_property PACKAGE_PIN D20 [get_ports {lcd_b[6]}]

set_property PACKAGE_PIN M17 [get_ports {lcd_b[5]}]

set_property PACKAGE_PIN M18 [get_ports {lcd_b[4]}]

set_property PACKAGE_PIN L16 [get_ports {lcd_b[3]}]

set_property PACKAGE_PIN L17 [get_ports {lcd_b[2]}]

set_property PACKAGE_PIN J20 [get_ports {lcd_b[1]}]

set_property PACKAGE_PIN H20 [get_ports {lcd_b[0]}]

set_property PACKAGE_PIN E19 [get_ports lcd_clk]

set_property PACKAGE_PIN G17 [get_ports lcd_de]

set_property PACKAGE_PIN E18 [get_ports lcd_hsync]

set_property PACKAGE_PIN G18 [get_ports lcd_vsync]

set_property PACKAGE_PIN U18 [get_ports clk]

set_property PACKAGE_PIN L15 [get_ports rst_n]

ZYNQ7020标准J11扩展口管脚: 文章来源:https://www.toymoban.com/news/detail-462633.html

文章来源:https://www.toymoban.com/news/detail-462633.html

4.3寸TFT液晶屏的对应的管脚接口原理图:

测试结果: 文章来源地址https://www.toymoban.com/news/detail-462633.html

文章来源地址https://www.toymoban.com/news/detail-462633.html

到了这里,关于ZYNQ7020(黑金)纯verilog驱动4.3寸RGB接口TFT液晶屏(AN430)显示彩条的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!