MOS器件虽然漏极电流可以达到数安培,漏源电压可以达到100V以上,但是由于漏源电阻大、频率特性差、硅片面积利用率低等缺点,使得MOSFET在功率上有很大的限制。随着VMOS技术移植到MOS功率器件后,VMOSFET的耐压可达到1000V以上,电流处理能力可达到几百安培。这得益于VMOSFET短沟道、高电阻漏极漂移区和垂直导电电路等特点。VMOSFET具有VVMOS和VDMOS两种结构,下面分别来说说。

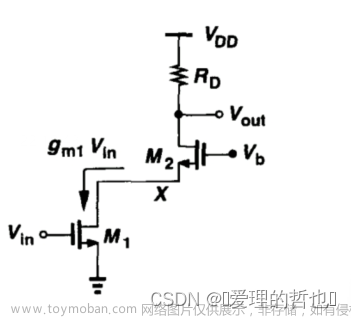

VVMOS结构介绍

VVMOS结构示意图

如上图所示,这种结构是在N+衬底和N-漂移层上,先后进行P型区N+型区两次扩散,然后利用晶体硅的各向异性刻蚀技术,造出V型槽。槽的开口深度由开口宽度决定,槽壁和硅平面成54.7°。漏极从管子背面引出。这种结构改变了MOSFET的电流方向,不再是延表面水平方向流动,而是从N+区域出发,经过与表面成54.7°的N沟道流到N-漂移区,然后垂直的流动到漏极。

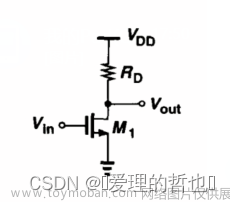

VDMOS结构介绍

VDMOS管结构示意图

VDMOS主要应用在大功率场景,其结构如上图所示,VDMOS的意思是垂直导电双扩散结构,和VVMOS不同,它不利用V型导电槽构成导电沟道,而是利用两次扩散形成的P型区和N+型区,在硅片表面的结深度之差形成导电沟道。电流在沟道内沿表面流动,然后垂直的被漏极接收。下面来详细分析一下。

VDMOS管的衬底是一个N+衬底,其上外延生长一个高阻N-型层,最终形成一个N-漂移层,该层的电阻率和外延厚度决定了器件的耐压水平。在N-外延上经过P型和N型两次扩散,形成了N+_N-_P_N+的结构,这样两次扩散深度差形成的P体区就形成了一个MOS栅结构。栅极零偏压时,阻隔图中电流Id通过。当栅极正偏压超过开启电压Vt时,沟道由P型区变成N+型,整个器件处于导通状态。由于依靠N沟道来导电,所以成为N沟道VDMOS管。反之,就是P沟道VDMOS管。由于电子的迁移率比空穴高三倍左右,N沟道的工艺比较常用,相反P沟道器件的成本价格就会比较高。

VMOSFET的优点总结

说了那么多VMOSFET的结构原理,下面来说说我们使用VMOSFET到底有什么优点。

1. 高输入阻抗、低驱动电流

2. 开关速度快、高频特性好

3. 负电流温度系数、热稳定性好,不会导致温度越高,载流子运动越快,从而导致温度继续升高的恶性循环。如下图所示。

VMOS负温度系数示意图

4. 安全工作区域大,得益于VMOSFET的负温度系数,其不存在局部热点和电流集中等问题,只要设计合理,可以避免二次击穿。如下图。

VMOS的安全工作区示意图

5. 高线性化跨导Gm:由于VMOS器件的沟道比传统MOS管更短,当Vgs上升到一定值后,Gm就保持不变,出现沟道饱和效应,如下图所示。

VMOS高线性跨导示意图

6. 几乎线性的转移特性,放大信号时失真极小,如下图所示。

VMOS转移特性比较示意图

另外整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、PCB设计、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~文章来源:https://www.toymoban.com/news/detail-464133.html

博主福利:免费获取电子工程类资料https://mp.weixin.qq.com/mp/appmsgalbum?__biz=MzkzOTM5NTE0OQ==&action=getalbum&album_id=2532293941282209792#wechat_redirect文章来源地址https://www.toymoban.com/news/detail-464133.html

到了这里,关于模拟电路设计(9)--- VMOSFET的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!