第一章 FPGA简介

第1节 什么是FPGA

FPGA的全称为Field-ProgrammableGateArray,即现场可编程门阵列。

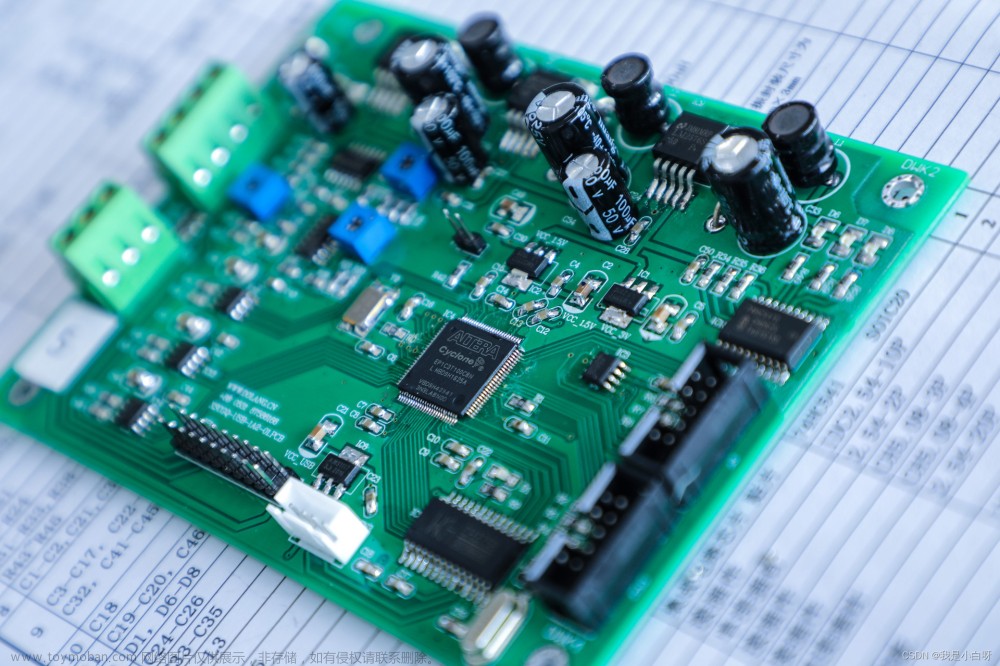

在开始学习FPGA之前,同学们首先应该清楚地了解FPGA的概念,明白FPGA到底是什么东西,可以用来做什么。FPGA是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。简而言之,FPGA就是一个可以通过编程来改变内部结构的芯片。直观来说,FPGA就是一个可以“改变”内部结构的芯片,而让这个芯片来实现怎样的功能,就需要通过编程即设计硬件描述语言,经过EDA工具编译、综合、布局布线成后转换为可烧录的文件,最终加载到FPGA器件中去,改变FPGA内部的连线,最终完成所实现的功能。此时的FPGA就可以认为是用来实现具体功能的一个粗糙的芯片。

稍微接触过硬件的人大概都听说过另一种集成电路芯片即单片机,那么FPGA与单片机在结构上有着怎样的差别呢?对于单片机而言,FPGA是一种微处理器,类似于电脑的CPU,一般是基于哈佛总线结构或者冯·诺依曼结构。单片机用途广泛,多用于控制流水线上;FPGA的结构是查找表,它的结构比较复杂,相对应的它可以实现的功能也很强大,一般应用于通信接口设计、数字信号处理等比较高端的场合,而且FPGA还有一个特殊的应用场合,即ASIC的原型验证。

相较于专职专用的ASIC,FPGA工具在开发难度上降低了许多,并且大大缩短了开发周期,而且由于FPGA是可重复编程的,其研发成本与风险也要比ASIC减少许多,更适用于复杂多变的数据中心等应用。但是FPGA也不是万能的,优势有时候也是劣势。虽然FPGA相比于单片机、CPU等集成电路芯片拥有效率更高、功耗更低的特点,但是易于开发程度远远不如单片机、CPU;在数字芯片设计领域,FPGA虽然相比ASIC具有更短的开发周期与开发难度,但是其存在着成本过高、性能较差并且在资源的利用率上远不及ASIC等问题,不能真正的替代ASIC。

第2节 FPGA的结构

FPGA可编程的特性决定了其实现数字逻辑的结构不能像专用ASIC那样通过固定的逻辑门电路来完成,而只能采用一种可以重复配置的结构来实现,而查找表(LUT)可以很好地满足这一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工艺的查找表结构。

在任意一款 FPGA 芯片说明书中可以查看到该器件具体的参数指标,其中包含可编程逻辑模块的数量、固定功能逻辑模块(如乘法器)的数目及存储器资源(如嵌入式 RAM)的大小。当然仅仅依靠这些结构是构成不了 FPGA 的基本结构的,在芯片中还有其他众多部分,但是在比较 FPGA 时,上述结构是最重要的参考指标。在最底层的可配置逻辑模块(如片上的逻辑单元)上,存在着基本的两种部件:触发器和查找表(LUT),而触发器和查找表的组合方式不同,是各个 FPGA 家族之间区别的重要依据,并且查找表本身的结构也可能各不相同(有 4 输入或 6 输入或其他)。查找表(Look-Up-Table)简称为 LUT,其本质上就是一个 RAM。

目前 FPGA 内部中多使用 4输入的 LUT,每一个 LUT 可以看成一个有 4 位地址线的 RAM。当用户在 EDA 工具上通过原理图或硬件描述语言设计了一个逻辑电路以后,FPGA 开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM 中。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查找表操作,通过地址找到对应的 RAM 中的结果,最后将其输出。以实现数字逻辑 Y=A&B&C 的功能为例。如果是在专用 ASIC 中,为了实现该逻辑,逻辑门都已经事先确定好,Y 的输出值为两个逻辑与运算后的结果,其基本的实现结构如下图所示

而在 FPGA 的结构中若要实现同样的逻辑功能,用户首先在 EDA 工具中使用硬件描述语言设计出“Y=A&B&C”逻辑代码,EDA 工具(QUARTUS 或其他开发工具)分析这一行代码,得出 A、B、C 在不同输入组合下(共 8 种),Y 的值分别是多少,其真值表如下表所示:

然后软件工具将所有的结果写到查找表上,从而实现了该代码的功能。下图就是 FPGA 的实现基本结构。查找表就类似于一个 RAM,输入 A、B、C 则相当于地址,通过 A、B、C 的地址就得读到值赋给 Y 并输出

第3节 更为复杂的FPGA架构

1985,赛灵思公司推出了第一块 FPGA 芯片—XC2064,最初的 FPGA 包含了 8×8=64 的逻辑块阵列和 85000 个晶体管,其门电路不超过 1000 个,且每个逻辑块由一个四输入的查找表和其它一些简单功能模块构成。FPGA 诞生之初由于其容量非常有限,因此只能用来执行一些相对简单的任务,如用来集中一些胶合逻辑或实现基本的状态机。

而在 22 年后,FPGA 行业两大巨头 Xilinx 和 Altera 公司纷纷推出了采用最新 65nm 工艺的 FPGA 产品,其门数量已经达到千万级,晶体管个数更是超过 10 亿个。在这 22 年间,FPGA 在紧跟半导体工艺进步的同时也推动了半导体的发展进程——2001 年采用 150nm 工艺、2002 年采用 130nm 工艺,2003 年采用 90nm 工艺,2006 年采用 65nm 工艺,而目前最新推出的 FPGA 产品更是已经使用上 10nm 工艺。随着技术的发展和工艺节点的进步,FPGA 的容量和性能在不断提高的同时,其功耗却不断的优化减少。2006 年以前四输入查找表一直被广泛使用,在一些高端器件可能会用上六输入、八输入或更多输入端口的查找表。而一个多输入的查找表又可以分解成较小输入的查找表,即能够分裂成许多更小的功能。例如一个八输入的查找表可以分解成两个四输入的查找表或分解成一个三输入加一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。

==在 FPGA 内部,有着“软内核”与“硬内核”之分。比如若利用 FPGA 的可编程性在芯片内部构造实现了一个计数器逻辑,那么在构造计数器逻辑过程中使用到的功能便可以被称为“软功能”,又称之为软内核。而如果某个功能若是直接利用芯片实现的,则是利用了芯片内部的“硬功能”,一般又称之为硬内核。==软内核与硬内核之间优势互补,软内核的优势在于可以在利用芯片资源的基础上利用编程设计让其完成需要实现的任何功能(注意是数字功能,不包括模拟功能)。而硬内核由于是实现固定功能的器件,因此其优势在于资源利用率高且功耗较低,占用硅片的面积也较小,并具有较高的性能。而两者最重要的区别在于:与软内核相比硬内核可用于实现模拟功能,例如锁相环的倍频功能,这个功能需要在模拟电路下实现,所以这一部分是在 FPGA 内部用硬件来实现的。

第4节 带嵌入式处理器的FPGA

在上文中提到“软内核”与“硬内核”的概念,而利用 FPGA 的可编程构造实现的事情之一即为使用其中的一部分数字逻辑资源制作一个或多个软处理器内核,当然,也可以实现不同规模的处理器。

举例来说,可以创建一个或多个 8 位的处理器加上一个或多个 16 位或 32 位的软处理器,而所有处理器都在同一器件中。而如果 FPGA 供应商希望提供一个占用较少硅片面积、消耗较低功率但性能更高的处理器,解决方案是将其实现为硬内核。如果需要高速、高性能的处理器,并且需要实现逻辑编程时,传统的方法是在电路板上放置处理器(如 ARM、DSP 等)和 FPGA,ARM 或者 DSP 工程师实现软件部分,FPGA 工程师实现可编程逻辑部分,两者协同合作。

现在最新的方案是使用 ZYNQ 一个芯片以更低的功耗、更高的速度实现以上功能。在 2010 年 4 月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的 ARM 处理器的 SoC 可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双 ARM Cortex-A9 MP Core 处理器系统作为“主系统”,结合低功耗 28nm 工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思 28nm 7 系列 FPGA,因此该系列产品的名称中添加了“7000”,以保持与 7 系列 FPGA 的一致性,同时也方便日后本系列新产品的命名。

考虑下面所示这个例子

这个芯片完全以硬内核方式实现的双路 ARM Cortex-A9 微控制器子系统(运行时钟高达 1GHz,包含浮点引擎,片上缓存,计数器,定时器等)以及种类广泛的硬内核接口功能(SPI,I2C,CAN

等),还有一个硬内核的动态内存控制器,所有这些组件都利用大量传统的可编程构造和大量的通用输入输出(GPIO)引脚进行了性能增强。如果是 ZYNQ 单芯片方案,是不是意味着只需要软件工程师或者 FPGA 工程师独立工作就可以了呢?目前所了解的情况是:FPGA 工程师负责搭建周边电路,如 ARM 的接口、时钟配置等,还负责可编程逻辑部分的开发。而软件部分仍然还是软件工程师负责。其主要原因在于 FPGA 逻辑开发和软件开发都是专业性比较强的技能,非常少的工程师能同时掌握这两个技能。当然,这里说的掌握性能,是专业性的、能应用到企业项目的技能,只是接触一下的不算。

第5节 数据存储以及配置分方式

随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。

在 FPGA 内部存在着存储单元片内 RAM 块,数据是存放在 RAM 中并由其来设置工作状态的,若想要 FPGA 进行工作,就需要对片内 RAM 进行编程。而如果外部有大量数据交互时,就要通过增

加外设来对数据进行暂时性的存储,如 SDRAM 存储器或者 DDR3 存储器,暂存在外设中的数据最终也是要通过 FPGA 内部的 RAM 进行存储与处理。

当在 EDA 工具上将程序设计完成之后,便需要将软件上的程序烧录进 FPGA 内部。通过不同的配置模式,FPGA 便会有不同的编程方式。以下为常用的几种配置模式

1、并行模式:通过并行 PROM、Flash 配置 FPGA;(将文件放置到PROM以及Flash中去,然后在把数据放置到FPGA)

2、主从模式:使用一片 PROM 配置多片 FPGA;

3、串行模式:串行 PROM 配置 FPGA;

4、外设模式:将 FPGA 作为微处理器的外设,由微处理器对其编程。

对于外设模式,比如用一个CPU来作为中间缓冲的,从PROM中读取数据,然后再通过CPU传输到FPGA上去,比如可以实现加密功能,而直接通过并行模式则不能实现。文章来源:https://www.toymoban.com/news/detail-465461.html

目前,主流的 FPGA 都是基于 SRAM 工艺的,在大部分的 FPGA 开发板上,使用的都是串行配置模式。由于 SRAM 掉电就会丢失内部数据,因此往往都会外接一个能够掉电保存数据的片外存储

器以保存程序。这样一来,上电时 FPGA 便将外部存储器中的数据读入片内 RAM 以完成配置,对 FPGA 编程完成后便进入工作状态;掉电后 FPGA 内部 SRAM 中存储的数据丢失,逻辑清零。以这种方式配置 FPGA 不仅能反复使用,还无需重复的手动配置。完成一次主动配置之后每次上电便会自动的实现 FPGA 的内部编程。文章来源地址https://www.toymoban.com/news/detail-465461.html

到了这里,关于第一篇 FPGA基础知识的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!