摘要

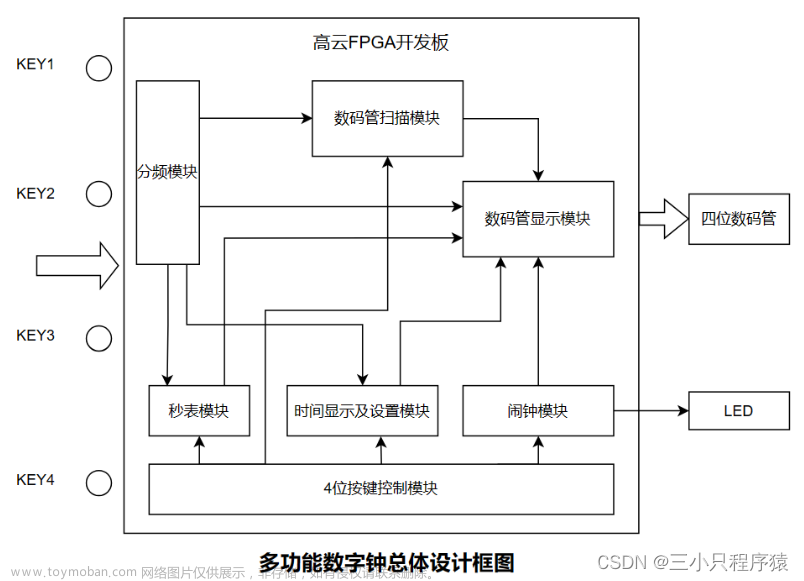

数字钟是采用数字电路实现对时、分、秒数字显示的计时装置,是人们日常 生活中不可少的必需品。本文介绍了应用FPGA芯片设计多功能数字钟的•种方 案,并讨讨论了有关使用FPGA芯片和VHDL语言实现数字钟设计的技术问题。 关键词数字钟、分频器、译码器、计数器、校时电路、报时电路。

0.引言

数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度远远 超过老式钟表。钟表的数字化给人们生产生活带来了极大的方便而且大大地扩展 了钟表原先的报时功能。因此,研究数字钟及扩大其应用,有着非常现实的意义。

- .设计要求说明

L1设计要求文章来源:https://www.toymoban.com/news/detail-465891.html

1)设计•个具有文章来源地址https://www.toymoban.com/news/detail-465891.html

到了这里,关于基于FPGA的多功能数字钟的设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!