一、开发环境的安装

首先去安路官网下载安装包工具与资料下载-国产FPGA创新者 - 安路科技

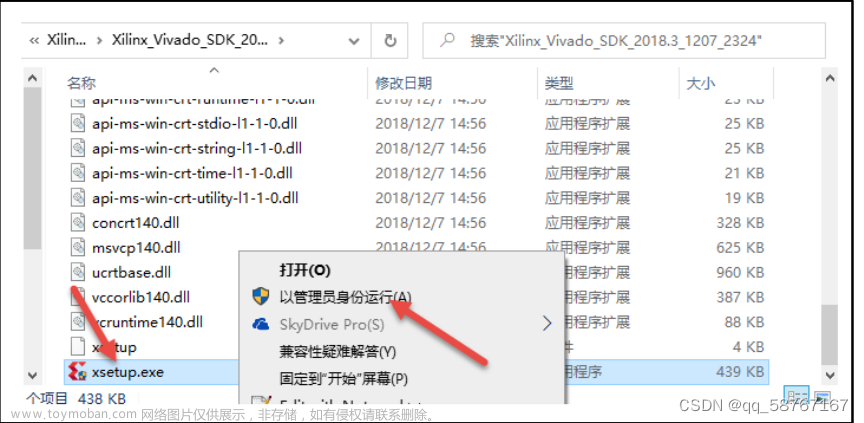

下载后解压 点击安装包直接傻瓜式安装即可

点击安装包直接傻瓜式安装即可

备注:安装后无法打开或者缺文件等情况是安路安装包不包含一些C++库,需要我们自己下载一个

DirectX修复工具(最好下载最新版,因为最新版C++库更完善)

二、一切准备工作做完开始建立第一个属于我们自己的过程,首先打开TD开发环境这里以点亮一个LED灯为演示。

Project→new Project→输入项目名称、选择存放位置与开发板芯片型号→点击OK

三、工程建立后添加/新建.v文件

添加现有的.v文件 Add→选择文件存放位置→双击添加ok确认

文件添加成功

四、编写代码运行

文本编译工具添加在1的位置可以添加我们自己的文本编译软件,在2的位置为安路自己的编译软件

代码编写

在1的位置点击编辑,如果编译不通过文件会出现在2的位置,2的位置为存放报错文件,3的位置可以看到保存信息等等

五、代码编译成功联合仿真验证Modelsim

第一步在modelsim安装路径下新建Anlogic→src文件夹用来存放仿真库在TD安装路径内拷贝库文件,并把.v文件与tb文件拷贝到同一目录下

第二步、打开modelsim软件 为TD新建一个库,首先新建一个库包

然后把TD库放进去

新建仿真工程,建立相对应芯片的仿真库,并添加设计和仿真文件

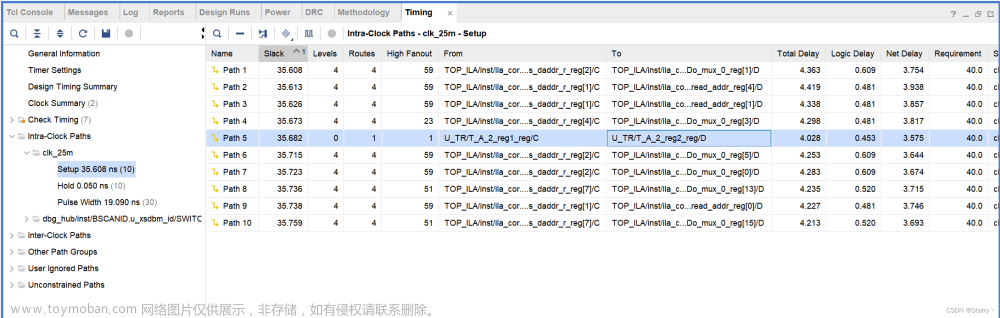

点击仿真,这里要把仿真文件与tb文件都要存放进去,双击报错信息可以看到具体哪行错误

文章来源:https://www.toymoban.com/news/detail-465925.html

最终完成仿真 文章来源地址https://www.toymoban.com/news/detail-465925.html

到了这里,关于【安路FPGA】FPGA开发日记(一)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!