以太网接口技术

概述

-

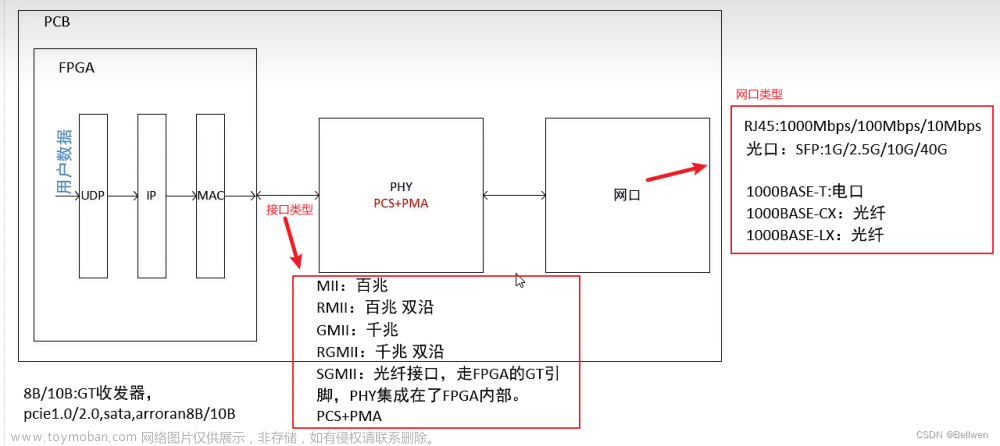

以太的接口技术有很多,按照其在标准模型中所在位置,可以简单地分成两种:

-

MAC接口:MAC接口用于连接PHY芯片或者和MAC直连,常用的有:MII、SMII、GMII、RGMII、SGMII、QSGMII、XGMII、XAUI、XLAUI等等。

-

MDI接口:MDI接口是介质相关接口,常用于连接PHY芯片和外部介质,常用的有MDIX、SFI、XFI等。

-

MII(Media Independent Interface)

参考标准

-

《IEEE Std 802.3 - 2002》

接口概述

-

MII接口由两个独立的数据通道、各个数据通道的控制/状态/时钟信号以及MII管理接口信号组成。

-

MII接口在MAC和PHY之间提供一条百兆位速率的通路。

-

支持10Mbos和100Mbps速率的数据传输以及其管理功能。

-

提供独立的4位宽数据收发通道。

-

数据和控制信号需要时钟同步。

-

提供一个简单管理接口。

-

使用TTL信号电平,兼容通用的数字CMOSASIC处理。

-

使用屏蔽线缆可提供有限长度的驱动能力。

-

提供全双工操作。

-

-

接口信号

-

MII为点对点连接,加上MDC/MDIO管理信号,共有18根引脚。

-

-

信号速率与带宽

-

100Mbps模式下MII接口时钟频率为25MHz;数据通路为4路并行通路,且MIi接口上传送的信号不需要经过编码,故信号带宽最高为25 * 4 = 100Mbps。

-

10Mbps模式下MII接口时钟频率为2.5MHz;数据通路为4路并行通路,且MII接口上传送的信号不需经过编码,所以信号带宽最高2.5 * 4 = 10Mbps。

-

-

应用环境

-

MII接口互连:允许MAC间通过MII接口互连通信。

-

10/100Mbps自适应收发器模块:实现不同媒介百兆PHY同百兆MAC之间的连接,MII可支持板上连接或线缆连接。

-

SMII(Serial Media Independent Interface)

参考标准

-

Cisco Systerms,Inc Serial-MII Specification Revision 2.1 February 9,2000

接口概述

-

SMII是简化MII接口的设计,SMII接口仅使用一个发送数据线和一个接收数据线来传送MII接口的所有数据和控制信息,大大简化了接口设计,SMII接口具有一下特点:

-

允许多个端口共用一个系统参考时钟;

-

允许全双工和半双工;

-

支持10/100Mbps数据传输;

-

允许MAC与MAC之间的相互通讯;

-

接口信号

-

支持SMII接口的每个端口均有两组信号组成,一组全局同步信号和一组125MHz的参考时钟。所有的信号均与时钟同步。

-

SMII接口共有4根引脚,引脚定义如下:

-

RX:from PHY to MAC for Receive Data and Control

-

TX:from MAC to PHY for Transmit Data and Control

-

SYNC:from MAC to PHY for Synchronization

-

CLOCK:from System to MAC&PHY for Synchronization

-

-

MAC和PHY端均需要提供参考时钟。

信号速率和带宽

-

SMII接口工作频率最高为125MHz,数据通路为1位并行通路,由于SMII接口上传送的信号包含控制与状态信息,故信号带宽最高为125 * 1 * 80% = 100Mbps。

-

SMII接口可以向下兼容,SMII接口支持100Mbps和10Mbps的带宽。

编码方式以及对应的传输帧格式

-

接收路径:接收数据域控制信号的相关信息在RX数据线上传输。在100Mbps速率下,RX数据线上每串行传输10位数据称为一个segment,每传输一个segment代表传输了一个字节数据。在10Mbps速率下,每个segment会重复传输10次,每传输10个segment代表传输了1个字节的数据。MAC端可以采样10个segment中的任意一个。segment之间的分界依靠SYNC信号,即SYNC信号每隔10个Clock就产生一个脉冲。RX数据线上传输的控制信息与标准MII接口相同。RXD7-0可以传输数据,RX_ER以及PHY的状态信息。

-

发送路径:发送数据域控制信号的相关信息在TX数据线上传输,其传输机制与RX相同。

-

冲突检测机制:当CRS位与TX_EN位同时有效时,意味着冲突的出现,在这种情况下,PHY应该能保证在冲突出现时,其发送路径应不受影响。

应用环境

-

SMII接口互连:允许MAC间通过SMII接口互连通信。

-

10/100Mbps自适应收发器模块:实现不同媒介百兆PHY同百兆MAC之间的连接。

GMII(Gigabit Media Independent Interface)

参考标准

-

《IEEE Std 802.3 -2002》

接口描述

-

GMII接口是一个工作在125Mhz时钟下的8/10比特宽的数据总线接口。GMII由两个独立的数据通道、接收和发送各个数据通道的控制信号、网络状态信号、各个数据通路的时钟信号以及管理接口信号组成。在GMII中有一个在1000Mb/s速度工作时使用的独立时钟信号,协调子层接口使各种更高速度的PHY可以连接到千兆位MAC引擎上。

-

GMII(千兆媒质无关接口)接口是在MII接口的基础上发展而来。提供了一种简单,可以容易实现互联且成本低的千兆接口,在MAC和PHY之间提供一条千兆位速率的通路。

-

工作能力达到1000Mb/s。

-

独立的8位数据收发通道。

-

数据需要时钟同步。

-

提供一个简单管理接口。

-

支持通用的CMOS接口和部分双极性期间接口。

-

提供全双工操作,不支持半双工。

-

提供向下兼容,兼容MII接口和TBI接口。

-

兼容10M以及100M传输速率。

-

接口信号

-

GMII接口为点对点连接,信号线有GTXCLK、RXCLK、TXD[0:7]、RXD[0:7]、TXER、TXEN、COL、RXER、RXDV、CRS,一共24根信号线。

-

其中COL和CRS信号和时钟无关,其余信号是时钟同步信号。

-

GMII规范规定,GMII接口同MII接口以及TBI接口共享信号线,信号对应方式如下:

GMII MII TBI TX_ER TX_ER TX<9> TX_EN TX_EN TX<8> TXD<7> - TX<7> TXD<6> - TX<6> TXD<5> - TX<5> TXD<4> - TX<4> TXD<3> TXD<3> TX<3> TXD<2> TXD<2> TX<2> TXD<1> TXD<1> TX<1> TXD<0> TXD<0> TX<0> COL COL - RX_ER RX_ER RX<9> RX_DV RX_DV RX<8> RXD<7> - RX<7> RXD<6> - RX<6> RXD<5> - RX<5> RXD<4> - RX<4> RXD<3> RXD<3> RX<3> RXD<2> RXD<2> RX<2> RXD<1> RXD<1> RX<1> RXD<0> RXD<0> RX<0> CRS CRS -

GTXCLK:1000Mbs transmit clk,为TXD[0:7]、TXER、TXEN信号提供参考时钟,由MAC的Recinciliation sublayer层给出信号,PHY在GTXCLK的上升沿采样。时钟频率为125MHz。

-

RXCLK:1000Mbs receive clk,为RXD[0:7]、RXER、RXDV信号提供参考时钟,由PHY发出信号,由MAC的Reconciliation Sublayer层在RXCLK的上升沿采样。

-

TXEN:Transmit enable,TXEN和TXER是一起作用表述数据已经由Reconciliation sublayer层放到GMII接口数据线上,同前导码的第一个字节同时有效,并且保持到所有的传送数据都已经放到GMII接口。TXEN信号由MAC的Reconciliation sublayer层提供,与GTXCLK保持同步。

-

TXER:Transmit code error,TXER有效代表在此段时间内在TXD信号线上传输的数据信号是无效的。TXER信号是由MAC的Reconciliation sublayer层提供,与GTXCLK保持同步。

-

TXD:Transmit data,发送数据,8位数据宽度,由MAC的Reconciliation sublayer提供,与GTXCLK保持同步。当TXEN和TXER都无效的情况下,TXD上信号是无效的。

-

RXDV:receive data vaild,接收数据有效,由PHY驱动,与RXCLK保持同步,表示已经把经过恢复和解码好的信号放在数据线上,此信号必须限于帧开始界定符(SFD)有效,在帧结束界定符(EFD)后无效。

-

RXER:receive error,RXER有效且在RXDV有效的情况下,通知MAC的Reconciliation Sublayer在当前已经发送的RXD信号线上的信号存在错误。RXER由PHY驱动,与RXCLK保持同步。

-

RXD:Receive data,接收数据,8位数据宽度,由PHY提供,与RXCLK保持同步。

-

CRS:Carrier Sense,由PHY提供,不需要同GTXCLK或RXCLK同步。在用在中继器时,PHY在接收媒介非空闲状态下驱动CRS有限,在接收媒介空闲状态下,使CRS信号处于无效。当用在非中继器模式下,PHY工作在半双工模式下时,当接收或发送媒质中任意一个处于空闲模式下时由PHY驱动CRS有效,在接收和发送媒质都处于空闲模式时,使CRS信号处于无效。

-

COL:Collision detected,冲突检测。由PHY驱动,不需要同GTXCLK或RTXCLK同步,当检测到媒质上有冲突的时候驱动有效,并且保持到冲突结束。在全双工模式COL信号没有意义。

-

信号速率以带宽

-

GMII接口工作频率最高为125MHz,数据通路为8位并行通路,且GMII接口上传送的信号不需要经过编码,故信号带宽最高为125 * 8 = 1000Mbps。

-

由于GMII接口要向下兼容,故GMII接口必须支持1000M、100M、10M的工作带宽。在不同的工作带宽下,接口信号的工作频率为:

| 工作带宽 | 时钟频率 | 数据位宽 | 使用的信号线 |

|---|---|---|---|

| 1000M | 125MHZ | 8bit | TXD[7:0],RXD[7:0] |

| 100M | 25MHz | 4bit | TXD[3:0],RXD[3:0] |

| 10M | 2.5MHz | 4bit | TXD[3:0],RXD[3:0] |

信号编码方式

-

GMII接口是基于MII接口的,在数据传输中不对数据进行编码,TXD、RXD数据线直接传送原始数据。控制信息由TXEN、TXER、RXDV、RXER、COL、CRS信号传送。

-

GMII传送帧格式为:

<inter-frame> <preamble> <sfd> <data> <efd> <extend>

-

GMII

GMII传送帧格式

-

GMII接口发送和接收数据位都是8位宽度,故一个时钟周期可以传输和接收一个字节的数据。

应用环境

-

实现不同媒质千兆PHY同千兆MAC之间的连接,GMII仅支持板上连接,可以通过PCB板在有限的距离内实现连接,不支持使用电缆连接。

RGMII(Reduced Gigabit Media independent interface)

参考标准

-

Reduced Gigabit Media Independent Interface,HP Company,V2.0 2002.4.1

接口概述

-

RGMII接口提供了MAC与PHY之间的一种连接选择。只需要12根信号线就可以完成GMII接口所能完成的功能。为了达到减少管脚的目的,其数据以控制信号的时钟参考沿改变为DDR的形式。

接口信号

-

RGMII接口共12根信号线,发送时钟数据信号线1根,发送数据信号线4根,发送控制信号线1根,接收时钟数据信号线1根,接收时钟信号线4根,接收控制信号线1根。

| 信号名 | 信号流向 | 信号描述 |

|---|---|---|

| TXC | from MAC to PHY | 发送时钟信号。速率为1000M时,频率为125MHz;速率为100M时,频率为25MHz;速率为10M时,频率为2.5MHz。 |

| TD[3:0] | from MAC to PHY | 发送数据信号,在时钟上升沿时为bit[3:0],时钟下降沿时为bit[7:4] |

| TX_CTL | from MAC to PHY | 发送控制信号,在时钟上升沿时为TXEN,时钟下降沿为TXERR。 |

| RXC | from PHY to MAC | 接收时钟信号。速率为1000M时,时钟频率为125MHz;速率为100M时,速率为25MHz;速率为10M时,速率为2.5MHz。 |

| RD[3:0] | from PHY to MAC | 接收数据信号,在时钟上升沿时为bit[3:0],时钟下降沿时为bit[7:4] |

| RX_CTL | from PHY to MAC | 接收控制信号,在时钟上升沿时为RXDV,时钟下降沿为RXERR。 |

-

CLK延时:对于RGMII接口,在信号的发送端,时钟和数据是同时变化,但是在数据的接收端,数据在时钟的上升或下降沿采样,故要求在PCB布线时,CLK信号要比数据信号多引入大于1.5ns,小于2ns的时延。

速率信号与带宽

-

当RGMII接口工作于千兆模式时,RGMII接口的时钟信号为125MHz,由于采用DDR的接口形式,故数据速率将乘以2。由于有4根数据线,故单向的数据带宽为1000M。当工作于全双工模式时,双向带宽为2000M。

-

RGMII同时也支持百兆和十兆速率,此时的时钟频率分别为25MHz和2.5MHz。在百兆速率情况下,速率是千兆的十分之一,但时钟是千兆的五分之一,当时钟处于下降沿时,数据会进行一次复制,相当于一个时钟周期还是只传输一次数据,故最终速率还是百兆。百兆速率同百兆也采用这个的方式。

编码方式及对应传输帧格式

-

RGMII接口的编码形式同GMII接口。不同点主要在于:

-

RGMII采用双沿采样,在上升沿时,传送的数据为bit[3:0],在下降沿时,传送的数据为bit[7:4]。

-

发送控制信号在上升沿时代表的含义为TXEN,在下降沿时代表的数据为TXERR;接收控制信号在上升沿时代表的含义为RXDV,在下降沿时代表的含义为RXERR。

-

-

为了简化对PHY端的LINK、双工和速率的检测,RGMII允许在PHY通过RXD[7:0]传递inter-frame给MAC端,MAC端通过inter-frame内容可以获取PHY的LINK、双工、速率信息。inter-frame是内部的控制管理帧,仅在RX_CTL为0的情况下生效。该功能在RGMII规范中是可选的,需要MAC端和PHY端都支持该功能。由于是非强制标准,为了避免兼容性问题出现,实际开发过程中一般都会选择直接从PHY端寄存器获取LINK、速率和双工信息。

应用环境

-

RGMII接口应用于千兆MAC和千兆PHY之间的连接。

XAUI(10 Gigabit Attachment Unit Interface)

参考标准

-

《IEEE Std 802.3 ae-2002》

接口概述

-

XAUI接口的形成基于XGMII(10 Gigabit Media Interface)接口,即将32位并行数据转换为4对Serdes通道的8位数据(8根数据线转换为一组serdes)。由于XGMII接口信号线太多,不利于PCB走线,因此很多支持10Gbps数据传输的MAC芯片和PHY芯片之间接口选择采用XAUI接口。XAUI仅支持全双工操作。

信号数量

-

XAUI接口是递增幅AC耦合差分接口。AC耦合允许互连器件之间采用不同的供电电压。低振幅差分信号可达到抑制噪声与改善EMI(电磁干扰)的效果。

-

XAUI接口为点对点连接,由8对差分信号组成,其中4对发送,4对接收。

-

SLn<P/N>为发送信号(MAC->PHY);DLn<P/N>为接收信号(PHY->MAC);n = 0,1,2,3

-

XAUI接口不提供单独的时钟信号,驱动器通过采用8/10bit编码方式把时钟信号嵌入到数据流中,接收器需从数据流中提取这个时钟信号进行数据同步。所以,支持XAUI接口的MAC芯片一般要求提供一对差分时钟信号作为参考时钟。

信号速率与带宽

-

XAUI接口支持4通道,每个通道信号速率为3.125 Gbps +- 100ppm。

-

带宽为3.125 x 4 = 12.5Gbps,但由于XAUI接口采用8/10B编码,即传输一个字节需要占用10位,因此纯数据带宽占用率为80%,即12.5 x 80% = 10Gbps。

编码方式

-

XAUI接口基于XGMII接口,将32位并行数据转换为4通道的8位数据。XAUI接口与XGMII接口均采用8B/10B编码方式,IEEE 802.3ae-2002针对XGMII接口对8B/10B的编码原理介绍。

-

8/10B编码将8位并行数据转换为直流均衡(dc balanced)的10位串行数据流,从而有效减少信号的衰弱。直流均衡就是将数据流中1与0的个数相等,其最大的运转周期为5。当10为编码中1与0个数不相等时,其偏差将在下一个10位编码中补齐,以保证整个数据流的直流均衡。这也是为何某些8位并行数据对应2个10位串行编码的原因。

-

XGMII传输帧格式如下。

<inter-frame> <preamble> <sfd> <data> <efd>

应用环境

-

背板级连接:用于高带宽要求的插卡式串行背板交换架构中,使用中需要使用连接器连接。

-

万兆光模块应用:对于超短距离应用,XAUI可以直接驱动并行光模块。对于需要单光纤连接,可以采用波分复用模块实现。对于较长举例应用,需要物理媒质福建和物理编码内层来处理数据,并将数据打包放到SONET帧中。

SerDes(SERializer/DESerializer)

接口概述

-

Serdes是serialiseriali/deserializer(串行器/解串器)的简称,是一种时分多路复用(TMD)、点对点的通讯技术,即将发送端的多路低速平行讯号转换成高速串列讯号,最后在接收端将高速串行信号转换为低速平行讯号。这种点对点的串列通讯技术充分利用传输媒体的讯息通道容量,减少所需的传输信息通道和元件接脚数目,因而大幅降低通讯成本。随着对流量需求的不断成长,传统平行界面成为传输速率的瓶颈,串行通讯拘束serdes正取代平行信号成为主流。

-

基于serdes的高速串列界面采用一下措施突破了传统平行界面的数据传输瓶颈:

-

采用差分信号传输代替单端讯号传输,因而增强了抗噪音、抗干扰能力。

-

采用时钟和数据恢复技术代替同时传输数据和时钟,因而解决了限制数据传输速率的讯号时钟偏移的问题。

-

信号数量

-

serdes接口由两对差分信号线组成,一对发送一对接收。

信号电平

-

LVDS和CML是Serdes接口最常用的两种差分信号电平标准。

信号速率与带宽

-

serdes通讯速率一般可以设置为1.0~3.125Gbps之间,用户可通过选择serdes通道组数及通道数据速率来获取不通的带宽需求。如四通道的serdes单元,可以在每个方向以高达12.5Gbps的速度传输,或者获得最高25Gbps的全双工带宽。

编码方式及对应传输帧格式

-

目前常用的serdes接口采用8/10B编码方式。

应用环境

-

XAUI接口由4组通讯速率为3.125Gbps的serdes接口组成,SFP接口由1组通讯速率为1.25Gbps的serdes接口组成。

SGMII(Serial Gigabit Media Independent Interface)

参考标准

-

Cisco Systerms,Inc Serial-GMII Specification。Revision 1.7,2001.7.19

接口概述

-

SGMII接口的含义为串行的GMII接口。

接口信号

-

SGMII接口包含两对差分数据信号,1对发送,1对接收;以及两对差分时钟信号,一对发送,一对接收。若数据数据接收端的器件自身可以从数据流中恢复出时钟,则其数据的参考时钟可以不使用。大部分产品中使用SGMII接口的器件均可以从数据中恢复出时钟。

信号速率与带宽

-

SGMII接口使用8B/10B编码形式,将控制信号嵌入数据信号中,所以其数据线上的速率由1G上升为1.25G。SGMII接口的带宽为单向1G,全双工2G。

编码方式及对应传输帧格式

-

SGMII接口使用1000BASE-X编码方式来传送数据和控制信号。

-

8B/10B编码的重要在于,其数据码流中包含了足够的电平转变,使得从数据流中恢复时钟成为了可能。8B/10B这种编的数据若出现了单位或多位错误,在接收端有可能直接被检测出来。

-

SGMII接口的MAC侧通过检测数据流中的控制代码来恢复出GMII接口规范中定义的控制信号。如检测S及T码字来恢复出RX_DV信号,通过检测V码字来恢复出RX_ER信号。

-

SGMII接口需要通过1000BASE-X的自动协商功能使得MAC和PHY之间建立起稳定的连接关系。SGMII的自动协商与802.3的clause 37中定义的1000BASE-X自动协商的方法相同。但SGMII接口的自动协商的内容和1000BASE-X中的自动协商的编码内容有所不同。

-

PHY将tx_config_reg[15:0]的内容通过自动协商的方式通知MAC;MAC在获得了PHY的连接状况后,将tx_config_reg[15:0]中的bit14置为1,发送给PHY,表明已经更新了连接的状态。

-

自动协商中的link_timer的数值从10ms修改1.6ms。当介质接口的连接状态改变时,SGMII的自动协商功能也要重新启动,以更新连接的速率和双工信息。

应用环境

-

SGMII接口应用与需要千兆连接而对信号线的数目有限制的场景。由于SGMII接口的编码形式和Serdes(fiber)接口相同,而信号电平类似。所以很多芯片的SGMII接口和Serdes接口使用相同的管脚,方便了面向不同应用形式。

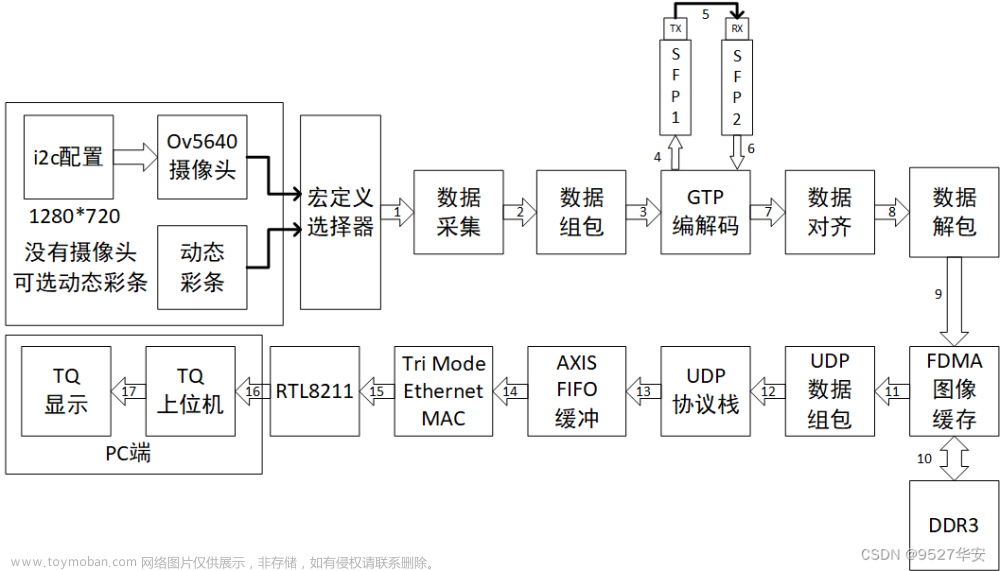

SFP(Small From-factor Pluggable)

参考标准

-

SFP MSA

接口概述

-

SFP MSA规范定义的SFP接口主要针对千兆速率数据通讯如光纤通道和千兆以太网应用(gigabit rate datacom applications such as fiber channel and gigabit etherent),由于其较GBIC接口体积小的优势,大大减小了硬件布板面积,从而提高端口密度。SFP光模块采用LC接头;GBIC光模块采用SC接头,LC接头的截面只有SC接头的一半。SFP MSA规范指出可根据SFP模块的颜色来区分其支持的光纤模式,黑色或褐色为多模,蓝色为单模。

接口信号

-

SFP接口共有20根引脚。

信号速率与带宽

-

SFP接口仅支持单通道,其信号速率为1.25Gbps。

编码方式以及对应的传输帧格式

-

采用8B/10B编码方式。文章来源:https://www.toymoban.com/news/detail-466024.html

应用环境

-

主要针对千兆速率数据通讯,如光纤通道和千兆以太网应用。文章来源地址https://www.toymoban.com/news/detail-466024.html

SPF+(Small From-factor Pluggable Plus)

到了这里,关于以太网接口总线类型笔记的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!