一、原因

由于项目需要,整个工程需要在100kHz的时钟下运行,FPGA的clk:50MHz

二、方案分析

采用IP核得到分频时钟

clocking wizard

问题:MMCM和PLL都不能实现分频到100KHz这么低的频率

MMCM最小频率4.687MHz

PLL最小频率6.25MHz

自己写一个简单的分频模块

分频模块如下:

module divi_fre #(parameter DIVNUM=500,parameter WIDTH=9)(

input clk,

input rst_n,

output reg divi_clk

);

reg [WIDTH-1:0] counter;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

counter <= 'd0;

end

else begin

counter <= counter + 1'b1;

if(counter==DIVNUM/2-1)

counter <= 'd0;

end

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

divi_clk <= 1'b0;

end

else begin

if(counter == DIVNUM/2-1)begin

divi_clk <= ~divi_clk;

end

end

end

endmodule问题:自己写的分频模块直接使用是不可以的,需要在约束文件中进行时序约束

自写分频模块时钟时序约束

(1)打开implemented Design

查看分频模块的原理图

找到输出divi_clk

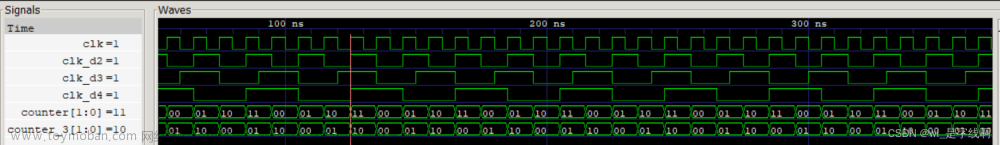

可以看到divi_clk_reg寄存器的C端口连接的是输入CLK(50MHz),Q端口连接的是divi_clk(100KHz)

(2)约束文件编写

create_clock -period 20.000 -name clk1 [get_ports clk]

create_generated_clock -name clk2 -source [get_pins u_divi_fre/divi_clk_reg/C] -divide_by 500 [get_pins u_divi_fre/divi_clk_reg/Q]clk1对应50MHz

20ns--->50MHz, get_ports对应clk

注:clk1和clk2只是随意取的名字,没有影响

clk2对应100kHz

-divide_by后跟的是计算得到的分频值,50_000_000/100_000=500

-source后跟输入时钟,上面说到了divi_clk_reg寄存器的C端口连接的是输入CLK,注意这个定位到寄存器的时序约束需要从顶层一层一层传下来到管脚

[get_pins u_divi_fre/divi_clk_reg/Q]就输出的divi_clk了文章来源:https://www.toymoban.com/news/detail-469743.html

其实应该直接get_ports到clk和divi也是可以的,但是因为我当时没这么写,后面改改文章来源地址https://www.toymoban.com/news/detail-469743.html

到了这里,关于Vivado自写分频模块的分频时钟的约束条件编写的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!