-

第1关:MIPS指令译码器设计

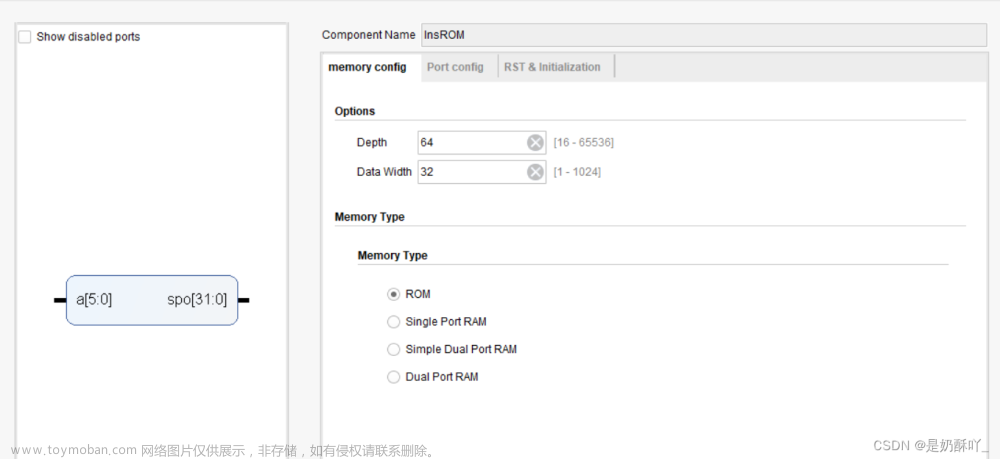

利用比较器等功能模块将32位MIPS 指令字译码生成LW、SW、BEQ、SLT、ADDI、OtherInstr信号也就是利用比较器将指令字转换为译码信号,OP与不同信号对应(查询MIPS手册得知) 16 进制 :23 是 2进制: 00100011 ,把获得的OP,Func,和常数比对,相同输出1.

,把获得的OP,Func,和常数比对,相同输出1.

第2关:变长指令周期---时序发生器FSM设计

按照题目要求填写表格,使用logisim的组合逻辑电路分析功能,当然也可以直接再logisim中写真值表。单总线采用变长指令周期,不同指令周期数不同,节拍数可变化。

写的excel表格

最终生成电路

(当然 需要先把生成的公式填入logisim中)

(当然 需要先把生成的公式填入logisim中)

3. 第3关:变长指令周期---时序发生器输出函数设计

和第二关没有区别根据题目要求填写表格,然后生成表达式输入logisim完事。

-

第4关:硬布线控制器组合逻辑单元

(第四关可没少耽误时间。。)

和第二关和第三关超不多,但是这一关需要使用表达式进行logisim得组合逻辑电路分析,表达式依旧通过excel生成,

根据分析

得出公式

(不完整),输入到logisim中输出电路

-

第5关:变长指令周期---硬布线控制器设计

所给的硬布线控制器电路中时序发生器状态机和输出函数默认是定长指令周期的,所以我们需要更换我们前几关设计的变长指令系统 的输出函数,变长指令系统的输入需要加上译码信号。其实根据题目要求给出的图连接即可。

-

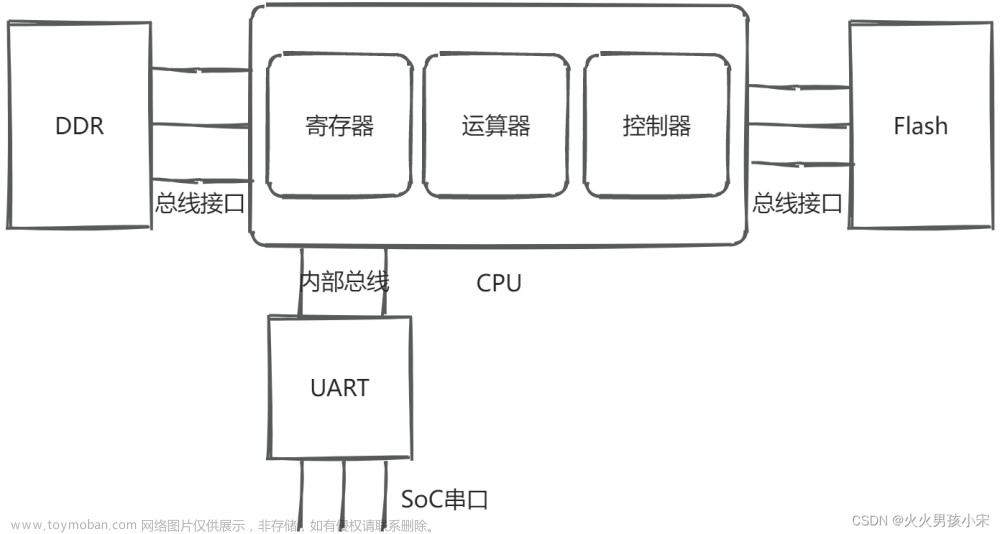

第6关:变长指令周期---单总线CPU设计

首先在RAM中加载sort-5.hex程序(加载数据镜像),ctrl+k自动运行,程序应该运行至0x81d节拍停下,指令计数为251,注意最后一条指令是一条beq分支指令,会跳回当前指令继续执行,是死循环。(最主要的是前面第四关的硬布线控制器设计成功 这一关问题不大)调节频率加快执行速度。

文章来源:https://www.toymoban.com/news/detail-470294.html

文章来源:https://www.toymoban.com/news/detail-470294.html

如果需要 circ文件 请访问 ➡ 单总线CPU设计(变长指令周期3级时序)(HUST)(circ文件)-单片机文档类资源-CSDN文库文章来源地址https://www.toymoban.com/news/detail-470294.html

到了这里,关于单总线CPU设计(变长指令周期3级时序)(HUST)(头歌实验)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!