1、实验目的

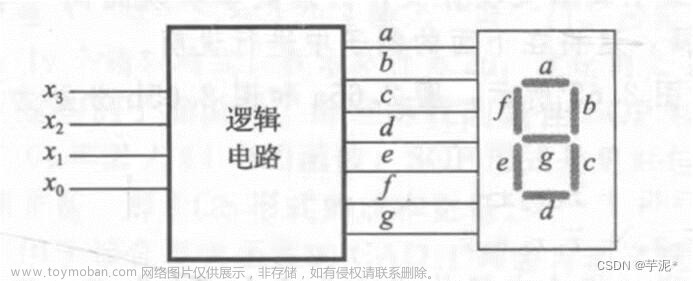

掌握七数码管显示原理

掌握七段码显示译码设计

进一步熟悉 Xilinx ISE 环境及 SWORD 实验平台

2、实验内容

任务 1:原理图设计实现显示译码 MyMC14495 模块

任务 2:用 MyMC14495 模块实现数码管显示

3、实验过程

任务 1:原理图设计实现显示译码 MyMC14495 模块

1.创建工程并绘制原理图

建立工程 MyMC14495,创建原理图文件 MyMC14495,按原理图绘制

2.原理图仿真

建立基准测试波形文件 MyMC14495,输入仿真激励信号,在 Process 窗口中选择 Simulate Behavioral Model,可以得到仿真波 形图

选择 Create Schematic Symbol,生成符号逻辑图

任务 2:用 MyMC14495 模块实现数码管显示

1.创建工程并绘制原理图

建立工程 DispNumber_sch,创建原理图文件 DispNumber_sch,将 MyMC14495.sym 和 MyMC14495.sch 复制到工程目录下,按原理图绘制。

2.为模块的端口指定引脚分配

建立引脚约束文件 K7.ucf,输入代码,为原理图的每个输入输出 端口分配引脚。

3.生成 bit 文件并下载到开发板

最左边的两个按钮依次是 point 和 LE。从右边第一个开始向左, 依次是输入第一位,输入第二位,输入第三位,输入第四位,右边第 一个 LED 开关,右边第二个 LED 开关,左边第二个 LED 开关,最左边 LED 开关。以下按照从最左边 LED 开关开始,从左向右的顺序,如: 1111 0001 表示 4 盏灯都亮,显示数字为 1。至于 point 和 LE 单独说明。 以下是实验结果:

4、实验结果

这里需要说明译码不是转换。译码:十进制的13对应的BCD码是0001 0011,而转换:十进制的10对应二进制的1010

七段译码管是将要显示的数字翻译成七个数码管显示的开关命令。比如C,用共阳控制,就是a,d,e,f 为 0,其余为 1,所有对应的abcdefg就是0110001,对应的十六进制数字就是31,也就是说译码器将C翻译成了31(这个最后的实验会用到)文章来源:https://www.toymoban.com/news/detail-471292.html

这里有一个for循环需要说明,其中{D3,D2,D1,D0}=i 这一行,可以看到i是从0到15依次增加的,这里直接赋值就可以了……(当时卡了好一会)文章来源地址https://www.toymoban.com/news/detail-471292.html

到了这里,关于6、七段数码管显示译码器设计与应用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!