一、设计目的

1、熟悉MAX+PLUSⅡ、QUARTUSⅡ软件的使用;

2、熟悉EDA/SOPC、FPGA基本结构;

3、熟悉EDA开发的基本流程。

二、设计原理

所谓表决器就是对于一件事,由多个人投票,如果同意的票数过半,就认为此事可行;否则如果否决的票数过半,则认为此事不行。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。实验中用7个按键来表示七个人,当对应的按键按下时,输入为“1”,表示此人同意;否则若按键输入为‘0’,则表示此人反对。表决的结果用一个LED表示,若表决的结果为同意,则输出‘0’,LED被点亮;否则,如果表决的结果为反对,则输出‘1’,LED不会被点亮。

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为逻辑“0”时,表示表决者“不赞同”。输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;否则为“0”。

三、设计内容

本实验利用EDA/SOPC实验箱中的按键开关模块和LED模块来实现一个简单的七人表决器功能。按键F1~F7表示七个人,当按键按下输入为‘1’时,表示对应的人投同意票,否则当按键输入为‘0’时,表示对应的人投反对票;LED模块中led0表示七人表决的结果,当led0点亮时,表示一致同意,否则当led0熄灭时,表示一致反对。按键F1~F7以及led0与FPGA的引脚连接如下表所示。

| 芯片引脚 |

开发平台模块 |

| AC10 |

LED0 |

| Y11 |

F1 |

| AA10 |

F2 |

| AB10 |

F3 |

| AE6 |

F4 |

| V22 |

F5 |

| AF23 |

F6 |

| AE23 |

F7 |

四、设计结果

1、七人表决器源程序:

module VOTER7(a,b,c,d,e,f,g,pass);

input a,b,c,d,e,f,g;

output pass;

reg pass;

reg[3:0] count;

initial count=0;

always@(a,b,c,d,e,f,g)

begin

count=a+b+c+d+e+f+g;

pass=count<4?0:1;//当人数在三人以下是输出1

end

endmodule2、仿真波形图:

上图为四人赞同时的表决结果,pass=1,表示通过。

上图为三人赞同时的表决结果,pass=0,表示不通过。

3、管脚约束:

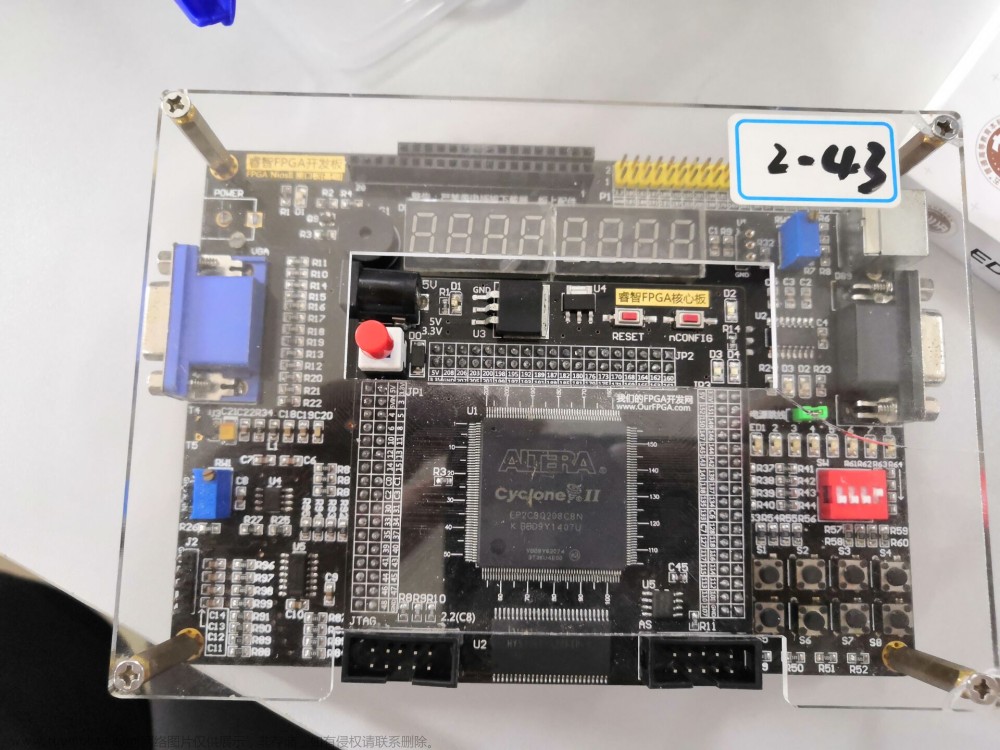

4、下载到试验箱上的结果:

五、注意文章来源:https://www.toymoban.com/news/detail-474421.html

在Verilog开发时出现了module命名与.v文件命名不一样会导致编译报错。文章来源地址https://www.toymoban.com/news/detail-474421.html

到了这里,关于FPGA设计开发(基础课题):七人表决器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[ZYNQ]开发之MATALB与FPGA联合仿真平台设计](https://imgs.yssmx.com/Uploads/2024/02/765704-1.png)