FPGA时序分析中的建立时间与保持时间

概述

总体从时序分析的概念,时序分析模型来分析建立时间与保持时间裕量,通过建立保持时间公式定性分析。

1、时序分析概念

通过分析FPGA设计中各个寄存器之间的数据延时和时钟传输路径的时钟延时的关系,来确保所有寄存器都能正确的寄存数据。

2、时序分析

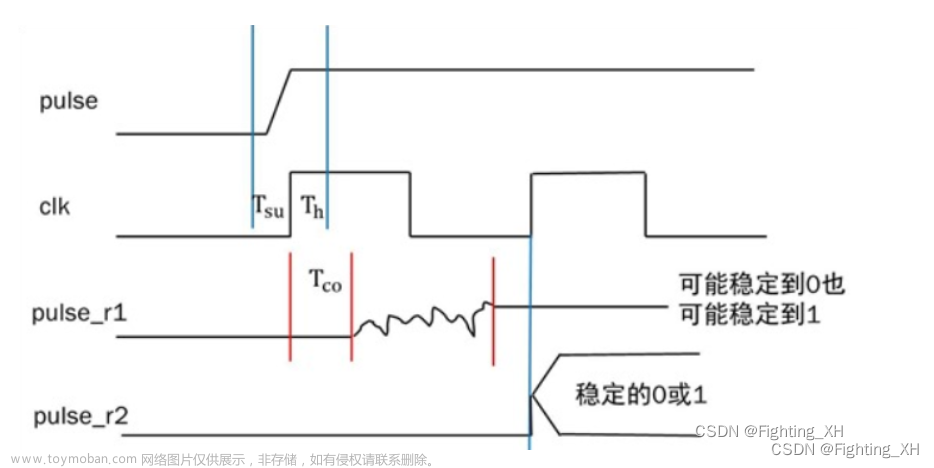

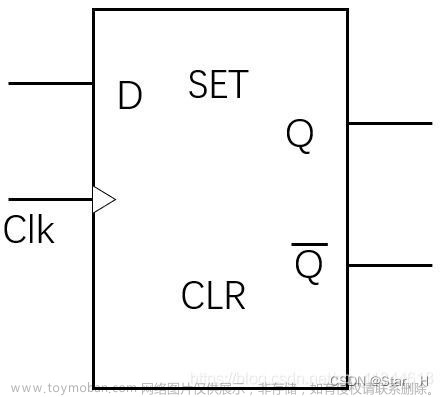

a、寄存器延时Tco:时钟上升沿到达D触发器 到 数据输出Q端的延迟;

b、组合逻辑延时Tdata:组合逻辑进行运算时产生的延时,一般为最长路径延时;

c、时钟延时Tclk_delay:从时钟IO口(时钟源),到寄存器的时钟端口延时;

e、时钟偏移Tskew (clock skew):指时钟信号到达数字电路各部分所用时间的差异;

f、建立时间Tsu:触发器的时钟上升沿来之前,输入端的数据必须保持不变的最小时间;

g、保持时间Th:触发器的时钟上升沿来之后,输入端的数据必须保持不变的最小时间;

如果数据在建立保持时间内发生跳变,系统就会产生亚稳态输出,即输出值在短时间内不确定(1/0/什么也不是)。

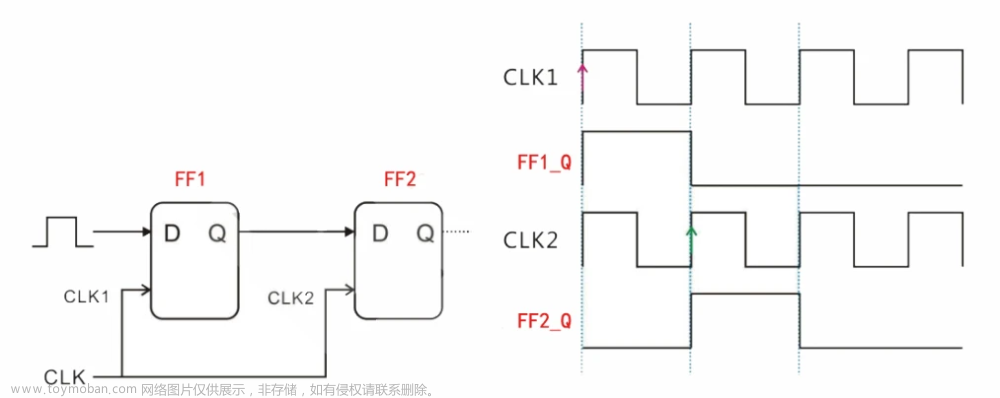

通过上面两幅图图更直观分析(规定一个时钟周期为Tcycle)

clk_in:时钟输入的时钟信号;

Clk_Reg1:clk_in经过Tclk1时间到REG1端的波形;

REG1 Q:数据从REG1的D端到Q端的寄存器延时Tco;

REG2 D:数据从REG1 Q端到REG2 D端中间的延时Tdata;

CLK_Reg2:clk_in经过Tclk2时间到REG2端的波形;

通过第二副图,Tsu Slack为建立时间裕量;Tsu Slack=要求数据到达时间-实际数据到达时间;

实际数据到达时间为:Tclk1+Tco+Tdata;

要求数据到达时间为:Tcycle+Tclk2-Tsu;

而建立时间的约束条件为:数据传输的时间要小于时钟到达的时间,即要求数据到达时间为-实际数据到达时间为>=0;

Tsu Slack = Tcycle + Tclk2 - Tsu - (Tclk1 + Tco + Tdata)=Tcycle + Tskew-Tsu-Tdata-Tco>=0

如果不满足建立时间,即Tsu Slack<0,则增大时钟周期Tcycle或减小Tdata寄存器之间组合逻辑延时

计算FPGA时钟允许的最大时钟频率或最小时钟周期,建立时间裕量必须为0

通过公式推导:Tcycle +Tskew >= Tsu+Tdata+Tco;Tcycle>= Tsu+Tdata+Tco-Tskew 。

最小时钟周期=Tsu+Tdata+Tco-Tskew

最快时钟频率=1/最小时钟周期=1/(Tsu+Tdata+Tco-Tskew)。

通过上面一幅图,先定义Th Slack为保持时间裕量,Th Slack = 实际数据结束时间-要求数据结束时间;

实际数据结束时间:Tclk1 + Tco +Tdata +Tcycle

要求数据结束时间:Tcycle + Tclk2 +Th

保持时间的约束条件是前一级的数据延时时间大于触发器的保持时间,即实际数据结束时间>要求数据结束时间

Told Slack = Tcycle + Tclk1 + Tco + Tdata - (Tcycle + Tclk2 + Th),从式中看保持时间裕量与时钟周期Tcycle无关,所以时钟频率也与保持时间裕量无关。

总结

把建立时间与保持时间式子拿出来一起分析(Tskew = T2-T1):

建立时间:Tcycle +Tskew-Tdata-Tco >= Tsu

保持时间:Tco+Tdata -Tskew >Th

从上面式子分析,数据跑的越快(Tdata,寄存器间组合逻辑延时越小),时钟传输延时越大(Tskew越大)对建立时间满足越有利,而对保持时间越不利;时钟周期越小越容易发生建立时间违例。在设计中,通常只关心建立时间是否满足要求,因为这关系到系统的最快时钟频率能否跑到预定的工作频率,而时钟通常走的是专门的快速路线,很难出现时钟传输延时过大问题,一般不会出现保持时间。

建立时间违例解决办法:

1、降低时钟频率,即增大时钟周期。

2、再时钟路径上加缓冲器(buffer),让时钟晚到来。

3、更换具有更小器件延迟的触发器。

4、组合逻辑优化或插入流水线,缩短关键路径。文章来源:https://www.toymoban.com/news/detail-474695.html

保持时间解决办法:

1、在数据路径上插 buffer。

2、更换具有更大器件延迟的触发器。

3、优化时钟路径,让时钟更早到来。文章来源地址https://www.toymoban.com/news/detail-474695.html

到了这里,关于FPGA时序分析中的建立时间与保持时间(看完就懂)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!