第5章 新型嵌入式存储器

在现有主流嵌入式存储器中,SRAM虽然读写速度非常快,但是单元面积太大,无法在片上实现高密度集成;DRAM由于要制造电容,所采用的工艺无法在先进的CMOS工艺中实现,不利于做嵌入式存储,虽然基于增益单元的eDRAM能够完全采用标准CMOS工艺,但是仍然需要刷新,而且集成密度也不够高;Flash由于采用浮栅和高压操作,也不利于其在先进工艺集成。因此,目前集成电路发展亟须出现一种高密度、与CMOS工艺兼容性强、非易失的嵌入式存储器方案,而新型存储器的发展带来了希望。

5.1 新型存储器原理介绍

5.1.1 ReRAM

阻变存储器(ReRAM),又称忆阻器,作为除电阻、电容和电感之外的“第四种无源器件”。ReRAM具有非易失、单元结构简单(两端器件)、微缩性好和与标准CMOS工艺兼容性好等优点,因此,ReRAM有望分别取代NOR Flash和NAND Flash实现高密度片上存储和分立式存储。

典型的ReRAM器件器件采用MIM的结构,上、下电极都是金属,中间为阻变材料层,如图5-1所示。

图片来源于《嵌入式存储器架构、电路与应用》

ReRAM的阻变特性主要体现在其电压-电流曲线上,典型的单极型ReRAM阻态转变的I-V曲线如图5-2(a)所示,阻态转变并不依赖施加电压的极性。双极型ReRAM阻变器件的I-V曲线如图5-2(b)所示。

图片来源于《嵌入式存储器架构、电路与应用》

5.1.2 PRAM

相变随机存储器(PRAM),又称PCM或PcRAM,是采用相变材料的存储器件。相变材料具有晶态和非晶态两个不同状态,不同的晶态表现出不同的电阻,其中晶态为低阻,非晶态为高阻。一般定义高阻为逻辑“0”,低阻为“1”。在不同的温度条件下,相变材料的非晶态和晶态之间可以发生转换,如图5-3所示。

图5-4给出了PRAM单元处于晶态和非晶态的I-V特性曲线,可分为三个区间:读(READ)、置位(SET)和复位(RESET)。

图片来源于《嵌入式存储器架构、电路与应用》

PRAM的最大挑战是需要很高的编程电流密度,一般需要采用双极型晶体管或二极管来作为选通器件,而如果采用NMOS晶体管作为选通管的话,单元面积就比较大,导致存储密度较小。另外,PRAM单元的电阻和编程电压会随时间漂移,耐久性较差。

5.1.3 MRAM

磁阻式随机访问存储器(MRAM)是指以磁电阻性质来存储数据的随机存储器,采用磁化的方向不同所导致的磁电阻不同来记录0和1,只要外部磁场不改变,磁化的方向就不会变化。

MRAM最新的编程机理STT。单元结构如图5-5所示,选用NMOS晶体管作为选通管。

图片来源于《嵌入式存储器架构、电路与应用》

5.1.4 FeRAM

铁电随机访问存储器(FeRAM)利用铁电材料的铁电效应实现数据存储。FeRAM主要有三种结构,分别是1T1C(一个晶体管一个铁电电容)、1T(一个铁电晶体管)和1T1R(一个晶体管一个铁电隧穿结电阻),如图5-6所示。

图片来源于《嵌入式存储器架构、电路与应用》

5.2 选通器件及阵列设计

5.2.1 场效应晶体管(NMOS或PMOS)选通器件

从广义上讲,MRAM、FeRAM和PRAM都属于阻变型存储器,操作方式也类似,只是阻变的机理不同。

典型的1T1R单元如图5-7所示,存储器件R的下电极与NMOS选通管T的漏端相连,连接存储器件R上电极的是位线(BL),连接NMOS栅极的是字线(WL),连接存储器件源端的是源线(SL)。

图5-8给出了一个1T1R单元结构的截面图,其中阻变器件R集成在漏端的接触底部。

图片来源于《嵌入式存储器架构、电路与应用》

阻变器件也可以集成在后段金属层之间的通孔上,如图5-9所示。

图5-10给出了两种常见的1T1R存储阵列,分别面向单极型阻变器件和双极型阻变器件。

图片来源于《嵌入式存储器架构、电路与应用》

表5-1给出了单极型和双极型1T1R单元结构的存储阵列的操作电压表。

图片来源于《嵌入式存储器架构、电路与应用》

1T1R存储单元构成的阵列结构也有其他的形式,比如列方向的源线跟位线一样连接在一起,而字线和位线与前面介绍的连接方式一样,如图5-11所示。

图片来源于《嵌入式存储器架构、电路与应用》

5.2.2 双极型晶体管选通器件

对于PRAM和ReRAM,写操作过程需要有较大的电流流经存储单元。但是,NMOS主要通过少子来产生漏电流,导致电流驱动能力不足。为此,采用具有更大电流驱动能力的双极型晶体管(BJT)作为选通器件,成为提高存储密度的重要途径。

图5-12给出了采用BJT作为选通器件的PRAM单元。

图5-13给出了采用竖直方向寄生的BJT作为选通器件的ReRAM单元。

图片来源于《嵌入式存储器架构、电路与应用》

5.2.3 二极管或非线性选通器件

作为选通器件,二极管相比BJT的面积更小,但是不足之处在于,二极管仅适用PRAM或单极型的阻变器件。为了克服该不足,可以采用非线性器件(S)或者RRAM本身包含的非线性效应,比如双向二极管。

图5-14给出了采用二极管作为选通器件的PRAM单元,即1D1R,其中Diode通过选择性外延生长(SEG)工艺来实现。

图片来源于《嵌入式存储器架构、电路与应用》

采用二极管作为选通器件的1D1R单元的阵列采用交叉阵列架构,如图5-16所示。

图片来源于《嵌入式存储器架构、电路与应用》

阵列的操作电压如表5-2所示。

图片来源于《嵌入式存储器架构、电路与应用》

图5-17给出了采用非线性器件作为选通器件的1S1R存储单元的I-V特性曲线。

图片来源于《嵌入式存储器架构、电路与应用》

采用非线性器件作为选通器件的阻变单元的阵列也采用交叉阵列架构,如图5-18所示。

图片来源于《嵌入式存储器架构、电路与应用》

阵列的操作电压分别如表5-3和表5-4所示。

图片来源于《嵌入式存储器架构、电路与应用》

5.3 新型嵌入式存储器的电路技术

5.3.1 提高读写速度及带宽的电路技术

对于新型存储器,数据的读出速度受限于很多因素,包括阻变器件的阻值、一条位线上连接的单元数目、灵敏放大器的结构以及读参考的选取。

新型存储器带宽的提升除了依赖读写速度的改善,也可通过增加读写资源来实现。

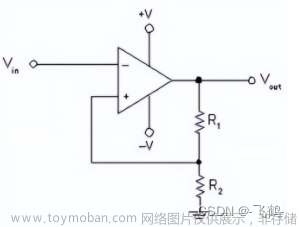

1 基于反馈调节位线偏压的电流型灵敏放大电路

基于反馈调节的位线偏压方法来减小调节时间,从而提高读速度。基于反馈调节的位线偏压方案的读电路如图5-19所示,该图的底部是1T1R单元阵列,其包含128根位线和2根参考位线。

图片来源于《嵌入式存储器架构、电路与应用》

2 源线预充电的电流型灵敏放大电路

台积电公司提出一种源线预充电电流型灵敏放大方案,来应对CSL读取时电容的增加。读出方案如图5-21(a)所示,图中仅显示了两个列作为示例,其位线分别被表示为BL0和BL1,CSL是它们的共同源线。此读出电路的组成包括读SA、偏压产生器(BG)、BL/SL预充电器(PC)和均衡器(E)。源线预充电的电流型灵敏放大电路及工作时序如图5-21(b)。

图片来源于《嵌入式存储器架构、电路与应用》

3 电荷转移型灵敏放大器

日本日立公司提出电荷转移直接检测的方法,在保持高速读取的同时有较低的读取功耗。如图5-22所示,电荷转移型灵敏放大器的直接前置放大器由三对MOS晶体管组成。

图片来源于《嵌入式存储器架构、电路与应用》

4 快速验证实现高速写入的电路技术

阻变型存储器与浮栅型的Flash相似,写操作往往需要验证来确认是否写成功。进行一次验证,相当于做了一次读操作,因此,编程验证(PV)是一个制约写入速度的因素。由于读操作过程中检测电流通常较小,常规编程验证执行速度往往比较缓慢,写入过程中需要较长时间进行编程验证。为克服此问题,索尼公司提出了在编程中直接检测(DSIP)的技术以实现快速验证,提高写入速度。

图5-24为DSIP方案的实现电路,包括写入驱动器、参考单元和灵敏放大器。图5-25显示了与传统验证方案相比的DSIP操作的仿真波形。

图片来源于《嵌入式存储器架构、电路与应用》

5 实时监测快速关断的写电路技术

DSIP方案可减少编程验证时间,但仍需要一定的验证时间。同样为解决编程验证影响写入速度的问题,复旦大学提出一种无需验证的非对称写入方法,称为快速步降置位/步升复位(FS-DSUR),无需专门设置验证过程以实现高速写入的同时还能提升可靠性。

FS-DSUR的写电路实现如图5-26所示。

图片来源于《嵌入式存储器架构、电路与应用》

6 增加读写资源以实现高带宽

在嵌入式应用中,存储器读写无需经过片外走线,读写带宽受限于片上的读写电路数量以及读写访问时间。因此,为了提高带宽,在读写速度已经足够优化的条件下,增加片上读写电路的数量往往是最直接有效的途径,但也会带来瞬时功耗过大,导致电源电压的大幅振荡,影响读写良率。如图5-28所示,通过增加读写资源以提高带宽的4Mb RRAM架构。

图片来源于《嵌入式存储器架构、电路与应用》

5.3.2 提高读良率的电路技术

读良率依赖读参考的选取和灵敏放大器的设计。

1 简单动态参考

摩托罗拉公司的Nahas提出了动态参考电流技术,使参考电流同样随温度变化,以降低读失败的概率。简单动态参考电流电路如图5-29所示,参考电流被选取为低阻态单元和高阻态电流的平均值。

图片来源于《嵌入式存储器架构、电路与应用》

2 并串参考单元方案

为克服参考单元的电阻随温度变化问题,台湾工业技术研究院提出了并串参考单元(PSRC)技术,使参考电流分布更小。图5-31为PSRC方案的示意图,其中每个PSRC单元都是由p个串联连接的子参考模块(SRBs)组成,每个SRB又由q个并联连接的参考单元组成。

图片来源于《嵌入式存储器架构、电路与应用》

3 自适应读取模式

在高温下,RRAM电阻变化很大,尤其是其高阻态的电阻分布将严重向低阻方向延伸,导致RRAM的电阻窗口变小,引发高温下读取失败的问题。为了克服此问题,复旦大学提出了自适应读取模式(SARM),采用两个虚拟行(DR)产生动态的读参考电压而不使用参考阵列,在高温时也能保持足够的检测容限。

图5-32给出了SARM方案所采用的阵列架构,其由258行与256列相交而成。

图片来源于《嵌入式存储器架构、电路与应用》

4 与被读数据相关的读参考方案

随着尺寸微缩,RRAM的单元电阻更高,写入时间和电阻的变化更大,导致高低阻态电阻比变小。较高的低阻态电阻还会导致RRAM上压降更大,降低写入电压和单元开关尺寸。这些现象最终减小了RRAM的检测容限,限制了最小读取VDD,延长了读取访问时间。为克服此问题,清华大学提出使用摆动采样和耦合电压型灵敏放大器(SSC-VSA)来保证低电压下的读取可靠性。

图5-34给出了SSC-VSA的电路图,包括一个带有额外PMOS晶体管T1的传统差分输入电压型SA,两个开关SW1、SW2和一个耦合电容C1。

图片来源于《嵌入式存储器架构、电路与应用》

图5-35给出了采用依赖数据的动态读参考电流的读取电路。读出放大器(SA)包括两级放大器、输出锁存器、预充电晶体管、钳位晶体管和读使能晶体管。

图片来源于《嵌入式存储器架构、电路与应用》

5 热感应位线偏压方案

图5-36给出了热感应位线偏压(TABB)方案的实现电路和波形图。TABB的实现电路包括VBE跟踪电路(BETU)和对温度敏感的电压钳位电路(TABC)。

图片来源于《嵌入式存储器架构、电路与应用》

6 体漏驱动电流灵敏放大器方案

台湾清华大学提出一种体漏驱动电流灵敏放大器(BDD-CSA)方案,消除位线钳位电路的过驱动电压BLC对VHR的影响,从而实现在更低电源电压下保持较高的读良率。

图5-38给出了BDD-CSA的电路,包括一对体漏连接的PMOS晶体管(BDP,M1/M2)和第二级电压比较器。

图片来源于《嵌入式存储器架构、电路与应用》

7 连续记录增强电压型灵敏放大器

台湾清华大学提出一种连续记录增强电压型灵敏放大器(CRE-VSA),可以容忍较小的隧道磁阻比并在低BL读取电压下实现快速读取,同时降低读取功耗。

CRE-VSA的电路图如图5-40所示,分三个阶段运行。

图片来源于《嵌入式存储器架构、电路与应用》

5.3.3 提高写良率及可靠性的电路技术

1 自适应写模式

传统的置位和复位算法分别是单电压脉冲(SVP)和“写入-验证-写入”的斜坡脉冲序列(RPS)。自适应写入模式(SAWM)可以检测单元电阻是否在置位/复位期间切换并立即关闭写入激励,因而能缩短快速单元在置位期间切换到大电流的持续时间,同时节省了置位功耗,并避免由写入干扰引起的复位失败。

图5-42给出了SAWM的写通路,其中包括判决模块、写偏压模块、SAWM模块、极性选择器、列选择器和RRAM存储阵列。

图片来源于《嵌入式存储器架构、电路与应用》

2 自升压写入终止

自升压写入终止(SBWT)使用4个晶体管,图5-44给出了SBWT写入驱动器(WD)的电路图,包括2T(P1和N1)偏压发生器VBG,置位驱动器NSD和复位驱动器NRSD。

图片来源于《嵌入式存储器架构、电路与应用》

3 低电压写电流限制方案

阻变器件在发生置位时,当达到目标电平后立刻断开单元电流,可防止被置位的单元承受干扰电压,但突然断开电流可能使RRAM单元材料中无法形成足够稳定的导电细丝,从而影响数据保留时间。为克服此问题,台积电提出了低电压写电流限制方案(LV-WCLS)。图5-45给出了LV-WCLS方案的电路图。

图片来源于《嵌入式存储器架构、电路与应用》

4 两步导电细丝形成方案

ReRAM数据存储在阻变单元的导电细丝中,因此导电细丝的一致性和尺寸是其可靠性的关键因素,在写入操作期间,应严格控制其氧迁移。为保持RRAM中导电细丝的一致性,日本松下公司提出一种两步Forming电路,以实现稳定的写入控制。图5-47给出了两步Forming的V-R曲线,其中第一步采用Forming1电压VFH,第二步采用Forming2电压VFL。

图片来源于《嵌入式存储器架构、电路与应用》

图5-48给出了两步Forming的实现电路和时序图。第一步Forming电路包含反馈控制,其作用是在位线上施加VFH电压。第二步Forming施加VFL给源线,同时具有限流功能。

图片来源于《嵌入式存储器架构、电路与应用》

5 阻值验证写方案

除了两步Forming方案外,日本松下公司还同时提出了阻值验证写方案,可以恢复存储单元的中间态(IM),提高RRAM阵列中电阻单元的阻值稳定性。如图5-49所示,阻值验证写方案的实现电路包括比较器和写脉冲产生器。

图片来源于《嵌入式存储器架构、电路与应用》

5.4 新型存储器的应用实例

5.4.1 ReRAM应用实例

MN101LR是一组8位的低功耗微控制器系列,主要用于靠电池供电的设备,包括移动设备、安全设备等,如图5-50所示。

图片来源于《嵌入式存储器架构、电路与应用》

MB85AS4MT的主要参数如表5-5所示。

图片来源于《嵌入式存储器架构、电路与应用》

5.4.2 PRAM应用实例

最初,PRAM是主要作为Flash的替代技术而受到关注,因为PRAM可以直接改写,无需块擦除。但是NAND Flash的存储密度发展太快,特别是3D堆叠技术的出现,导致高密度存储应用短时间内仍然是NAND的市场。

如图5-52所示,采用3D Xpoint的Optane存储卡,Optane也可以代替NAND作为SSD的存储介质使用,虽然成本比较高。

图片来源于《嵌入式存储器架构、电路与应用》

5.4.3 MRAM应用实例

如图5-53所示,三星的eMRAM采用后端工艺制作MRAM存储单元,仅需增加三层掩膜版,可以支持bulk(体硅)、FinFET和FD-SOI制造工艺。

图片来源于《嵌入式存储器架构、电路与应用》

5.4.4 FeRAM应用实例

相比MRAM,FeRAM的应用更加小众,因为铁电电容的微缩性能太差,导致存储容量很小,而且制造成本高。FeRAM存储器具有低功耗、快速写和很高的读写耐久性。

5.5 新型嵌入式存储器在计算方面的应用

5.5.1 存储计算

存储计算往往需要修改存储阵列和外围电路及其工作方式,进而同时可以选中两行或更多行进行读操作,通过对电流和的判断并配合相应的外围电路实现一定的逻辑运算。图5-55给出了所采用的存储计算阵列结构。在进行存储计算时,一般同时选中两行,然后进行读操作,那么同一位线流过的电流可能是两个低阻态的读出电流之和、两个高阻态的读出电流之和或者一个高阻态和一个低阻态的读出电流之和。选择合适的参考电流,即可判断位线读出电流所在的区域,通过灵敏放大器读出即可实现相应的逻辑操作。

图片来源于《嵌入式存储器架构、电路与应用》

如图5-56所示,“与”操作。

图片来源于《嵌入式存储器架构、电路与应用》

如图5-57所示,“或”操作。

图片来源于《嵌入式存储器架构、电路与应用》

如图5-58所示,“异或”操作。

图片来源于《嵌入式存储器架构、电路与应用》

5.5.2 机器学习加速

机器学习主要的运算形式是乘加计算(MAC),能够实现高能效的MAC是实现机器学习加速的关键。目前机器学习加速采用的硬件主要有CPU、GPU或ASIC,无论何种硬件,所需要的权值或输入数据都需要从片外载入,带来较大的功耗。

采用存储计算实现机器学习加速与上述实现逻辑运算的原理相似,都是同时选中多行进行读操作,然后将流经同一位线的电流与多个读参考比较,然后确定输出。图5-59给出了台湾清华大学2018年所采用的阵列架构。

图片来源于《嵌入式存储器架构、电路与应用》

致谢《嵌入式存储器架构、电路与应用》

希望本文对大家有帮助,上文若有不妥之处,欢迎指正文章来源:https://www.toymoban.com/news/detail-475125.html

分享决定高度,学习拉开差距文章来源地址https://www.toymoban.com/news/detail-475125.html

到了这里,关于《嵌入式存储器架构、电路与应用》----学习记录(四)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!