开发环境

- KEIL:MDK_ARM_5.27

- MCU:STM32F429IGT6

- PHY_IC:LAN8720A

- LWIP:LWIP2.1.2

- STM32CUBEMX:6.6.1

- HAL:V1.27.1

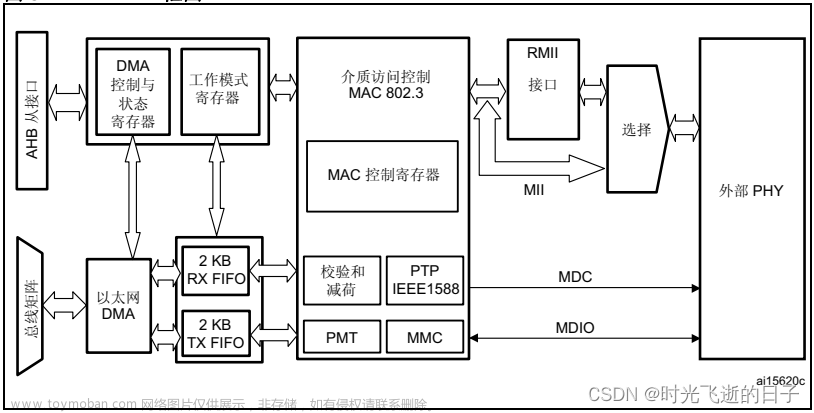

LAN8720A使用RMII接口与STM32的ETH外设进行数据通信

STM32使用SMI接口读/写LAN8720A的寄存器

硬件原理图

LAN8720A由外部25MHz晶振提供时钟,LED2/NINTSEL引脚配置为下拉,故PHY(LAN8720A)提供50MHz时钟给RMII的NINT/REFCLKO(此时引脚NINT/REFCLKO仅作为时钟输出,中断功能不可用),RMII需要50MHz时钟

LED1/REGOFF配置为下拉,使用LAN8720A内部稳压器

上电后MODE引脚的电平会被锁存,用于设置PHY的工作模式,后续也可以写寄存器来修改HPY工作模式,也可以设置PHY为自适应模式,自动适配最佳模式,然后通过读寄存器来获取PHY的工作模式,无非就是速率与双工。

上电复位后,RXER/PHYAD0,引脚的电平被锁存在一个内部寄存器中;

可以使用硬件配置将设备的 SMI 地址配置为值 0 或 1,不接的话认为为0。

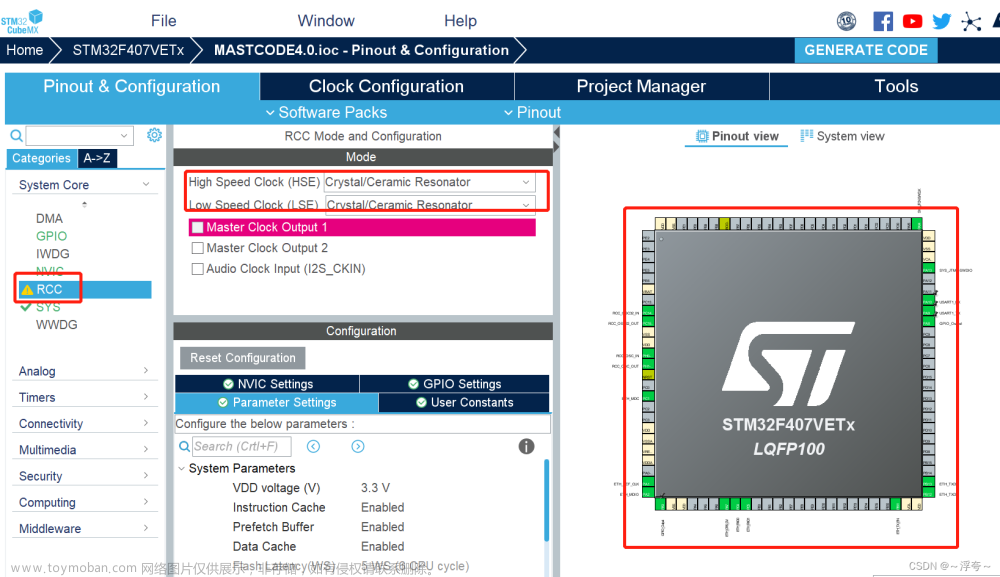

CUBEMX配置

基本的时钟、调试下载、Systick 不过多介绍

PHY引脚配置

设置MAC地址、接收缓冲区的大小、数据接收模式

设置PHY的类型为LAN8742A

(最好根据LAN8742A来设置自己使用的PHY,否则CUBEMX不会生成void HAL_ETH_MspInit(ETH_HandleTypeDef* ethHandle)GPIO、DMA、NVIC等初始化函数)

这些生成的宏均在路径Core\Inc\stm32f4xx_hal_conf.h下,大家可以去看看

生成的void HAL_ETH_MspInit(ETH_HandleTypeDef* ethHandle)在工程文件夹LWIP\Target\ethernetif.c下

在生成的HAL_ETH_MspInit()函数中添加PHY上电复位代码(其实也可以不用添加,HAL库生成会通过写BCR寄存器RESET位来实现软件复位,然后读取RESET位来确认是否PHY已经复位完毕)

HAL库生成的HAL_ETH_MspInit()如下:

/**

* @brief Initializes the ETH MSP.

* @param ethHandle: ETH handle

* @retval None

*/

void HAL_ETH_MspInit(ETH_HandleTypeDef* ethHandle)

{

GPIO_InitTypeDef GPIO_InitStruct = {0};

if(ethHandle->Instance==ETH)

{

/* USER CODE BEGIN ETH_MspInit 0 */

/* USER CODE END ETH_MspInit 0 */

/* Enable Peripheral clock */

__HAL_RCC_ETH_CLK_ENABLE();

__HAL_RCC_GPIOC_CLK_ENABLE();

__HAL_RCC_GPIOA_CLK_ENABLE();

__HAL_RCC_GPIOB_CLK_ENABLE();

__HAL_RCC_GPIOG_CLK_ENABLE();

/**ETH GPIO Configuration

PC1 ------> ETH_MDC

PA1 ------> ETH_REF_CLK

PA2 ------> ETH_MDIO

PA7 ------> ETH_CRS_DV

PC4 ------> ETH_RXD0

PC5 ------> ETH_RXD1

PB11 ------> ETH_TX_EN

PG13 ------> ETH_TXD0

PG14 ------> ETH_TXD1

*/

GPIO_InitStruct.Pin = GPIO_PIN_1|GPIO_PIN_4|GPIO_PIN_5;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF11_ETH;

HAL_GPIO_Init(GPIOC, &GPIO_InitStruct);

GPIO_InitStruct.Pin = GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_7;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF11_ETH;

HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

GPIO_InitStruct.Pin = GPIO_PIN_11;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF11_ETH;

HAL_GPIO_Init(GPIOB, &GPIO_InitStruct);

GPIO_InitStruct.Pin = GPIO_PIN_13|GPIO_PIN_14;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF11_ETH;

HAL_GPIO_Init(GPIOG, &GPIO_InitStruct);

/* USER CODE BEGIN ETH_MspInit 1 */

/* 手动添加 PHY 需要的复位延时代码 */

HAL_GPIO_WritePin(LAN8720A_RESET_GPIO_Port, LAN8720A_RESET_Pin, GPIO_PIN_RESET);

HAL_Delay(60);

HAL_GPIO_WritePin(LAN8720A_RESET_GPIO_Port, LAN8720A_RESET_Pin, GPIO_PIN_SET);

HAL_Delay(60);

/* USER CODE END ETH_MspInit 1 */

}

}

void HAL_ETH_MspDeInit(ETH_HandleTypeDef* ethHandle)

{

if(ethHandle->Instance==ETH)

{

/* USER CODE BEGIN ETH_MspDeInit 0 */

/* USER CODE END ETH_MspDeInit 0 */

/* Peripheral clock disable */

__HAL_RCC_ETH_CLK_DISABLE();

/**ETH GPIO Configuration

PC1 ------> ETH_MDC

PA1 ------> ETH_REF_CLK

PA2 ------> ETH_MDIO

PA7 ------> ETH_CRS_DV

PC4 ------> ETH_RXD0

PC5 ------> ETH_RXD1

PB11 ------> ETH_TX_EN

PG13 ------> ETH_TXD0

PG14 ------> ETH_TXD1

*/

HAL_GPIO_DeInit(GPIOC, GPIO_PIN_1|GPIO_PIN_4|GPIO_PIN_5);

HAL_GPIO_DeInit(GPIOA, GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_7);

HAL_GPIO_DeInit(GPIOB, GPIO_PIN_11);

HAL_GPIO_DeInit(GPIOG, GPIO_PIN_13|GPIO_PIN_14);

/* USER CODE BEGIN ETH_MspDeInit 1 */

/* USER CODE END ETH_MspDeInit 1 */

}

}

设置PHY寄存器及相应掩码

打开 Drivers\BSP\Components\lan8742\lan8742.h 对照LAN8720A的BCR寄存器修改相应位的掩码

/**

******************************************************************************

* @file lan8742.h

* @author MCD Application Team

* @brief This file contains all the functions prototypes for the

* lan8742.c PHY driver.

******************************************************************************

* @attention

*

* <h2><center>© Copyright (c) 2017 STMicroelectronics.

* All rights reserved.</center></h2>

*

* This software component is licensed by ST under BSD 3-Clause license,

* the "License"; You may not use this file except in compliance with the

* License. You may obtain a copy of the License at:

* opensource.org/licenses/BSD-3-Clause

*

******************************************************************************

*/

/* Define to prevent recursive inclusion -------------------------------------*/

#ifndef LAN8742_H

#define LAN8742_H

#ifdef __cplusplus

extern "C" {

#endif

/* Includes ------------------------------------------------------------------*/

#include <stdint.h>

/** @addtogroup BSP

* @{

*/

/** @addtogroup Component

* @{

*/

/** @defgroup LAN8742

* @{

*/

/* Exported constants --------------------------------------------------------*/

/** @defgroup LAN8742_Exported_Constants LAN8742 Exported Constants

* @{

*/

/** @defgroup LAN8742_Registers_Mapping LAN8742 Registers Mapping

* @{

*/

#define LAN8742_BCR ((uint16_t)0x0000U)

#define LAN8742_BSR ((uint16_t)0x0001U)

#define LAN8742_PHYI1R ((uint16_t)0x0002U)

#define LAN8742_PHYI2R ((uint16_t)0x0003U)

#define LAN8742_ANAR ((uint16_t)0x0004U)

#define LAN8742_ANLPAR ((uint16_t)0x0005U)

#define LAN8742_ANER ((uint16_t)0x0006U)

#define LAN8742_ANNPTR ((uint16_t)0x0007U)

#define LAN8742_ANNPRR ((uint16_t)0x0008U)

#define LAN8742_MMDACR ((uint16_t)0x000DU)

#define LAN8742_MMDAADR ((uint16_t)0x000EU)

#define LAN8742_ENCTR ((uint16_t)0x0010U)

#define LAN8742_MCSR ((uint16_t)0x0011U)

#define LAN8742_SMR ((uint16_t)0x0012U)

#define LAN8742_TPDCR ((uint16_t)0x0018U)

#define LAN8742_TCSR ((uint16_t)0x0019U)

#define LAN8742_SECR ((uint16_t)0x001AU)

#define LAN8742_SCSIR ((uint16_t)0x001BU)

#define LAN8742_CLR ((uint16_t)0x001CU)

#define LAN8742_ISFR ((uint16_t)0x001DU)

#define LAN8742_IMR ((uint16_t)0x001EU)

#define LAN8742_PHYSCSR ((uint16_t)0x001FU)

/**

* @}

*/

/** @defgroup LAN8742_BCR_Bit_Definition LAN8742 BCR Bit Definition

* @{

*/

#define LAN8742_BCR_SOFT_RESET ((uint16_t)0x8000U)

#define LAN8742_BCR_LOOPBACK ((uint16_t)0x4000U)

#define LAN8742_BCR_SPEED_SELECT ((uint16_t)0x2000U)

#define LAN8742_BCR_AUTONEGO_EN ((uint16_t)0x1000U)

#define LAN8742_BCR_POWER_DOWN ((uint16_t)0x0800U)

#define LAN8742_BCR_ISOLATE ((uint16_t)0x0400U)

#define LAN8742_BCR_RESTART_AUTONEGO ((uint16_t)0x0200U)

#define LAN8742_BCR_DUPLEX_MODE ((uint16_t)0x0100U)

/**

* @}

*/

/** @defgroup LAN8742_BSR_Bit_Definition LAN8742 BSR Bit Definition

* @{

*/

#define LAN8742_BSR_100BASE_T4 ((uint16_t)0x8000U)

#define LAN8742_BSR_100BASE_TX_FD ((uint16_t)0x4000U)

#define LAN8742_BSR_100BASE_TX_HD ((uint16_t)0x2000U)

#define LAN8742_BSR_10BASE_T_FD ((uint16_t)0x1000U)

#define LAN8742_BSR_10BASE_T_HD ((uint16_t)0x0800U)

#define LAN8742_BSR_100BASE_T2_FD ((uint16_t)0x0400U)

#define LAN8742_BSR_100BASE_T2_HD ((uint16_t)0x0200U)

#define LAN8742_BSR_EXTENDED_STATUS ((uint16_t)0x0100U)

#define LAN8742_BSR_AUTONEGO_CPLT ((uint16_t)0x0020U)

#define LAN8742_BSR_REMOTE_FAULT ((uint16_t)0x0010U)

#define LAN8742_BSR_AUTONEGO_ABILITY ((uint16_t)0x0008U)

#define LAN8742_BSR_LINK_STATUS ((uint16_t)0x0004U)

#define LAN8742_BSR_JABBER_DETECT ((uint16_t)0x0002U)

#define LAN8742_BSR_EXTENDED_CAP ((uint16_t)0x0001U)

/**

* @}

*/

/** @defgroup LAN8742_PHYI1R_Bit_Definition LAN8742 PHYI1R Bit Definition

* @{

*/

#define LAN8742_PHYI1R_OUI_3_18 ((uint16_t)0xFFFFU)

/**

* @}

*/

/** @defgroup LAN8742_PHYI2R_Bit_Definition LAN8742 PHYI2R Bit Definition

* @{

*/

#define LAN8742_PHYI2R_OUI_19_24 ((uint16_t)0xFC00U)

#define LAN8742_PHYI2R_MODEL_NBR ((uint16_t)0x03F0U)

#define LAN8742_PHYI2R_REVISION_NBR ((uint16_t)0x000FU)

/**

* @}

*/

/** @defgroup LAN8742_ANAR_Bit_Definition LAN8742 ANAR Bit Definition

* @{

*/

#define LAN8742_ANAR_NEXT_PAGE ((uint16_t)0x8000U)

#define LAN8742_ANAR_REMOTE_FAULT ((uint16_t)0x2000U)

#define LAN8742_ANAR_PAUSE_OPERATION ((uint16_t)0x0C00U)

#define LAN8742_ANAR_PO_NOPAUSE ((uint16_t)0x0000U)

#define LAN8742_ANAR_PO_SYMMETRIC_PAUSE ((uint16_t)0x0400U)

#define LAN8742_ANAR_PO_ASYMMETRIC_PAUSE ((uint16_t)0x0800U)

#define LAN8742_ANAR_PO_ADVERTISE_SUPPORT ((uint16_t)0x0C00U)

#define LAN8742_ANAR_100BASE_TX_FD ((uint16_t)0x0100U)

#define LAN8742_ANAR_100BASE_TX ((uint16_t)0x0080U)

#define LAN8742_ANAR_10BASE_T_FD ((uint16_t)0x0040U)

#define LAN8742_ANAR_10BASE_T ((uint16_t)0x0020U)

#define LAN8742_ANAR_SELECTOR_FIELD ((uint16_t)0x000FU)

/**

* @}

*/

/** @defgroup LAN8742_ANLPAR_Bit_Definition LAN8742 ANLPAR Bit Definition

* @{

*/

#define LAN8742_ANLPAR_NEXT_PAGE ((uint16_t)0x8000U)

#define LAN8742_ANLPAR_REMOTE_FAULT ((uint16_t)0x2000U)

#define LAN8742_ANLPAR_PAUSE_OPERATION ((uint16_t)0x0C00U)

#define LAN8742_ANLPAR_PO_NOPAUSE ((uint16_t)0x0000U)

#define LAN8742_ANLPAR_PO_SYMMETRIC_PAUSE ((uint16_t)0x0400U)

#define LAN8742_ANLPAR_PO_ASYMMETRIC_PAUSE ((uint16_t)0x0800U)

#define LAN8742_ANLPAR_PO_ADVERTISE_SUPPORT ((uint16_t)0x0C00U)

#define LAN8742_ANLPAR_100BASE_TX_FD ((uint16_t)0x0100U)

#define LAN8742_ANLPAR_100BASE_TX ((uint16_t)0x0080U)

#define LAN8742_ANLPAR_10BASE_T_FD ((uint16_t)0x0040U)

#define LAN8742_ANLPAR_10BASE_T ((uint16_t)0x0020U)

#define LAN8742_ANLPAR_SELECTOR_FIELD ((uint16_t)0x000FU)

/**

* @}

*/

/** @defgroup LAN8742_ANER_Bit_Definition LAN8742 ANER Bit Definition

* @{

*/

#define LAN8742_ANER_RX_NP_LOCATION_ABLE ((uint16_t)0x0040U)

#define LAN8742_ANER_RX_NP_STORAGE_LOCATION ((uint16_t)0x0020U)

#define LAN8742_ANER_PARALLEL_DETECT_FAULT ((uint16_t)0x0010U)

#define LAN8742_ANER_LP_NP_ABLE ((uint16_t)0x0008U)

#define LAN8742_ANER_NP_ABLE ((uint16_t)0x0004U)

#define LAN8742_ANER_PAGE_RECEIVED ((uint16_t)0x0002U)

#define LAN8742_ANER_LP_AUTONEG_ABLE ((uint16_t)0x0001U)

/**

* @}

*/

/** @defgroup LAN8742_ANNPTR_Bit_Definition LAN8742 ANNPTR Bit Definition

* @{

*/

#define LAN8742_ANNPTR_NEXT_PAGE ((uint16_t)0x8000U)

#define LAN8742_ANNPTR_MESSAGE_PAGE ((uint16_t)0x2000U)

#define LAN8742_ANNPTR_ACK2 ((uint16_t)0x1000U)

#define LAN8742_ANNPTR_TOGGLE ((uint16_t)0x0800U)

#define LAN8742_ANNPTR_MESSAGGE_CODE ((uint16_t)0x07FFU)

/**

* @}

*/

/** @defgroup LAN8742_ANNPRR_Bit_Definition LAN8742 ANNPRR Bit Definition

* @{

*/

#define LAN8742_ANNPTR_NEXT_PAGE ((uint16_t)0x8000U)

#define LAN8742_ANNPRR_ACK ((uint16_t)0x4000U)

#define LAN8742_ANNPRR_MESSAGE_PAGE ((uint16_t)0x2000U)

#define LAN8742_ANNPRR_ACK2 ((uint16_t)0x1000U)

#define LAN8742_ANNPRR_TOGGLE ((uint16_t)0x0800U)

#define LAN8742_ANNPRR_MESSAGGE_CODE ((uint16_t)0x07FFU)

/**

* @}

*/

/** @defgroup LAN8742_MMDACR_Bit_Definition LAN8742 MMDACR Bit Definition

* @{

*/

#define LAN8742_MMDACR_MMD_FUNCTION ((uint16_t)0xC000U)

#define LAN8742_MMDACR_MMD_FUNCTION_ADDR ((uint16_t)0x0000U)

#define LAN8742_MMDACR_MMD_FUNCTION_DATA ((uint16_t)0x4000U)

#define LAN8742_MMDACR_MMD_DEV_ADDR ((uint16_t)0x001FU)

/**

* @}

*/

/** @defgroup LAN8742_ENCTR_Bit_Definition LAN8742 ENCTR Bit Definition

* @{

*/

#define LAN8742_ENCTR_TX_ENABLE ((uint16_t)0x8000U)

#define LAN8742_ENCTR_TX_TIMER ((uint16_t)0x6000U)

#define LAN8742_ENCTR_TX_TIMER_1S ((uint16_t)0x0000U)

#define LAN8742_ENCTR_TX_TIMER_768MS ((uint16_t)0x2000U)

#define LAN8742_ENCTR_TX_TIMER_512MS ((uint16_t)0x4000U)

#define LAN8742_ENCTR_TX_TIMER_265MS ((uint16_t)0x6000U)

#define LAN8742_ENCTR_RX_ENABLE ((uint16_t)0x1000U)

#define LAN8742_ENCTR_RX_MAX_INTERVAL ((uint16_t)0x0C00U)

#define LAN8742_ENCTR_RX_MAX_INTERVAL_64MS ((uint16_t)0x0000U)

#define LAN8742_ENCTR_RX_MAX_INTERVAL_256MS ((uint16_t)0x0400U)

#define LAN8742_ENCTR_RX_MAX_INTERVAL_512MS ((uint16_t)0x0800U)

#define LAN8742_ENCTR_RX_MAX_INTERVAL_1S ((uint16_t)0x0C00U)

#define LAN8742_ENCTR_EX_CROSS_OVER ((uint16_t)0x0002U)

#define LAN8742_ENCTR_EX_MANUAL_CROSS_OVER ((uint16_t)0x0001U)

/**

* @}

*/

/** @defgroup LAN8742_MCSR_Bit_Definition LAN8742 MCSR Bit Definition

* @{

*/

#define LAN8742_MCSR_EDPWRDOWN ((uint16_t)0x2000U)

#define LAN8742_MCSR_FARLOOPBACK ((uint16_t)0x0200U)

#define LAN8742_MCSR_ALTINT ((uint16_t)0x0040U)

#define LAN8742_MCSR_ENERGYON ((uint16_t)0x0002U)

/**

* @}

*/

/** @defgroup LAN8742_SMR_Bit_Definition LAN8742 SMR Bit Definition

* @{

*/

#define LAN8742_SMR_MODE ((uint16_t)0x00E0U)

#define LAN8742_SMR_PHY_ADDR ((uint16_t)0x001FU)

/**

* @}

*/

/** @defgroup LAN8742_TPDCR_Bit_Definition LAN8742 TPDCR Bit Definition

* @{

*/

#define LAN8742_TPDCR_DELAY_IN ((uint16_t)0x8000U)

#define LAN8742_TPDCR_LINE_BREAK_COUNTER ((uint16_t)0x7000U)

#define LAN8742_TPDCR_PATTERN_HIGH ((uint16_t)0x0FC0U)

#define LAN8742_TPDCR_PATTERN_LOW ((uint16_t)0x003FU)

/**

* @}

*/

/** @defgroup LAN8742_TCSR_Bit_Definition LAN8742 TCSR Bit Definition

* @{

*/

#define LAN8742_TCSR_TDR_ENABLE ((uint16_t)0x8000U)

#define LAN8742_TCSR_TDR_AD_FILTER_ENABLE ((uint16_t)0x4000U)

#define LAN8742_TCSR_TDR_CH_CABLE_TYPE ((uint16_t)0x0600U)

#define LAN8742_TCSR_TDR_CH_CABLE_DEFAULT ((uint16_t)0x0000U)

#define LAN8742_TCSR_TDR_CH_CABLE_SHORTED ((uint16_t)0x0200U)

#define LAN8742_TCSR_TDR_CH_CABLE_OPEN ((uint16_t)0x0400U)

#define LAN8742_TCSR_TDR_CH_CABLE_MATCH ((uint16_t)0x0600U)

#define LAN8742_TCSR_TDR_CH_STATUS ((uint16_t)0x0100U)

#define LAN8742_TCSR_TDR_CH_LENGTH ((uint16_t)0x00FFU)

/**

* @}

*/

/** @defgroup LAN8742_SCSIR_Bit_Definition LAN8742 SCSIR Bit Definition

* @{

*/

#define LAN8742_SCSIR_AUTO_MDIX_ENABLE ((uint16_t)0x8000U)

#define LAN8742_SCSIR_CHANNEL_SELECT ((uint16_t)0x2000U)

#define LAN8742_SCSIR_SQE_DISABLE ((uint16_t)0x0800U)

#define LAN8742_SCSIR_XPOLALITY ((uint16_t)0x0010U)

/**

* @}

*/

/** @defgroup LAN8742_CLR_Bit_Definition LAN8742 CLR Bit Definition

* @{

*/

#define LAN8742_CLR_CABLE_LENGTH ((uint16_t)0xF000U)

/**

* @}

*/

/** @defgroup LAN8742_IMR_ISFR_Bit_Definition LAN8742 IMR ISFR Bit Definition

* @{

*/

#define LAN8742_INT_8 ((uint16_t)0x0100U)

#define LAN8742_INT_7 ((uint16_t)0x0080U)

#define LAN8742_INT_6 ((uint16_t)0x0040U)

#define LAN8742_INT_5 ((uint16_t)0x0020U)

#define LAN8742_INT_4 ((uint16_t)0x0010U)

#define LAN8742_INT_3 ((uint16_t)0x0008U)

#define LAN8742_INT_2 ((uint16_t)0x0004U)

#define LAN8742_INT_1 ((uint16_t)0x0002U)

/**

* @}

*/

/** @defgroup LAN8742_PHYSCSR_Bit_Definition LAN8742 PHYSCSR Bit Definition

* @{

*/

#define LAN8742_PHYSCSR_AUTONEGO_DONE ((uint16_t)0x1000U)

#define LAN8742_PHYSCSR_HCDSPEEDMASK ((uint16_t)0x001CU)

#define LAN8742_PHYSCSR_10BT_HD ((uint16_t)0x0004U)

#define LAN8742_PHYSCSR_10BT_FD ((uint16_t)0x0014U)

#define LAN8742_PHYSCSR_100BTX_HD ((uint16_t)0x0008U)

#define LAN8742_PHYSCSR_100BTX_FD ((uint16_t)0x0018U)

/**

* @}

*/

/** @defgroup LAN8742_Status LAN8742 Status

* @{

*/

#define LAN8742_STATUS_READ_ERROR ((int32_t)-5)

#define LAN8742_STATUS_WRITE_ERROR ((int32_t)-4)

#define LAN8742_STATUS_ADDRESS_ERROR ((int32_t)-3)

#define LAN8742_STATUS_RESET_TIMEOUT ((int32_t)-2)

#define LAN8742_STATUS_ERROR ((int32_t)-1)

#define LAN8742_STATUS_OK ((int32_t) 0)

#define LAN8742_STATUS_LINK_DOWN ((int32_t) 1)

#define LAN8742_STATUS_100MBITS_FULLDUPLEX ((int32_t) 2)

#define LAN8742_STATUS_100MBITS_HALFDUPLEX ((int32_t) 3)

#define LAN8742_STATUS_10MBITS_FULLDUPLEX ((int32_t) 4)

#define LAN8742_STATUS_10MBITS_HALFDUPLEX ((int32_t) 5)

#define LAN8742_STATUS_AUTONEGO_NOTDONE ((int32_t) 6)

/**

* @}

*/

/** @defgroup LAN8742_IT_Flags LAN8742 IT Flags

* @{

*/

#define LAN8742_WOL_IT LAN8742_INT_8

#define LAN8742_ENERGYON_IT LAN8742_INT_7

#define LAN8742_AUTONEGO_COMPLETE_IT LAN8742_INT_6

#define LAN8742_REMOTE_FAULT_IT LAN8742_INT_5

#define LAN8742_LINK_DOWN_IT LAN8742_INT_4

#define LAN8742_AUTONEGO_LP_ACK_IT LAN8742_INT_3

#define LAN8742_PARALLEL_DETECTION_FAULT_IT LAN8742_INT_2

#define LAN8742_AUTONEGO_PAGE_RECEIVED_IT LAN8742_INT_1

/**

* @}

*/

/**

* @}

*/

/* Exported types ------------------------------------------------------------*/

/** @defgroup LAN8742_Exported_Types LAN8742 Exported Types

* @{

*/

typedef int32_t (*lan8742_Init_Func) (void);

typedef int32_t (*lan8742_DeInit_Func) (void);

typedef int32_t (*lan8742_ReadReg_Func) (uint32_t, uint32_t, uint32_t *);

typedef int32_t (*lan8742_WriteReg_Func) (uint32_t, uint32_t, uint32_t);

typedef int32_t (*lan8742_GetTick_Func) (void);

typedef struct

{

lan8742_Init_Func Init;

lan8742_DeInit_Func DeInit;

lan8742_WriteReg_Func WriteReg;

lan8742_ReadReg_Func ReadReg;

lan8742_GetTick_Func GetTick;

} lan8742_IOCtx_t;

typedef struct

{

uint32_t DevAddr;

uint32_t Is_Initialized;

lan8742_IOCtx_t IO;

void *pData;

}lan8742_Object_t;

/**

* @}

*/

/* Exported macro ------------------------------------------------------------*/

/* Exported functions --------------------------------------------------------*/

/** @defgroup LAN8742_Exported_Functions LAN8742 Exported Functions

* @{

*/

int32_t LAN8742_RegisterBusIO(lan8742_Object_t *pObj, lan8742_IOCtx_t *ioctx);

int32_t LAN8742_Init(lan8742_Object_t *pObj);

int32_t LAN8742_DeInit(lan8742_Object_t *pObj);

int32_t LAN8742_DisablePowerDownMode(lan8742_Object_t *pObj);

int32_t LAN8742_EnablePowerDownMode(lan8742_Object_t *pObj);

int32_t LAN8742_StartAutoNego(lan8742_Object_t *pObj);

int32_t LAN8742_GetLinkState(lan8742_Object_t *pObj);

int32_t LAN8742_SetLinkState(lan8742_Object_t *pObj, uint32_t LinkState);

int32_t LAN8742_EnableLoopbackMode(lan8742_Object_t *pObj);

int32_t LAN8742_DisableLoopbackMode(lan8742_Object_t *pObj);

int32_t LAN8742_EnableIT(lan8742_Object_t *pObj, uint32_t Interrupt);

int32_t LAN8742_DisableIT(lan8742_Object_t *pObj, uint32_t Interrupt);

int32_t LAN8742_ClearIT(lan8742_Object_t *pObj, uint32_t Interrupt);

int32_t LAN8742_GetITStatus(lan8742_Object_t *pObj, uint32_t Interrupt);

/**

* @}

*/

#ifdef __cplusplus

}

#endif

#endif /* LAN8742_H */

/**

* @}

*/

/**

* @}

*/

/**

* @}

*/

/**

* @}

*/

/************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

LAN8720A的BSR寄存器

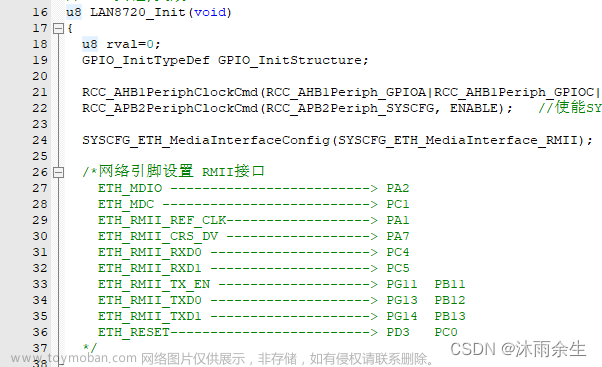

注意GPIO复用

LWIP配置

添加代码

- 复位PHY引脚

本次PI1连接PHY的复位引脚,低电平复位

在生成的void HAL_ETH_MspInit(ETH_HandleTypeDef* ethHandle)在工程文件夹LWIP\Target\ethernetif.c下添加复位PHY代码,具体延时时间根据PHY来设置

- PHY配置

置位LAN8720A的自动协商(自适应、自动适配,速率与双工)并等待配置完毕

在Drivers\BSP\Components\lan8742\lan8742.c的函数LAN8742_Init()

注意:每次配置最好做备份,因为每使用CUBEMX生成工程,用户代码都会被清除

- 主函数中添加

MX_LWIP_Process(); - Keil工程配置,勾上就对了(不勾上会生成

BKPT 0xAB,此时MCU会死机,具体原因未知)

下载代码,实现现象

工程文件下载链接

【STM32】HAL库-以太网外设-LAN8720A-LWIP-无操作系统-PING文章来源:https://www.toymoban.com/news/detail-475283.html

说明

初始化调用过程

MX_LWIP_Init() -> netif_add() -> ethernetif_init() -> low_level_init() -> HAL_ETH_Init() -> LAN8742_Init() -> ethernet_link_check_state()Get link state文章来源地址https://www.toymoban.com/news/detail-475283.html

到了这里,关于【STM32】HAL库-以太网外设-LAN8720A-LWIP-无操作系统的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!