一、实验任务及要求

1. 设计要求

篮球比赛中,进攻一方取得球权后双方开始比赛,若24秒到,该进攻一方仍然没有投球时,需要交换发球权。本实验要求设计一个24秒违例计时器(倒计时方式),当计时24秒时间到,用一个红色指示灯亮表示,指示灯持续点亮5秒。

要求电路设置一个启动开关,当该开关断开时,数码管显示24秒,当开关闭合后,电路开始运行,期间断开该开关,数码管又重新显示24秒。

二、思考题

1. 设计过程中遇到过哪些问题?是如何解决的?

2. 通过此次时序逻辑电路实验,总结任意进制计数器的设计方法。

三、篮球比赛24秒倒计时器设计

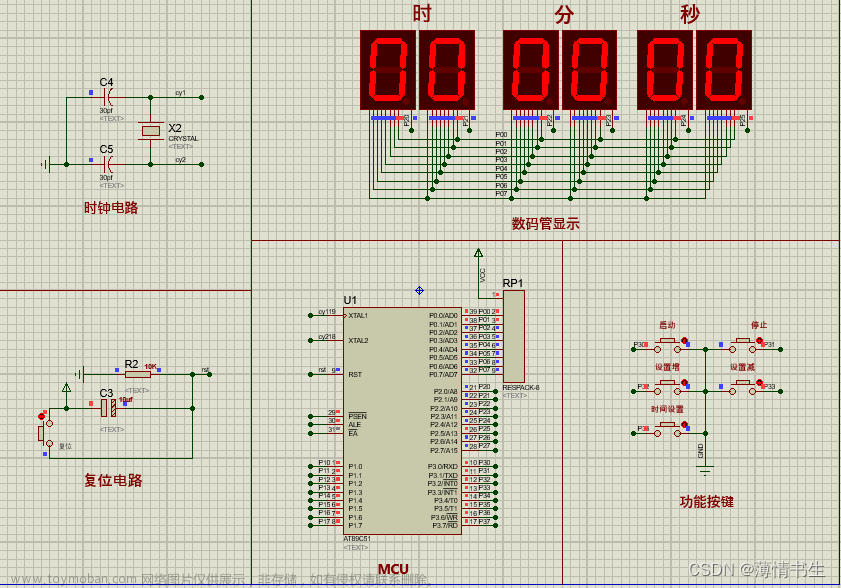

实验电路仿真如下

(1)此次实验主要用到的芯片有74192N计数器和JK触发器。

(2)24秒计数(绿色)是用到74192的down端,当个位借位信号BO来临的时候,十位会相当于一个脉冲输入down端,即十位减1(20->19)。另外当24秒计数结束后,24秒的时钟(接在JK触发器输出端)也就被停了,故显示00。

(3)十位借位端BO跟开关(空格)与是为了实现当该开关断开时,数码管显示24秒,当开关闭合后,电路开始运行,期间断开该开关,数码管又重新显示24秒。

(4)5秒计数器,当24计数结束时,十位借位信号BO作为JK触发器(开关断开时出态已置1)的时钟信号,利用了输出Q端跟普通的时钟信号与产生的时钟信号送到右边的5秒计数器up端,同时十位借位信号BO也传到右边的5秒计数器异步清零端。

(5)红灯,当下端的JK触发器Q端信号来临时,跟5秒计数器的0101信号或作为上面JK触发器的时钟信号,同样这个JK触发器也是开关断开时出态已置1,但此时红灯接到Q ‘ 端。

(6)这样操作后,当24秒计数结束时,信号传到下面的JK触发器使其为0,上面JK触发器翻转,红灯亮起。同时右边5秒计数器开始工作,当右端计数到5秒时,上面JK触发器翻转,红灯熄灭,5秒计数器的脉冲时钟接在JK触发器输出非端)也被停了。故功能全部实现。

总结

由于仿真器材完善,所以此次两个小实验均无悬空的无用输入端,基本上都是现有芯片和门电路构成。

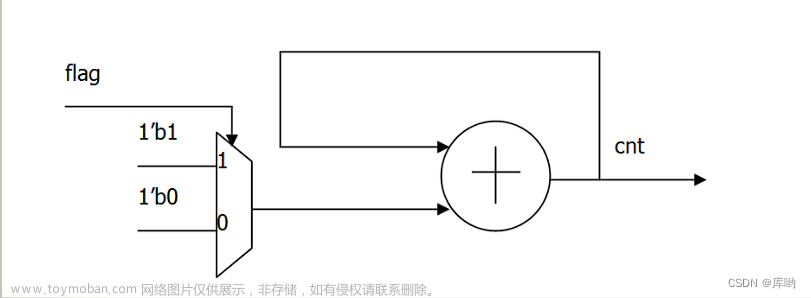

1.要达到只来一个脉冲后才开始工作的要求,可以使其跟正常的时钟信号与运算作为下一个时钟信号,即此实验的5秒计数器原理。

2.或门可实现来两个信号,只要一个信号来临时,JK触发器就翻转

3.计数器可以用普通的脉冲时钟来实现,也可以用借位信号来实现计数。

Multisim仿真文件(仅供学习参考):文章来源:https://www.toymoban.com/news/detail-476403.html

链接:https://pan.baidu.com/s/1K3Olw3wvS5R4SjzK_7y0lQ?pwd=6666

提取码:6666文章来源地址https://www.toymoban.com/news/detail-476403.html

到了这里,关于时序逻辑电路的设计(二) -- 篮球比赛24秒倒计时电路(附Multisim)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!