【2022.05西南交大数电实验】

【本代码及波形已通过老师验收。仅供参考。】

【参考博客:[数电实验]外星萤火虫设计_难凉oh的博客-CSDN博客】

【建议:有些口语化的注释看完删掉比较好哈,怕老师查验的时候看起来太明显咯】

最后一次数电实验啦!!完结撒花~~祝大家实验考试顺利!!

目录

1 Quartus代码编写

2 test代码

3 ModelSim仿真

4 实验记录、实物接线与实验现象

1 Quartus代码编写

本代码将信虫、哨虫模式合在一起编写。

module yck_1716_7_1(clk, f0, p, sta, f1, f2);

input clk; //50MHz的高精度时钟源输入

input f0; //虫后的发光信号,信虫电路的输入

input p; //位置信息:0表示不在边界地区,1表示在边界地区

input sta; //状态安全信息:0表示安全,1表示敌人来犯

//f1与虫后的f0同频同相

output f1; //信虫电路的输出,哨虫电路的输入

output f2; //哨虫电路的输出

reg f1,f2;

parameter N0 = 5000; //0.1毫秒的脉冲走过多少个时钟信号:0.1ms/(1/50MHz) = 0.1ms/20ns = 5000个

//防卫信号的脉冲宽度是0.1毫秒

//该信号是根据信虫信号f1进行的同步反馈

//如果安全(sta==0),防卫信号是一个与f1同相的双脉冲信号f2a

//当敌人来犯(sta==1),防卫信号是三脉冲信号f2b

reg [14: 0] cnt; //计数

reg temp; //寄存上一clk时刻f0值

reg flag; //用以判断f0是否为上升沿给出的标志信号

always @ (posedge clk)

begin

if(!temp & f0) //temp为上一clk时刻f0值

flag <= 1'b1; //判断f0上升沿,并给出标志信号

if(flag)

begin

casex({p,sta}) //拼接在一起

2'b0_x: //哨虫不在边界地区,职能为信虫

begin

if(cnt < 3*N0)

begin

f1 <= 1'b1;

f2 <= 1'b1;

cnt <= cnt + 1'd1;

end

else

begin

f1 <= 1'b0;

f2 <= 1'b0;

cnt <= 15'd0;

flag <= 1'b0; //脉冲产生结束,标志信号置0

end

end

2'b1_0: //哨虫在边界地区,且边界安全

begin

if(cnt < N0)

begin

f1 <= 1'b1;

f2 <= 1'b1; //对应f2a的第一处高电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 2*N0)

begin

f1 <= 1'b1;

f2 <= 1'b0; //对应f2a的低电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 3*N0)

begin

f1 <= 1'b1;

f2 <= 1'b1; //对应f2a的第二处高电平区

cnt <= cnt + 1'd1;

end

else

begin

f1 <= 1'b0;

f2 <= 1'b0;

cnt <= 15'd0;

flag <= 1'b0; //脉冲产生结束,标志信号置0

end

end

2'b1_1: //哨虫在边界地区,且边界不安全

begin

if(cnt < N0)

begin

f1 <= 1'b1;

f2 <= 1'b1; //对应f2b的第一处高电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 2*N0)

begin

f1 <= 1'b1;

f2 <= 1'b0; //对应f2b的第一处低电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 3*N0)

begin

f1 <= 1'b1;

f2 <= 1'b1; //对应f2b的第二处高电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 4*N0)

begin

f1 <= 1'b0;

f2 <= 1'b0; //对应f2b的第二处低电平区

cnt <= cnt + 1'd1;

end

else if(cnt < 5*N0)

begin

f1 <= 1'b0;

f2 <= 1'b1; //对应f2b的第三处高电平区

cnt <= cnt + 1'd1;

end

else

begin

f1 <= 1'b0;

f2 <= 1'b0;

cnt <= 15'd0;

flag <= 1'b0; //脉冲产生结束,标志信号置0

end

end

endcase

end

else cnt <= 15'd0;

temp <= f0;

end

endmodule

2 test代码

得到测试v文件的步骤见博客【数电实验5】Verilog—可控分频器设计 & ModelSim的使用_kokoのadventure的博客-CSDN博客_可控分频器设计

参考博客中的占空比存在问题,本人根据自己的理解进行了修正如下:

`timescale 1 ns/ 1 ns

module yck_1716_7_1_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg clk;

reg f0;

reg p;

reg sta;

// wires

wire f1;

wire f2;

// assign statements (if any)

yck_1716_7_1 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.f0(f0),

.f1(f1),

.f2(f2),

.p(p),

.sta(sta)

);

initial

begin

// code that executes only once

// insert code here --> begin

clk = 0;

f0 = 0;

p = 0;

sta = 0;

#11000000 p = 1; //11ms后由信虫模式变为哨虫模式

#10000000 sta = 1; //再10ms后敌人来犯

// --> end

$display("Running testbench"); //可删掉哦

end

always #10 clk = ~clk; //50MHz时钟信号

always

begin

// insert code here --> begin

//产生虫后信号f0

//繁殖季占空比为50%

//正常时是30%占空比的毫秒脉冲,年老时占空比逐渐减小,周期逐渐增大,直至死亡

//题设:f0的频率范围是0.5kHz(周期2.0ms)~1.2kHz(周期0.83ms)

//此处f0取1kHz

//题设:占空比1%~30%

f0 = 1; #500000; //0.5ms 繁殖季占空比为50%

f0 = 0; #500000; //0.5ms

f0 = 1; #300000; //0.3ms 正常占空比为30%

f0 = 0; #700000; //0.7ms 这里正常状态的数量可以自己选哈,这里就设置两个正常状态

f0 = 1; #300000; //0.3ms 正常占空比为30%

f0 = 0; #700000; //0.7ms

f0 = 1; #200000; //0.2ms 开始衰老占空比为20%

f0 = 0; #800000; //0.8ms

f0 = 1; #100000; //0.1ms 占空比为10%

f0 = 0; #900000; //0.9ms

f0 = 1; #50000; //0.5ms 占空比为5%

f0 = 0; #950000; //0.95ms

// --> end

end

endmodule

其中,正常状态(占空比为30%)的设置为了一个周期出现两次。

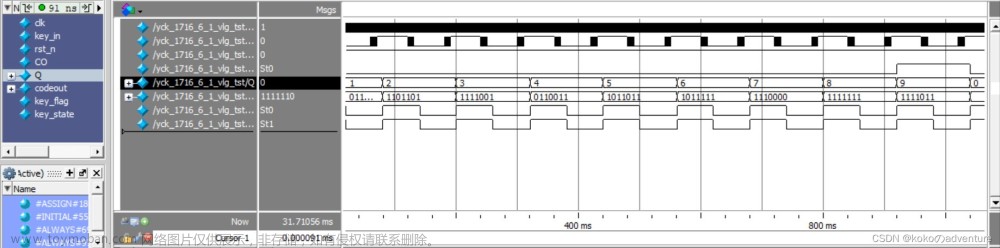

3 ModelSim仿真

生成相关波形的相关步骤见博客【数电实验5】Verilog—可控分频器设计 & ModelSim的使用_kokoのadventure的博客-CSDN博客_可控分频器设计

测试波形如下:

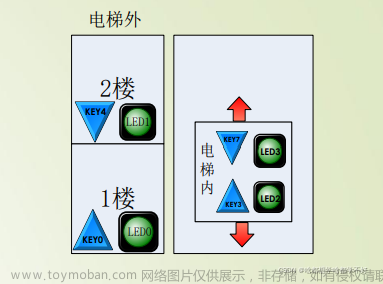

4 实验记录、实物接线与实验现象

| 信号名 |

主板器件 |

PIN |

信号名 |

主板器件 |

PIN |

|

| clk |

50MHz |

PIN_90 |

f2 |

IO1/LED1 |

PIN_50 |

|

| p |

Key0/SW0/LED8 |

PIN_24 |

f1 |

IO0/LED0 |

PIN_46 |

|

| sta |

Key1/SW1/LED9 |

PIN_31 |

||||

| f0 |

ECLK |

PIN_23 |

||||

| Top-level Entity name |

Family |

Device |

| yck_1716_7_1 |

Cyclone IV E |

EP4CE6E22C8 |

| Total logic elements |

Total registers |

Total pins |

| 58 / 6,272 ( < 1 % ) |

19 |

6 / 92 ( 7 % ) |

| Total memory bits |

Embedded Multiplier 9-bit elements |

Total PLLs |

| 0 / 276,480 ( 0 % ) |

0 / 30 ( 0 % ) |

0 / 2 ( 0 % ) |

注意!选择脉冲波(或称矩形波)(可调占空比)而不是方波进行输出:

20%:

30%:

50%:

黑夹子接GND(不一定接图上位置的GND,随便哪个GND都行),红夹子接ECLK:

信虫模式:

哨虫模式(安全): 文章来源:https://www.toymoban.com/news/detail-477172.html

文章来源:https://www.toymoban.com/news/detail-477172.html

哨虫模式(敌袭): 文章来源地址https://www.toymoban.com/news/detail-477172.html

文章来源地址https://www.toymoban.com/news/detail-477172.html

到了这里,关于【数电实验7】Verilog—外星萤火虫的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!