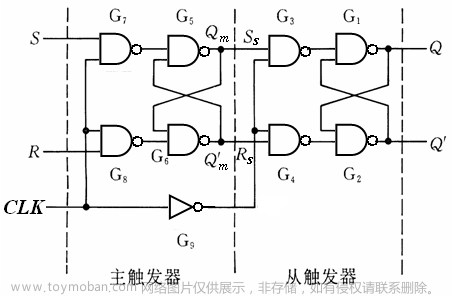

关于D触发器的内容见专栏的单片机原理及应用,主要是时钟脉冲出现时候,会改变输出状态。

下面来做一个D触发器的仿真实验。

部件

使用74LS74:带清除和预置端功能的双上升沿D型触发器

74LS74是一款现代集成电路芯片,属于TTL(Transistor-Transistor Logic)系列的D触发器芯片。它内部集成了两个D触发器,能够实现多种数字电路功能。

该芯片的具体参数包括:

- 工作电压范围:4.75V至5.25V

- 最大时钟频率:25 MHz

- 最大静态工作电流:4 mA

- 高电平输入电压:2V

- 低电平输入电平:0.8V

在数字电路中,在时钟的控制下,74LS74可以实现数据的存储,传输和计数等控制功能。它常常被用于各种数字电路设计中,比如计数器、分频器、频率调制器、数据采集等领域。

需要注意的是,74LS74在使用过程中需要注意电压稳定性,尤其是在高频率时钟下的稳定性。同时也需要注意静电防护,静电干扰可能会影响芯片的工作稳定性。

逻辑探测器LOGICPROBE(BIG)

逻辑探测器(Logic Probe)是一种测试数字电路的工具,它能够检测数字电路中的信号电平,并且可以判断它的高低电平状态。逻辑探测器通常用于测试和故障排除数字电路的情况下。

逻辑探测器通常包括一个尖端和一个显示屏。尖端通过电缆与待测试的电路连接在一起,显示屏会显示当前读取到的电平状态。通常情况下,逻辑探测器的显示屏可以显示高电平、低电平以及脉冲等信号。

逻辑探测器广泛应用于数字电路中各种测试和故障排查的场景,比如,检测微处理器和控制器的时钟和数据信号、检查逻辑门电路(比如AND、OR、NOT等)中的输出状态、检测逻辑控制系统的输入信号和输出信号等。它是检测和分析数字电路中的信号非常有用的工具。

逻辑切换器 LOGICTOGGLE

逻辑切换器(Logic Toggle)是数字电路中常见的一种元器件,它通常被用于切换电路中的状态或者控制电路中的信号,使得电路的功能可以在不同状态之间进行切换。

逻辑切换器通常被实现为一个D触发器或者JK触发器,它们的输入端口被连接到外部的控制信号,而输出端口控制了被切换的电路状态。当启用逻辑切换器时,触发器输出将改变,从而改变整个电路的状态。

逻辑切换器被广泛应用于数字电路中各种状态切换或者控制场景,比如在计算机中切换内存芯片、切换不同设备的输入输出信号等。它们可以帮助电路在不同的状态之间进行平滑地切换,以达到不同的控制目的。‘

示波器 OSCILLOSCOPE

示波器(Oscilloscope)是一种用于显示电压信号随时间变化的测试仪器,可用于测量电路中的电压、频率、相位等参数。它通常由显示器、控制栏、探头、通道、触发器等组成,能够捕获周期性和非周期性的信号波形,并显示其形状和幅度。

示波器的原理是使用探头将待测试的电路连接到示波器通道上,通过示波器内部的电路将电压信号转换成可视的波形图形式,并在显示器上显示出来。示波器通常有多个通道,可以同时测试多个信号源,并进行比较分析。

示波器被广泛应用于电子、计算机、通信、医疗等领域,它可以帮助工程师或者技术人员快速地检测和诊断问题,找到电路中的故障或者优化电路设计。基本上所有需要测量电信号的场合都需要使用示波器。

数字时钟 DCLOCK

它是一种显示时间数字的设备或应用程序。数字时钟通常由数码管、LCD 显示屏或 OLED 显示屏等组成,它可以显示当前时间(小时、分钟、秒钟等)或日期。数字时钟的显示方式可以是12小时制或24小时制。

数字时钟广泛应用于各种场景,比如装饰墙壁钟、手表、移动设备、计算机屏幕和机场车站等公共场所。数字时钟能够准确地显示当前时间,因此在生产和生活中非常重要。除了基本的显示功能外,数字时钟还可以具备其他功能,比如闹钟、倒计时、定时器等,为人们的生活提供更多的便利。

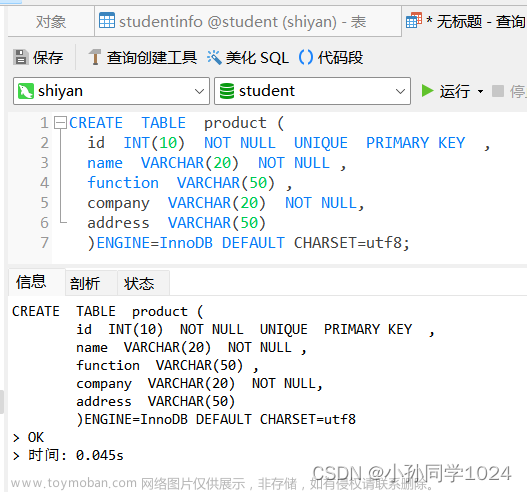

整体电路设计

仿真运行

当时钟信号 DCLOCK 到达 74LS74 的 CLK 引脚上时,锁存器会根据 D 的状态将 D 的值锁存到 Q 中。 而当逻辑探针 LOGICPROBE 连接到 74LS74 的 Q 引脚上时,当 Q 发生变化时, LOGICPROBE 的输出将对应地显示出 Q 引脚的电平状态。

因此,当按下逻辑开关和时钟信号 DCLOCK 在适当的条件下到达时,锁存器将保存逻辑开关的输出状态,并且 LOGICPROBE 的输出将显示存储在锁存器中的电平状态。

在示波器上,可以看到时钟信号 DCLOCK 的周期性方波信号,以及存储在锁存器中的电平状态 Q 的信号的变化。如果逻辑开关的输出状态一直保持不变,那么 Q 的电平状态也会一直保持不变,因此在示波器上只能看到平稳的直线信号。但如果逻辑开关的输出状态发生变化,则可以在示波器上看到 Q 引脚对应的电平状态发生相应的变化。

项目文件和运行视频

文件

视频见:

文章来源:https://www.toymoban.com/news/detail-478559.html

D触发器波形变化文章来源地址https://www.toymoban.com/news/detail-478559.html

到了这里,关于D触发器仿真实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!