1.什么是STA?

STA(静态时序分析)是时序验证的一种方法,用于计算和分析电路是否满足时序约束的要求。

2.为什么需要STA?

电路能否正常工作,其本质上是受最长逻辑通路(即关键路径)的限制,以及受芯片中存储器件的物理约束或工作环境的影响。

为了保证电路能够满足设计规定的时序规格及器件的约束条件,必须验证关键路径以及与关键路径延迟相近的通路是否满足时序要求,这就必须考虑逻辑门的传输延时、门之间的互连、时钟偏移、I/O时间裕度以及器件约束(建立时间、保持时间和触发器的时钟脉冲宽度)。如果边沿触发器的建立或保持时间这个约束条件被违反了,则触发器将进入亚稳态。

时序验证利用电路的器件和互连模型来分析电路时序,以此来判断物理设计是否能达到硬件的时序约束条件和输入/输出的时序规范。时序验证可以直接仿真电路的行为,一次判断是否达到硬件约束和性能指标,这种方法称为动态时序分析(DTA);也可以不直接仿真电路的行为而是通过分析电路中所有可能的信号通路来间接判定是否满足时序约束条件,成为静态时序分析(STA)。

3.建立时间和保持时间

(1)建立时间和保持时间的概念

为了确保寄存器在时钟沿稳定采集数据,那么必须要满足寄存器的建立,保持时间(setup/hold time)要求。

建立时间要求:在寄存器有效时钟沿之前至少Tsetup时间,数据必须到达且稳定。

保持时间要求:在数据采集有效时钟沿之后,数据必须维持最短Thold时间不变。

(2)触发器的建立时间裕度(setup time slack)

下图中,假设触发器CK端到Q端的延迟为1ns,时钟频率为100MHz,组合逻辑延迟为2ns,触发器的建立时间Tsetup = 2ns, 保持时间 Thold = 1ns.

前一级寄存器(DFF1)在第N个时钟沿发出的数据,经过最长路径(logic)的延迟后,需要在第N+1个时钟沿的setup/hold窗口之前稳定。也就是说,对于建立时间的要求,需要其在下一个时钟沿的setup time之前把数据发送完毕。

数据到达时间(data arrival time):对于DFF2而言,就是数据到达D端的时间

Tdata_arrive =Tclk_path_delay + Tck->q + Tlogic_delay = 1ns + 1ns + 2ns = 4ns

即等于时钟的延迟加上触发器CK到Q端的延迟再加上组合逻辑的延迟。

数据所需时间(data required time):表示数据到达的最晚时间点。数据需要在该时间点之前到达寄存器端。对于DFF2而言,就是数据到达CK端的时间减去Tsetup

Tdata_require = Tclk_period + Tclk_path_delay - Tsetup

即一个时钟周期时间加上时钟信号到达触发器DFF2时钟输入端的延迟时间减去触发器的建立时间。

假设时钟频率为100MHz,则Tclk_period = 10ns.

所以 Tdata_require = 10ns - 2ns = 8ns.

对于建立时间裕度: Tsetup_slack = Tdata_require - Tdata_arrive

建立时间裕度需要满足条件:Tsetup_slack > 0, 即 Tdata_require - Tdata_arrive > 0.

(3)触发器的保持时间裕度(hold time slack)

前一级寄存器(DFF1)在第N个时钟沿发出的数据,经过最短路径的延迟后,需要在第N个时钟沿的setup/hold窗口之后出现。

对于hold time,数据到达时间 Tdata_arrive 同setup time。

而数据所需时间Tdata_required = Tclk_path_delay + Thold

也就是说,对于保持时间的要求,需要其在同一个时钟沿的hold time之后才能拿到数据。另外需要注意的是,在做setup time的检查时,组合逻辑的延迟Tlogic_delay需要取延迟最长的组合逻辑路径,而在做hold time的检查时,则需要取延迟最短的组合逻辑路径。

保持时间裕度:Thold_slack = Tdata_arrive - Tdata_require (与建立时间裕度相反)

保持时间裕度需要满足条件:Tsetup_slack > 0, 即 Tdata_arrive - Tdata_require > 0.

4.如何计算电路的最大时钟频率

求最大时钟频率,就是分析每个DFF的setup time。

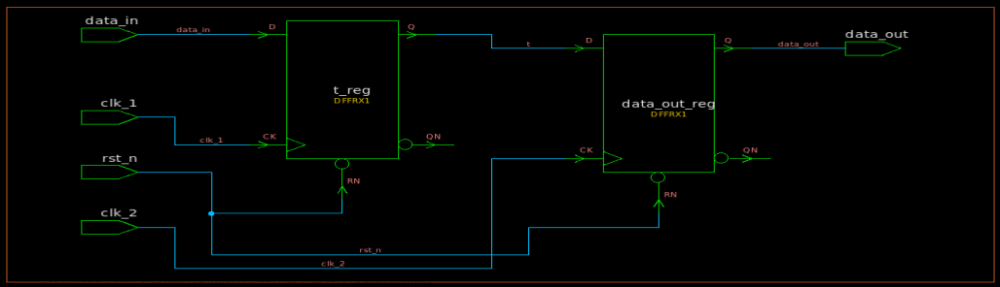

如下图所示题目,第一步求其最大工作频率:

对每个DFF,分析它们的建立时间:

DFF1:

数据到达D端的时间:Tdata_arrive = 1 + 1.1 + 1.1 + 2 + 1.5 = 6.7ns, 如下图

而数据所需时间 Tdata_required = Tcycle + 1 + 1.1 + 1.1 - 2.5= Tcycle + 0.7ns

所以DFF1的建立时间裕量 Tsetup_slack = Tdata_required - Tdata_arrive >= 0,

即 Tcycle >= 6ns.

DFF2:

数据到达D端的时间:Tdata_arrive = 1 + 1.1 + 1.1 + 2 = 5.2ns,如下图

而数据所需时间 Tdata_required = Tcycle + 1 + 1.2 + 1.2 + 1.4 - 2.5 = Tcycle + 2.3ns

DFF2的建立时间裕量 Tsetup_slack = Tdata_required - Tdata_arrive >= 0,

即 Tcycle >= 2.9ns

所以 Tcycle >= 6ns.最大频率为 1/Tcycle = 166.67MHz

5.如何判断电路是否出现时钟违例

判断电路是否出现时钟违例,就是检查每个DFF的hold time。

对于DFF1的hold time分析:

数据到达D端的时间:Tdata_arrive = 1 + 1.1 + 1.1 + 2 + 1.5 = 6.7ns

数据所需时间: Thold_time = 1 + 1.1 + 1.1 + Thold = 1 + 1.1 + 1.1 + 1 = 4.2ns

稳定时间裕量:Thold_slack = Tdata_arrive - Tdata_require = 2.5 ns > 0.

所以DFF1没有出现时钟违例。

对于DFF2的hold time分析:

数据到达D端的时间:Tdata_arrive = 1 + 1.1 + 1.1 + 2 = 5.2ns

数据所需时间: Thold_time = 1 + 1.2 + 1.2 + 1.4 + 1 = 5.8ns

稳定时间裕量:Thold_slack = Tdata_arrive - Tdata_require = -0.6ns < 0文章来源:https://www.toymoban.com/news/detail-479460.html

所以DFF2存在时钟违例。修正方法为去除1.4ns延迟的buffer。文章来源地址https://www.toymoban.com/news/detail-479460.html

到了这里,关于STA(静态时序分析) 详解:如何计算最大时钟频率,以及判断电路是否出现时钟违例(timing violation)?的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!