一、 实验内容

在 CMOS 工艺下,设计一个 CMOS 运算放大器,并利用 Virtuoso 工具对其性能进行仿真和分析。

二、 实验目的

深入理解 CMOS 运算放大器的设计方法和性能分析方法。

三、 实验要求

设计符合下列要求的 CMOS 运算放大器,结构不限。

1、技术指标要求:

供电电压:VDD 3.3v GND 0v

输入信号:正弦差分信号

共模电压范围为 1V

差分幅值范围 1mv

输出信号:正弦信号

摆率大于 10V/us(CL=10pF)

单位增益带宽:GB 不小于 5MHz(CL=10pF),3dB 带宽:不小于 5KHz。

幅值增益:70dB

相位裕度:大于 60 度

功耗小于 2mW

工作温度:0~85 摄氏度

2、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。逐步完成电路级设计、电路级仿真各个步骤。

3、电路的仿真与分析要求,要进行直流工作点、交流 AC 分析、瞬态 Trans 分析、建立时间小信号特性和摆率大信号分析,能熟练掌握各种分析的参数设置方法。

4、电路性能的优化与器件参数调试,并给出测试结果,要求达到预定的技术指标。

5、测试参数:电压增益、相位裕量、-3dB 频率带宽、摆率

6、整理仿真数据与曲线图表,撰写并提交实验报告

四、实验结果及分析

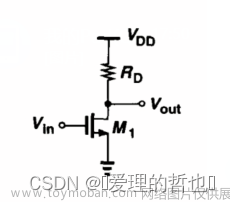

总体电路图:

仿真参数:

电流-30uA

Ac仿真结果:

由曲线知:

电压增益为71.025dB

相位裕量为91.21°

-3dB带宽为5.42kHz

输入方波后瞬态仿真:

仿真参数:

结果:

由图知:

摆率为11.3V/us文章来源:https://www.toymoban.com/news/detail-479693.html

五、实验感悟

实验,我再一次温习了放大器参数的设计,以及相关概念的含义。同时,对cadence的virtuoso的使用有了一个更加全面的掌握,对性能指标的测量有了更深刻的了解。文章来源地址https://www.toymoban.com/news/detail-479693.html

到了这里,关于集成电路工程实验——模拟部分(北京理工大学)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!