目录

前言

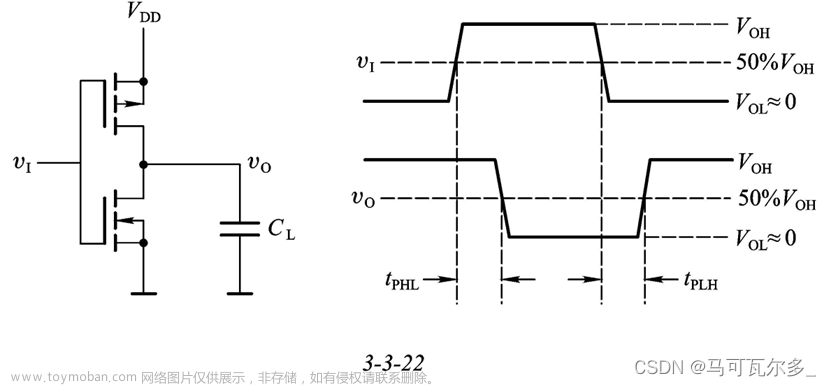

CMOS电路的延时分析

导通阈值

前言

在时序逻辑电路设计中,总是需要考虑延时信息,比如保持/建立时间,后端的静态时序分析等。

平时在做数字电路设计时中,信号传播的是0/1,一般考虑的是组合逻辑计算延时,一个时钟周期能不能计算完,算不完的话如何插入FF减小关键路径延时等概念性的东西,那么电路的根本传输延时到底是哪里来的呢?

CMOS电路的延时分析

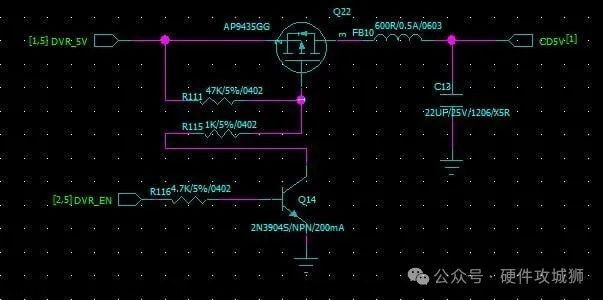

CMOS电路是电压驱动器件。通过在MOS管的栅极输入大于阈值Vth的电压,使栅极下产生导电沟道,从而让源漏之间能够导通传播电压。

mos管在栅衬之间的导电沟道是由电压差形成的,所以可以将此沟道视为小电容,有电容就有充放电时间,如果再有个电阻的话,就构成了RC延时电路结构。

那么电阻在哪里?在上级的导通的mos管。导通的mos在VDS没那么大的时候等效为一个小电阻Ron,这个电阻和后端的栅衬电容构成了基本的RC延时电路,导致了传输延时时间。

时间常数 = RC ,所以导通电阻越小,等效电容越小,时间常数越小,传输延时越小。

Q:导通电阻怎么减小?

A:ron = 1/2K(Vgs-Vt)。增大Gate端电压,在栅衬之间聚集的少子(N管是电子,P管是空穴)越多,导电沟道越宽,导通电阻就越小。但是对应的等效电容也越大。

传输延迟时间反应了电路的响应速度,现在芯片都要求高频率,所以芯片电压是越来越小的趋势。

导通阈值

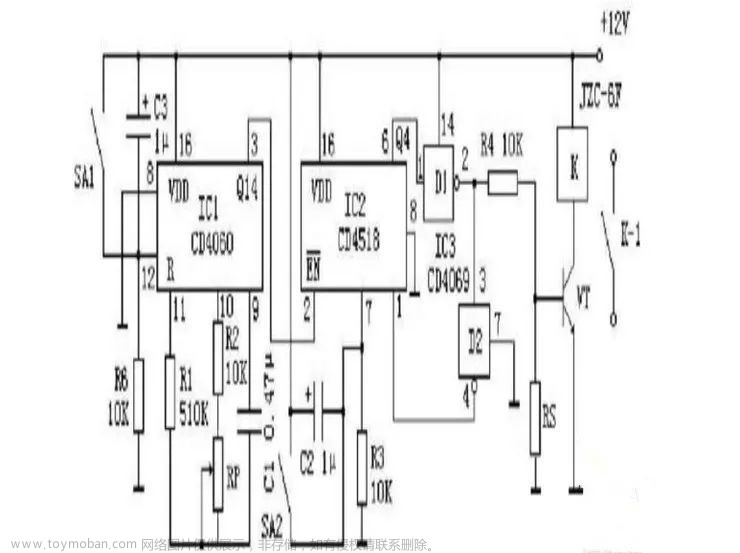

传输延迟时间还可以通过降低mos管阈值来实现,但是降低阈值Vt会导致静态漏电流的增加。

LVT, RVT, HVT这几个都是CMOS集成电路的Vth阈值电压相关的基本概念。

通常将传输特性曲线中输出电压随输入电压改变而急剧变化转折区的中点对应的输入电压称为阈值电压。

HVT = High V threshold.

comment:Can be used in the path where timing is not critical. So by using HVT cells we can save power.

LVT - Low V threshold.

comment:One should use these cells in timing critical paths. These cells are fast but , comsumes more power due to its leakage. So it will consume more power. So use only when timing is critical.

SVT- Standard V threshold.

comment:Best of both world. Medium delay and medium power requirment. So if timing is not met by small magin with HVT, you should try with SVT. And at last LVT.

RVT- Regular V threshold. Another name for SVT.

阈值电压越低,因为饱和电流变小,所以速度性能越高;但是因为漏电流会变大,因此功耗会变差。

速度大小按快到慢依次排列为SLVT, LVT, RVT, HVT。 功耗大小却正好相反。即HVT的cell其阈值电压最大其掺杂浓度越高,其泄露功耗最小;根据时序紧张还是不紧张,对于关键路径选择速度快,功耗差的,对于时序比较宽松的,可以用速度慢一些的器件。在满足时序的情况下降低功耗~

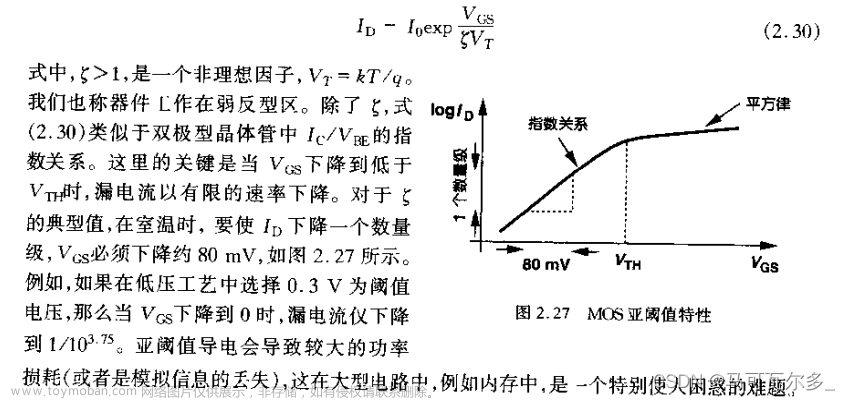

静态功耗的来源大部分时由于mos管亚阈值导电性带来的静态泄露功耗,Leakage。

通常在分析Mos管的时候,认为在VGS<Vth时,mos管突然就关断。实际上Vgs<Vth时一个比较弱的沟道仍然存在,与Vgs成指数关系。这时mos管的一种二级效应,即亚阈值导电性。

公式如下

文章来源:https://www.toymoban.com/news/detail-479813.html

文章来源:https://www.toymoban.com/news/detail-479813.html

参照拉扎维书,具体的推论不研究,总之,阈值电压越大,Leadage越小,速度越慢。文章来源地址https://www.toymoban.com/news/detail-479813.html

到了这里,关于为什么CMOS门电路存在传输延时,及解决方案的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!