目录

概要

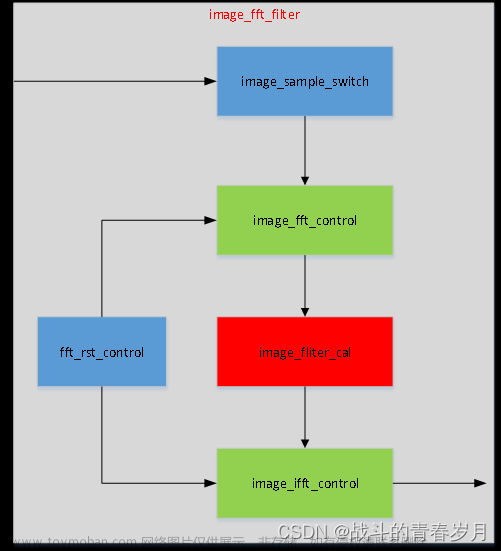

整体架构流程

技术名词解释

技术细节

编辑

小结

概要

提示:这里可以添加技术概要

本文主要基于DDR的图像缓存设计。

整体架构流程

提示:这里可以添加技术整体架构

先用图像产生模块产生一个1080P60Hz的测试图像,然后经过FDMA进入ddr3,缓存3帧后在读出来。然后在经过HDMI显示。

技术名词解释

FDMA:这是米联科开发一款DMA控制器,本文也是本着学习及分享两种意图写下了此文。

技术细节

在这里我们引入了AXi_interconnect IP,因为smc不能满足FDMA和MIG的最大带宽,导致1080P视频不能正常传输,并且在interconnected IP中要使能寄存器输出,并在使能fifo深度。

这样就能完美传输1080P@60fps的视频。

always@(posedge clk) begin

if(hcounter < hMax - 12'd1) //line over

hcounter <= hcounter + 12'd1;

else

hcounter <= 12'd0;

end

always@(posedge clk) begin

if(hcounter == hMax - 12'd1) begin

if(vcounter < vMax - 12'd1) //frame over

vcounter <= vcounter + 12'd1;

else

vcounter <= 12'd0;

end

end

assign hsync = ((hcounter >= (hStartSync - 2'd2))&&(hcounter < (hEndSync - 2'd2)))? 1'b0:1'b1; //Generate the hSync Pulses

assign vsync = ((vcounter >= (vStartSync - 1'b1))&&(vcounter < (vEndSync - 1'b1)))? 1'b0:1'b1; //Generate the vSync Pulses

assign de = (vcounter >= vVisible || hcounter >= hVisible) ? 1'b0 : 1'b1;

assign r_o = r_i;

assign g_o = g_i;

assign b_o = b_i;

endmodule

其实这里我们弄清楚一个问题:

为什么需要缓存,而不是为了设计缓存而去设计缓存。所以我的思想也比较天马行空,本文主要说明为什么,做什么,下节在去说明怎么做。

其实到目前为止,我也不知道他这个例程为什么要使用缓存。

文件上有这么一句,可能我理解能力比较差,没和案例结合在一起,发现问题。

(为了进行图像的多缓存,一般非同步信号至少要满足3缓存才能最大减小图片的延迟/撕裂/丢帧问题)

这个地方啊有两个重点,第一个非同步信号。(这个例程中,图片产生信号和HDMI输出信号同源,同步信号)那我其实可以这么理解,同步信号就不需要了。

第二个至少缓存三帧;

以上结论怎么来的呢。

在看下面一个结论:

由于摄像头产生的数据时钟速率和显示屏的时钟不匹配,而且当摄像头传来数据时,显示屏驱动模块不一定在此时需要数据,况且同一时刻摄像头传进的像素的位置不一定就是显示屏正刷新到的位置。故不能将摄像头的数据直接直接传输到显示屏驱动模块。

总结一些常见的认知,一般可以总结为以下几个方面:

1.时钟不同步,为导致一些异常情况

2.图像显示更加顺畅。

下面对整个流程做个初步设计,

关于FDMA:

fdma_wready设置为1,当fdma_wbusy=0的时候代表FDMA的总线非忙,可以进行一次新的FDMA传输,这个时候可以设置fdma_wreq=1,同时设置fdma burst的起始地址和fdma_wsize本次需要传输的数据大小(以bytes为单位)。当fdma_wvalid=1的时候需要给出有效的数据,写入AXI总线。当最后一个数写完后,fdma_wvalid和fdma_wbusy变为0。

fdma_rready设置为1,当fdma_rbusy=0的时候代表FDMA的总线非忙,可以进行一次新的FDMA传输,这个时候可以设置fdma_rreq=1,同时设置fdma burst的起始地址和fdma_rsize本次需要传输的数据大小(以bytes为单位)。当fdma_rvalid=1的时候需要给出有效的数据,写入AXI总线。当最后一个数写完后,fdma_rvalid和fdma_rbusy变为0

小结

提示:这里可以添加总结

例如:文章来源:https://www.toymoban.com/news/detail-479822.html

本文主要对图像缓存的应用场景,做了天马行空的介绍,下篇文章主要讲实际代码的实现过程文章来源地址https://www.toymoban.com/news/detail-479822.html

到了这里,关于FPGA实战开发-基于的ddr图像缓存设计(上)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!