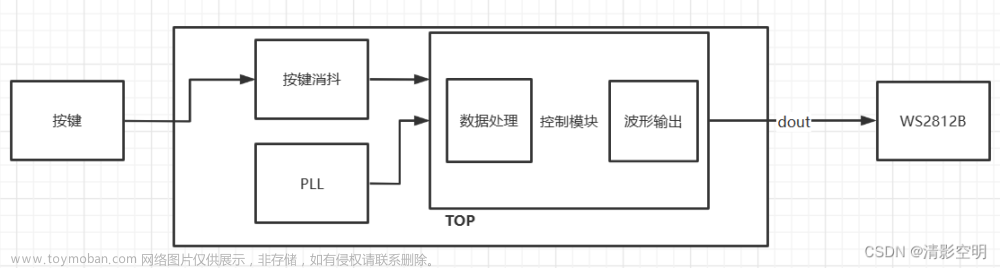

本次实现的功能就是利用FPGA驱动16*16点阵,在按键的配合下实现文字的滚动显示、数字的倒计时显示,以及按键控制显示等等。先上一幅实物图吧

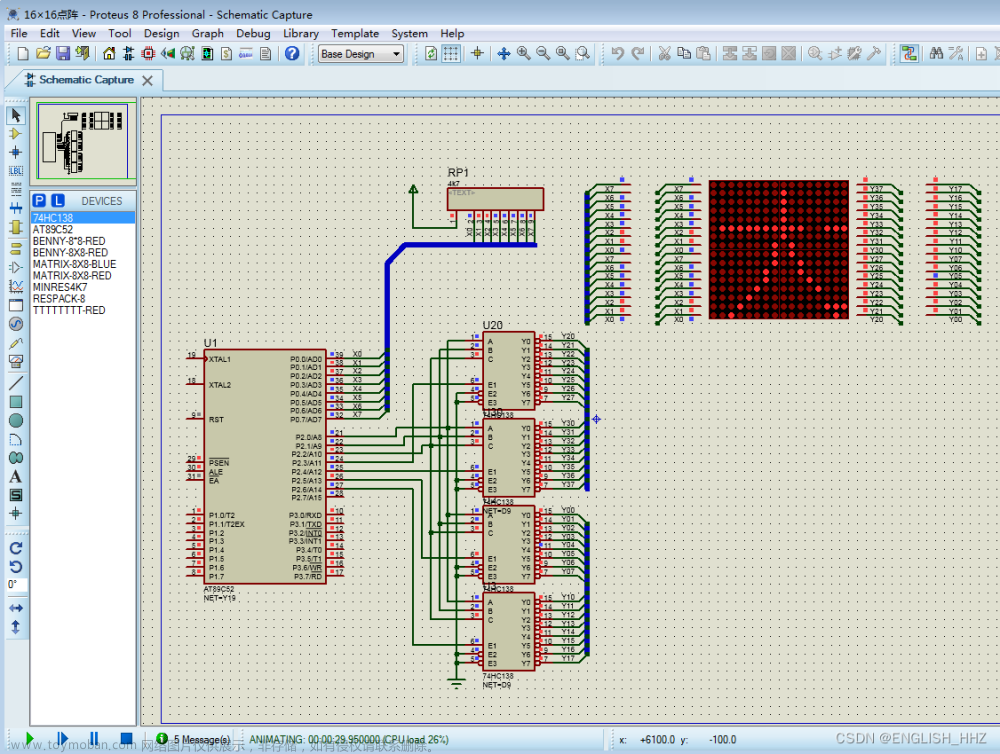

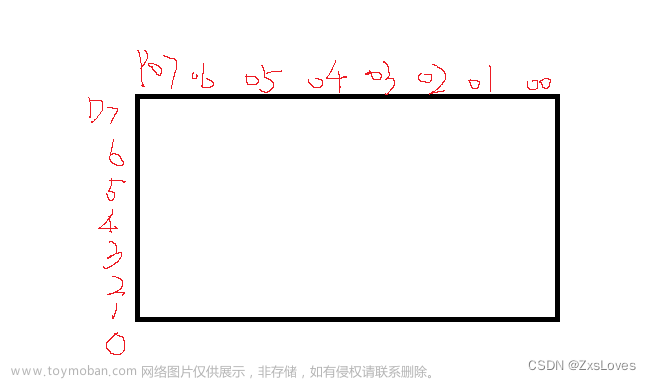

16*16点阵的硬件结构图如下所示:

可见,只要在C端输入高电平1,在R端输入低电平0,就可以点亮一颗LED。

我选择使用列扫描的方式,也就是按照一定的频率,依次给C0,C1,C2...高电平,然后分别将字模数据输入在R0--R15上,只要列扫描的频率足够大,由于人眼的视觉暂留效应,就可以在点阵屏幕上显示出字符。

接下来就是提取字符的字模数据了,这个时候就要用到字符转字模的软件了

软件截图如下:

在R0-R15给低电平,LED就被点亮。所以在设置字模提取方式时,要选择阳码(0点亮)。其余的配置选择如图所示:

配置好后,就可以输出字模数据了

如果要显示很多字符,那么字模数据量是很庞大的。那么如何存储这些数据就成为了问题。我选择的方案是将字模数据存在ROM里面。要使用的时候直接去ROM里面读取即可。注意ROM的数据宽度要为16位。其他的ROM配置步骤我在这里就不多介绍了。(注意,使用ROM前还需要配置好mif文件。数据主要是存储在mif文件里面的)

一切准备就绪以后,就是代码的编写了。

首先要例化ROM模块,因为字模数据全部在ROM里面。

然后还需要一些不同频率的时钟信号

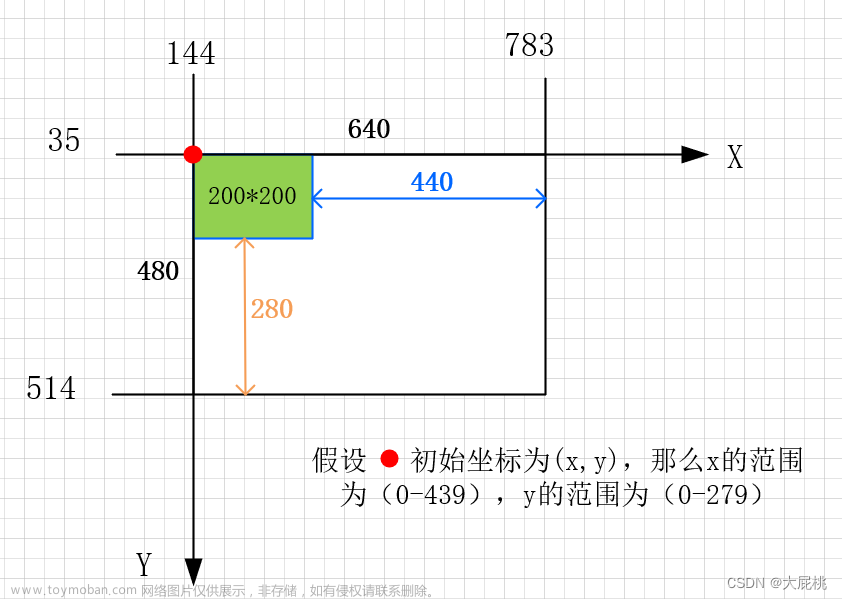

再接着就是根据列扫描信号,提取出对应的字模数据。由于使用了ROM,提取ROM里面的数据时,只需要给出ROM的地址就行。

动态显示(滚动显示)的关键在于,传入给ROM的地址,是以人眼可以识别的频率动态变化的。关键代码如下:

需要完整代码的,请私信文章来源:https://www.toymoban.com/news/detail-480590.html

文章来源地址https://www.toymoban.com/news/detail-480590.html

到了这里,关于FPGA项目(1)--FPGA驱动16*16点阵动态显示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!