目录

学习目标

学习内容

端口

端口列表

端口声明

端口链接规则

学习时间

总结

学习目标:

1.说明Verilog 模块定义中的各个组成部分,例如模块名、端口列表、参数、变址声明、数据流描述语句、行为语句、调用(实例引用》其他模块以及任务和函数等。

2.说明verilog模块定义中的各个组成部分,例如模块名、端口列表、参数、变址声明、数据流描述语句、行为语句、调用(实例引用“其他模块以及任务和函数等.

3.理解如何定义模块的端口列表以及在 Verilog中如何声明,理解如何定义模块的端口列表以及在verilog中如何声明.

4.讲述模块实例的端口连接规则。讲述模块实例的端口连接规则.

5.理解如何通过有序列表和名字将端口与外部信号相连。·解释对verilog标识符的层次引用。 理解如何通过有序列表和名字将端口与外部信号相连.·解释对verilog标识符的层次引用.

学习内容:

通过对学习,我们知道了模块是设计中的基本功能块;在忽略模块实现的同时,重点讨论了如何对模块进行定义和调用(实例引用)。在本章中,我们将对模块的内部实现做深入的分析。 通过学习,我们知道了模块是设计中的基本功能块;在忽略模块实现的同时,重点讨论了如何对模块进行定义和调用(实例引用)。在本章中,我们将对模块的内部实现做深入的分析.

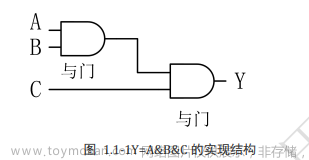

模块定义以关键字module开始,模块名、端口列表、端口声明和可选的参数声明必须出现在其他部分的前面,endmodule语句必须为模块的最后一条语句。端口是模块与外部环境交互的 、模块定义以关键字模块开始,模块名、端口列表、端口声明和可选的参数声明必须出现在其他部分的前面,终端模块语句必须为模块的最后一条语句。端口是模块与外部环境交互的 。

只有在模块有端凹的情况下才需要有端П列表和端口声明。模块内部的5个组成部分是:变量声明、数据流语句、低层模块实例、行为语句块以及任务和函数。这些部分可以在模块中的任意位置,以任意顾序出现。在模块的所有组成部分中,只有module、模块名和endmodule 必须出现,其他部分都是可选的,用户可以根据设计的需要随意选用。在一个Verilog源文件中可以定义多个模块,Verilog 对模块的排列顾序没有要求, 通道,只有在模块有端凹的情况下才需要有端П列表和端口声明.模块内部的5个组成部分是:变量声明、数据流语句、低层模块实例、行为语句块以及任务和函数.这些部分可以在模块中的任意位置,以任意顾序出现.在模块的所有组成部分中,只有模块、模块名和终端模块必须出现,其他部分都是可选的,用户可以根据设计的需要随意选用。在一个verilog源文件中可以定义多个模块,verilog对模块的排列顾序没有要求。

为了理解模块的各个组成部分,下面我们以SR锁存器为例进行详细说明,

SR锁存器有两个输人端口S和R以及两个输出端口,SR锁存器及其激励的Verilog 描述如例所示。 锁存器有两个输人端口S和R以及两个输出端口,SR锁存器及其激励的Verilog描述如例所示.

在SR锁存器的描述中,显示的各组成部分并未全部出现,例如变量声明、数据流( assign)语句和行为语句块( aways和 initial结构); ·在SR锁存器的描述中,中显示的各组成部分并未全部出现,例如变量声明、数据流(Ascription)语句和行为语句块(Aways和Initial结构);

在SR锁存器的激励模块中包括了模块名、线网/寄存器/变量声明、低层模块实例、行为语句块和endmodule语句,但是没有包括端口列表、端口声明和数据流( assign )语句;除了module和endmodule这一对关键字以及模块名,其他部分都是可选的,可以根据设计需要混合使用。 ·在SR锁存器的激励模块中包括了模块名、线网/寄存器/变量声明、低层模块实例、行为语句块和终端模块语句,但是没有包括端口列表、端口声明和数据流(赋值)语句;除了模块和终端模块这一对关键字以及模块名,其他部分都是可选的,可以根据设计需要混合使用。

端口

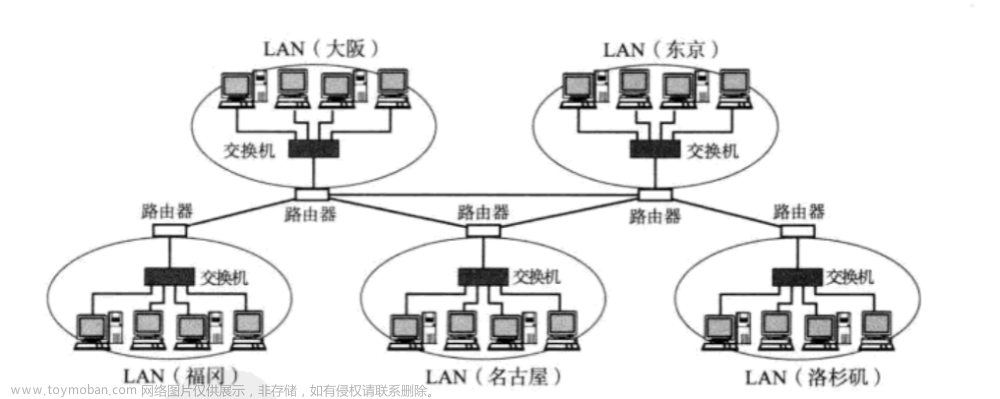

端口是模块与外界环境交互的接口,例如芯片的输人、输出引脚就是它的端口。对于外部环境来讲,模块内部是不可见的,对模块的调用(实例引用〉只能通过其端口进行。这种特点为设计者提供了很大的灵活性:只要接口保持不变,模块内部的修改并不会影响到外部环境。我们也常常将端口称为终端( terminal ) 端口是模块与外界环境交互的接口,例如芯片的输人、输出引脚就是它的端口.对于外部环境来讲,模块内部是不可见的,对模块的调用(实例引用>只能通过其端口进行.这种特点为设计者提供了很大的灵活性:只要接口保持不变,模块内部的修改并不会影响到外部环境.我们也常常将端口称为终端(终端).

端口列表

在模块的定义中包括一个可选的端口列表。如果模块和外部环境没有交换任何信号,则可以没有端口列表。考虑一个在顶层模块Top中被调用(实例引用)的四位加法器、显示了输人/输出端口的示意图。在中,Top是一个顶层模块,在其中调用(实例引用)了模块fulladd4,模块fulladd4从端口a,b和c_in读人数据,将结果从 sum和c_out 端口送出,这样它就可以作为加法器被外界调用(实例引用)。模块‘Top的作用是作为仿真中的顶层模块,调用(实例引用)设计模块。它无需和周围环境交换信息,因此没有端口列表。两个模块定义中的模块名和端口列表如所示。

端口声明

在Verilog 中,所有的端口隐含地声明为wire类型,因此如果希望端口具有wire数据类型,将其声明为三种类型之一即可;如果输出类型的端口需要保存数值,则必须将其显式地声明为reg数据类型。在下面的中,DFF触发器模块的输出端口q需要保持它的值,直到下一个时钟边沿,其端口声明如所示。

端口链接规则

我们可以将-个端口看成是由相互连接的两个部分组成,一部分位于模块的内部,另一部分位于模块的外部。当在一个模块中调用(实例引用)另--个模块时,端口之间的连接必须遵守一些规则。如果违反了这些规则,则Verilog仿真器会报错。中对这些规则进行了总结。

输入端口:从模块内部来讲,输入端口必须为线网数据类型;从模块外部来看,输入端口可以连接到线网或reg数据类型的变量。

输出端口:从模块内部来讲、输出端口可以是线网或reg数据类型;从模块外部来看,输出必须连接到线网类型的变量,而不能连接到reg类型的变量。

输入输出端口:从模块内部来讲,输入/输出端口必须为线网数据类型;从模块外部来看,输人/输出端口也必须连接到线网类型的变址。

学习时间:

2023.6.12晚

总结:

提示:这里统计学习计划的总量

模块定义包括多个组成部分。关键字module 和endmodule是必须使用的。其他各个部分,诸如端口列表、端口声明、变量和信号声明、数据流语句、行为语句块.低层模块实例以及任务和函数都是可选的,由用户根据需要进行添加。 模块定义包括多个组成部分.关键字模块和终端模块是必须使用的。其他各个部分,诸如端口列表、端口声明、变量和信号声明、数据流语句、行为语句块.低层模块实例以及任务和函数都是可选的,由用户根据需要进行添加.

端口是模块与其他模块或外部环境通信的渠道。模块可以具有一个端口列表,其中的每个端口必须在模块中声明为输入、输出或输人/输出三种类型之一。在对模块进行调用(实例引用)的时候,必须遵守有关端口连接的规则、ANSI C风格的端口声明将端口声明嵌人到端口列表中。

端口的连接方法有两种:顺序连接和命名连接. ·端口的连接方法有两种:顺序连接和命名连接.文章来源:https://www.toymoban.com/news/detail-480704.html

设计中的每个标识符都具有惟一的层次名,它使得用户可以在设计中的任何位置访问设计中的每个标识符。文章来源地址https://www.toymoban.com/news/detail-480704.html

到了这里,关于FPGA基础知识-模块和端口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA] 7系列FPGA的基础知识](https://imgs.yssmx.com/Uploads/2024/02/484166-1.png)