系列目录

Verilog 半加器和全加器

Verilog 半减器和全减器

串行加法器

11位全加器verilog设计

目录

系列目录

文章目录

前言

一、什么是半减器和全减器

半减器

全减器

二、半减器的verilog代码和testbench代码如下:

三、全减器的verilog代码和testbench代码如下:

四、全减器仿真结果:

RTL:

波形图:

前言

大二的数字逻辑课程和考试已经结束了,栽在了没细致研究的状态机上,但是对于一名计科学生来说,FPGA的领域仍然是广阔的,所以我将会把我之前学习所写的资料进行一个整理。

一、什么是半减器和全减器

半减器

半减器原理:两个二进制数相减叫做半减,实现半减器操作的电路称为半减器,半减器用于计算两bit x和y 的减法,输出结果diff和减法借位标志输出cin

半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位。它们的真值表如下:

| 被减数 | 减数 | 表示本位最终运算结果 | 表示本位是否向高位借位 |

| x | y | diff | cin |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

diff = x ^ y; cin = (~x) & y;全减器

要理解真值表,可以用举列子的方法得到:

| 被减数 | 减数 | 表示低位是否向本位借位 | 表示本位最终运算结果 | 表示本位是否向高位借位 |

| x | y | cout | diff | cin |

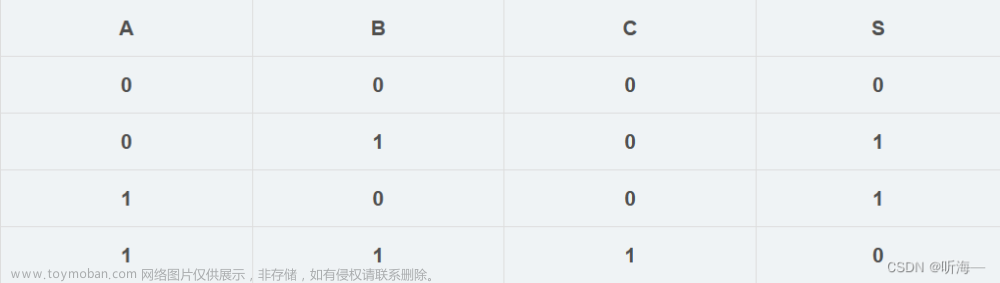

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

比如4'b1000 - 4b'0001,

则第一位对应0 1 0 1 1第二位对应的是0 0 1 1 1

从真值表中,可以得到

diff = x ^ y ^ cout, cin = (~x & (y ^ cout))|(y & cout)注意: +和|都表示或。

推导过程:

二、半减器的verilog代码和testbench代码如下:

代码如下(示例):

module halfsub(x,y,d,cin);

input x;

input y;

output d;

output cin;

assign d = x ^ y;

assign cin = (~x) & y;

endmoduletestbench:

`timescale 1ns/1ns

`define clock_period 20

module halfsub_tb;

reg x,y;

wire cin; //carryover

wire d;

reg clk;

halfsub halfsub_0(

.x(x),

.y(y),

.d(d),

.cin(cin)

);

initial clk = 0;

always #(`clock_period/2) clk = ~clk;

initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random;

end

initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random;

end

initial begin

#(`clock_period*20)

$stop;

end

endmodule三、全减器的verilog代码和testbench代码如下:

module fullsub(cout,x,y,d,cin);

input cout; // carry out bit, borrowed by its next low bit

input x;

input y;

output d;

output cin;

assign d = x ^ y ^ cout;

assign cin = (~x & (y ^ cout)) | (y & cout);

endmodule

`timescale 1ns/1ns

`define clock_period 20

module fullsub_tb;

reg x,y,cout;

wire cin; //carryover

wire d;

reg clk;

fullsub fullsub_0(

.cout(cout),

.x(x),

.y(y),

.d(d),

.cin(cin)

);

initial clk = 0;

always #(`clock_period/2) clk = ~clk;

initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random;

end

initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random;

end

initial begin

cout = 0;

repeat(20)

#(`clock_period) cout = $random;

end

initial begin

#(`clock_period*20)

$stop;

end

endmodule

四、全减器仿真结果:

RTL:

文章来源:https://www.toymoban.com/news/detail-481017.html

文章来源:https://www.toymoban.com/news/detail-481017.html

波形图:

文章来源地址https://www.toymoban.com/news/detail-481017.html

文章来源地址https://www.toymoban.com/news/detail-481017.html

到了这里,关于Verilog 半减器和全减器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!