本文链接:https://blog.csdn.net/qq_46621272/article/details/125337119

FIR 基础应用 - FM 调频波调制解调(FIR 低通滤波)

前言

这是 XILINX FIR IP 详解、Verilog 源码、Vivado 工程 这篇文章的实验部分,用 FIR 低通滤波实现了调频波的解调输出。

一、 调频波调制

1. fm_modulation_dds 模块逻辑框图

2. fm_modulation_dds.v verilog 代码

//fm_modulation_dds.v

module fm_modulation_dds

(

output m_axis_data_tvalid,

input m_axis_data_tready,

output [15:0] m_axis_data_tdata,

input rst_n,

input clk

);

parameter PHASE_COEF = 6554;//100KHz

reg signed [15:0] phase_cnt_r;

wire signed [15:0] s_axis_phase_tdata_i;

reg s_axis_phase_tvalid_r;

wire s_axis_phase_tready_i;

wire signed [15:0] phase_step_i;

wire signed [7:0] dds_4khz_tdata_i; // 4khz 正弦波 FM 调制信号

wire dds_4khz_tvalid_i;

wire dds_4khz_tready_i;

wire signed [15:0] fm_tdata_i; // FM 调频波

wire fm_tvalid_i;

wire fm_tready_i;

assign phase_step_i = dds_4khz_tdata_i*16;

assign dds_4khz_tready_i = s_axis_phase_tready_i;

assign s_axis_phase_tdata_i = phase_cnt_r;

always @(posedge clk)

begin

if(rst_n == 0 )

s_axis_phase_tvalid_r <= 0;

else if(s_axis_phase_tready_i == 1)

s_axis_phase_tvalid_r <= dds_4khz_tvalid_i;

end

always @(posedge clk)

begin

if(rst_n == 0 )

begin

phase_cnt_r <= 0;

end

else if(s_axis_phase_tready_i == 1 && dds_4khz_tvalid_i == 1)

begin

phase_cnt_r <= phase_cnt_r + phase_step_i + PHASE_COEF;

end

end

dds_compiler_1m_4k dds1 // XILINX VIVADO DDS IP,100MHz 时钟输入,4khz正弦波 8 位输出

(

.aclk (clk), // input wire aclk

.aresetn (rst_n), // input wire aresetn

.m_axis_data_tvalid (dds_4khz_tvalid_i), // output wire m_axis_data_tvalid

.m_axis_data_tready (dds_4khz_tready_i), // input wire m_axis_data_tready

.m_axis_data_tdata (dds_4khz_tdata_i) // output wire [7 : 0] m_axis_data_tdata

);

dds_compiler_phase dds2

(

.aclk (clk), // input wire aclk

.aresetn (rst_n), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid_r), // input wire s_axis_phase_tvalid

.s_axis_phase_tready(s_axis_phase_tready_i), // output wire s_axis_phase_tready

.s_axis_phase_tdata (s_axis_phase_tdata_i), // input wire [15 : 0] s_axis_phase_tdata

.m_axis_data_tvalid (fm_tvalid_i), // output wire m_axis_data_tvalid

.m_axis_data_tready (fm_tready_i), // input wire m_axis_data_tready

.m_axis_data_tdata (fm_tdata_i) // output wire [15 : 0] m_axis_data_tdata

);

assign fm_tready_i = m_axis_data_tready;

assign m_axis_data_tvalid = fm_tvalid_i;

assign m_axis_data_tdata = fm_tdata_i;

endmodule

二、 调频波解调

1. fm_demodulation_fir 模块逻辑框图

2. fm_demodulation_fir.v verilog 代码

//fm_demodulation_fir.v

module fm_demodulation_fir

(

input rst_n,

input clk,

input s_axis_data_tvalid,

output s_axis_data_tready,

input signed[15:0] s_axis_data_tdata,

output m_axis_data_tvalid,

input m_axis_data_tready,

output signed[15:0] m_axis_data_tdata

);

reg signed [15:0] uf_data_r = 0;

reg signed [15:0] sv_data_r = 0;

reg uf_valid_r = 0;

wire uf_tready_i;

reg [15:0] abs_data_r = 0;

reg abs_valid_r = 0;

wire abs_tready_i;

////////////////////////////////////////////////////////////////////////////////////

always @(posedge clk)

begin

if(rst_n == 0 )

uf_valid_r <= 0;

else if(uf_tready_i == 1)

uf_valid_r <= s_axis_data_tvalid;

end

always @(posedge clk) //微分 dx/dt ,dt =一个时钟周期,dx=当前数据减去上个时钟的数据的差

begin

if(rst_n == 0 )

begin

uf_data_r <= 0;

sv_data_r <= 0;

end

else if(uf_tready_i == 1 && s_axis_data_tvalid == 1)

begin

sv_data_r <= s_axis_data_tdata; //将当前数据存起来

uf_data_r <= s_axis_data_tdata - sv_data_r; //当前数据 - 上个时钟保存的数据

end

end

////////////////////////////////////////////////////////////////////////////////////

always @(posedge clk)

begin

if(rst_n == 0 )

abs_valid_r <= 0;

else if(abs_tready_i == 1)

abs_valid_r <= uf_valid_r;

end

always @(posedge clk) //绝对值

begin

if(rst_n == 0 )

abs_data_r <= 0;

else if(abs_tready_i == 1 && uf_valid_r == 1)

begin

if(uf_data_r >= 0)

abs_data_r <= uf_data_r;

else

abs_data_r <= -uf_data_r;

end

end

////////////////////////////////////////////////////////////////////////////////////

wire signed [39:0] fir_fm_tdata_i;

wire fir_fm_tvalid_i;

wire fir_fm_tready_i;

assign fir_fm_tready_i = m_axis_data_tready;

assign m_axis_data_tdata = fir_fm_tdata_i >>>19;

assign m_axis_data_tvalid = fir_fm_tvalid_i;

assign s_axis_data_tready = abs_tready_i;

assign uf_tready_i = abs_tready_i;

fir_compiler_lowpass_10k_30k_1m fm_fir_u1

(

.aresetn (rst_n), // input wire aresetn

.aclk (clk), // input wire aclk

.s_axis_data_tvalid (abs_valid_r), // input wire s_axis_data_tvalid

.s_axis_data_tready (abs_tready_i), // output wire s_axis_data_tready

.s_axis_data_tdata (abs_data_r), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid (fir_fm_tvalid_i), // output wire m_axis_data_tvalid

.m_axis_data_tready (fir_fm_tready_i), // input wire m_axis_data_tready

.m_axis_data_tdata (fir_fm_tdata_i) // output wire [31 : 0] m_axis_data_tdata

);

endmodule

三、 fm_modem_fir_testbench.v

///////////////////////////////////////////////////////////////////////

`timescale 1ns / 100ps

//fm_modem_fir_testbench.v

module fm_modem_fir_testbench;

reg rst_n;

reg clk;

parameter CLK_PERIOD = 1000; //1MHz

initial begin

rst_n = 0;

#(10 * CLK_PERIOD)

rst_n = 1;

#(3000 * CLK_PERIOD)

$stop;

end

initial

clk = 0;

always

begin

clk = #(CLK_PERIOD/2.0) ~clk;

end

wire signed [15:0] fm_mod_tdata; //调频波数据,载波100KHz 正弦波,调制信号 4KHz 正弦波

wire fm_mod_tvalid;

wire fm_mod_tready;

wire signed [15:0] fm_demod_tdata; //经过解调还原的 4KHz 正弦波

wire fm_demod_tvalid;

wire fm_demod_tready=1;

fm_modulation_dds fm_u1 //调频波调制模块,生成 载波100KHz 正弦波,调制信号 4KHz 正弦波的调频信号

(

.clk (clk), //1MHz

.rst_n (rst_n), //复位

.m_axis_data_tdata (fm_mod_tdata), //调频波数据输出, output wire [16 : 0]

.m_axis_data_tvalid (fm_mod_tvalid),

.m_axis_data_tready (fm_mod_tready)

);

fm_demodulation_fir fm_u2 //调频波解调模块,将调频波解调还原调制信号

(

.clk (clk), //1MHz

.rst_n (rst_n), //复位

.s_axis_data_tdata (fm_mod_tdata), //调频信号输入 intput wire [16 : 0]

.s_axis_data_tvalid (fm_mod_tvalid),

.s_axis_data_tready (fm_mod_tready),

.m_axis_data_tdata (fm_demod_tdata), //调频波解调数据输出, output wire [16 : 0]

.m_axis_data_tvalid (fm_demod_tvalid),

.m_axis_data_tready (fm_demod_tready)

);

endmodule

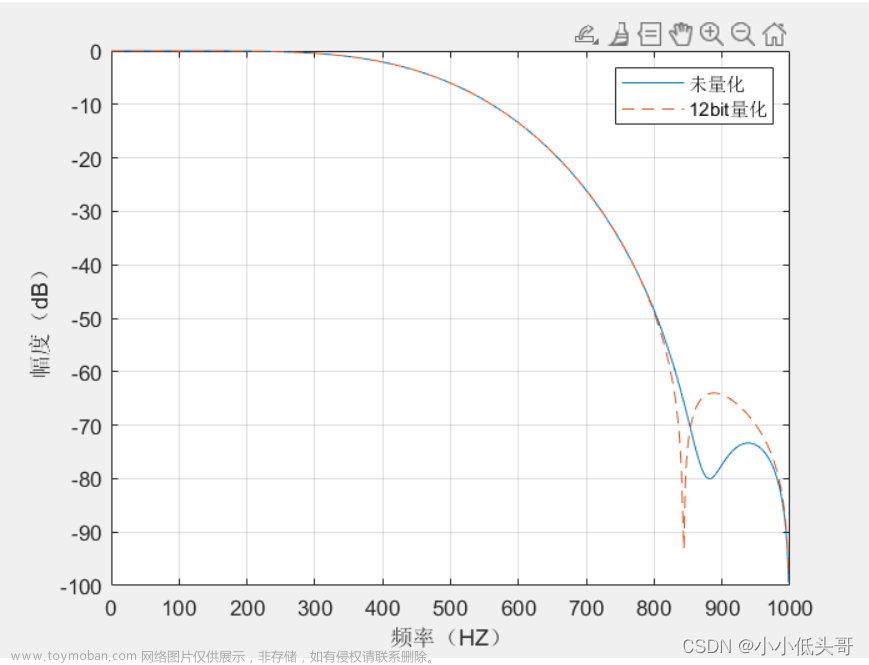

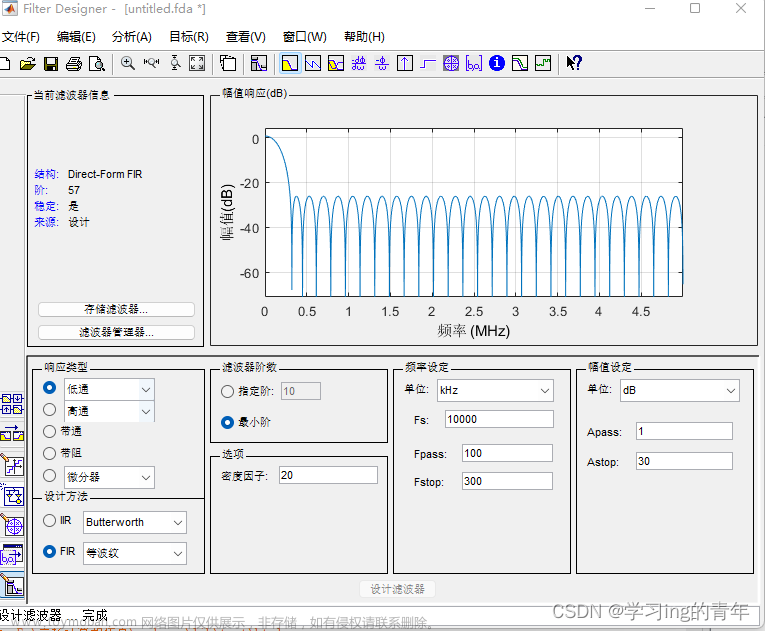

四、 FIR IP 设置

- 和上篇文章 FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波) 的设置一样,系数文件也一样,请参考这篇文章 FIR IP 配置这一章节

五、 DDS IP 设置

- dds_compiler_1m_4k IP设置和上篇文章 FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波) 的设置一样,请参考这篇文章 DDS IP 配置这一章节

1. dds_compiler_phase IP设置

六、 仿真时序波形图

1. 激励文件信号波形图

2. FM调频波调制模块信号波形图

3. FM调频波解调模块信号波形图

文章来源:https://www.toymoban.com/news/detail-481585.html

文章来源:https://www.toymoban.com/news/detail-481585.html

六、 综合布线后 FPGA 资源使用报告

文章来源地址https://www.toymoban.com/news/detail-481585.html

文章来源地址https://www.toymoban.com/news/detail-481585.html

七、 相关 vivado 工程、IP 设置等详细文档连接,采用 Xilinx vivado 2017.4 版本

-

XILINX FIR IP 详解、Verilog 源码、Vivado 工程

-

FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)详细介绍

-

FIR 基础应用 - FM 调频波调制解调(FIR 低通滤波) 详细介绍

-

FIR 中级应用 - AM 调幅波调制解调(FIR + FIFO)详细介绍

-

FIR 高级应用 - AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) 详细介绍

-

FIR 高级应用 - 多通道实验 (四个通道用一个 FIR IP,每通道用不同的系数) 详细介绍

-

FIR 高级应用 FIR Reload的使用) 详细介绍

-

AM 调幅波调制解调(FIR 低通滤波) vivado 工程文件下载

-

FM 调频波调制解调(FIR 低通滤波) Vivado 工程文件下载

-

AM 调幅波调制解调(FIR + FIFO) Vivado 工程文件下载

-

AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) Vivado 工程文件下载

-

FIR 高级应用 - 多通道实验 Vivado 工程文件下载

-

FIR 高级应用 FIR Reload 的使用 vivado 工程文件下载

到了这里,关于FIR 基础应用 - FM 调频波调制解调(FIR 低通滤波)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!