目录

学习目标

学习内容

1.设计方法学

2.设计实例

3.逻辑仿真实例

学习时间

总结

学习目标:

提示:这里可以添加学习目标

理解数字电路设计中自底向上和自顶向下的设计方法;

解释verilog中模块和模块实例之间的区别;

学习从4中不同的抽象角度来描述同一个模块;

解释仿真中的各个组成部分,定义激励块和功能块,说明两种激励进行仿真的方法。

学习内容:

提示:这里可以添加要学的内容

1.设计方法学

数字电路设计中两种基本的设计方法:自底向上和自顶向下的设计方法;

2.设计实例

下面以四位脉动进位计数器为例:

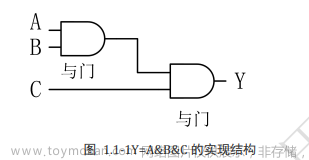

图中的脉动进位计数器是由下降沿触发的T触发器组成的.每个T触发器可以由下降沿触发的D触发器和反相器构成(假设D触发器的Q_bar端不可用),如图所示。

使用自顶向下的方法进行设计,首先需要说明脉动进位计数器的功能.在使用T触发器搭建起顶层模块之后,进一步使用D触发器和反相门来实现T触发器.这样我们就可以将较大的功能块分解为较小的功能块,直到无法继续分解.在自底向上的设计方法中,设计过程恰好与此相反:我们不断地使用较小的功能块来搭建大--些的模块.例如,在脉动进位计数器的例子中,我们首先使用与门和或门搭建D触发器,或者使用晶体管搭建一个自定义的D触发器,使自底向上和自顶向下的方法在D触发器这个层次上会合。

现在我们将层次建模的概念和 Verilog 联系起来。Verilog 使用模块( module〉的概念来代表一个基本的功能块。一个模块可以是一个元件,也可以是低层次模块的组合。常用的设计方法是使用元件构建在设计中多个地方使用的功能块,以便进行代码重用。模块通过接口(输入和输出)被高层的模块调用,但隐藏了内部的实现细节。这样就使得设计者可以方便地对某个模块进行觞改,而不影响设计的其他部分。

module<模块名>(<模块端口列表>);

<模块的内容>

endmodule

module T_FF(a, clock, reset)

使用Verilog既可以进行行为描述,同时也可以进行结构描述.根据设计需要,设计者在每个模块内部可以在4个抽象层次中进行描述,而模块对外显示的功能都是一样的,仅与外部环境有关,而与抽象层次无关。模块的内部结构对外部环境来讲是透明的。因此,对模块内部抽象层次的更改不会影响外部环境。本书将在后面的章节中对这些抽象层次分别进行叙述-这些抽象层次定义如下:

行为或算法级:Verilog所支持的最高抽象层次。设计者只注重其实现的算法,而不关心其具体的硬件实现细节。在这个层次上进行的设计与C语言编程非常类似。

·数据流级:通过说明数据的流程对模块进行描述。设计者关心的是数据如何在各个寄存器之间流动,以及如何处理这些数据。

·门级:从组成电路的逻辑门及其相互之间的互连关系的角度来设计模块。这个层次的设计类似于使用门级逻辑简图来完成设计。

Verilog 允许设计者在一个模块中混合使用多个抽象层次。在数字电路设计中,术语寄存器传输级(RTL)描述在很多情况下是指能够被逻辑综合工具接受的行为级和数据流级的混合描述。

假设一个设计中包含4个模块,Verilog 允许设计者使用4种不同的抽象层次对各个模块进行描述。在经过综合工具综合之后,综合结果一般都是门级结构的描述。

一般来说,抽象的层次越高,那么设计的灵活性和工艺无关性就越强;随着抽象层次的降低,灵活性和工艺无关性逐渐变差,微小的调整可能会导致对设计的多处修改。这就类似于使用C语言和汇编语言进行程序设计的对比。使用C这样的高级语言的好处是编码简单并且可移植性好;然而如果使用汇编语言,则需要针对特定的计算机,并且在移植到其他计算机上的时候可能会出现问题。

3.逻辑仿真实例

在设计完成之后,还必须对设计的正确性进行测试。我们可以对设计模块施加激励,通过检查其输出来检验功能的正确性。我们称完成测试功能的块为激励块。将激励块和设计块分开设计是一种良好的设计风格。激励块同样也可以用Verilog 来描述,而不必采用另外一种语言。激励块一般均称为测试台( test bench)。可以使用不同的测试台对设计块进行全面的测试。

激励块的设计有两种模式。一种模式是在激励块中调用(实例引用)并直接驱动设计块。顶层块为激励块,由它控制ck和reset信号,检查并显示输出信号q。

另一种使用激励的模式是在一个虚拟的顶层模块中调用(实例引用)激励块和设计块。激励块和设计块之间通过接口进行交互,。激励块驱动信号d_clk和d_reset,这两个信号则连接到设计块的clk和reset输入端口。激励块同时检查和显示信号c_q,这个信号连接到设计块的输出端口q。顶层模块的作用只是调用(实例引用)设计块和激励块。 另一种使用激励的模式是在一个虚拟的顶层模块中调用(实例引用)激励块和设计块.激励块和设计块之间通过接口进行交互,如图2.7所示.激励块驱动信号d_clk和d_Reset,这两个信号则连接到设计块的clk和Reset输入端口。激励块同时检查和显示信号c_q,这个信号连接到设计块的输出端口_q.顶层模块的作用只是调用(实例引用)设计块和激励块.

学习时间:

提示:这里可以添加计划学习的时间

周一到周五7点到9点,文章来源:https://www.toymoban.com/news/detail-481809.html

总结:

在本章中,我们讨论了下面的概念:

用于数字电路设计的两种方法:自顶向下方法和自底向上方法,在当今的数字电路设计中,这两种方法经常组合使用。随着设计复杂性的增加,使用这些结构化的方法来进行设计管理变得越来越重要。

模块是 Verilog 中的基本功能单元。模块通过调用(实例引用)来使用,模块的每个实例都被惟一标识,以区别于同-模块的其他实例。每个实例都拥有其模板模块的不同副本。读者需要将模块和模块实例区别开来。

仿真有两个不同的组成部分:设计块和激励块,激励块用于测试设计块。激励块通常是顶层模块。对设计块施加激励有两种不同的模式。

以脉动进位计数器为例一步步地解释了为各个部分创建仿真的过程。并且理解 Verilog语言如何适应这个设计流程。关于Verilog语言的详细语法,在目前阶段并不重要,以后会详细讲解这些内容。文章来源地址https://www.toymoban.com/news/detail-481809.html

到了这里,关于FPGA基础知识-层次建模的概念的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA] 7系列FPGA的基础知识](https://imgs.yssmx.com/Uploads/2024/02/484166-1.png)