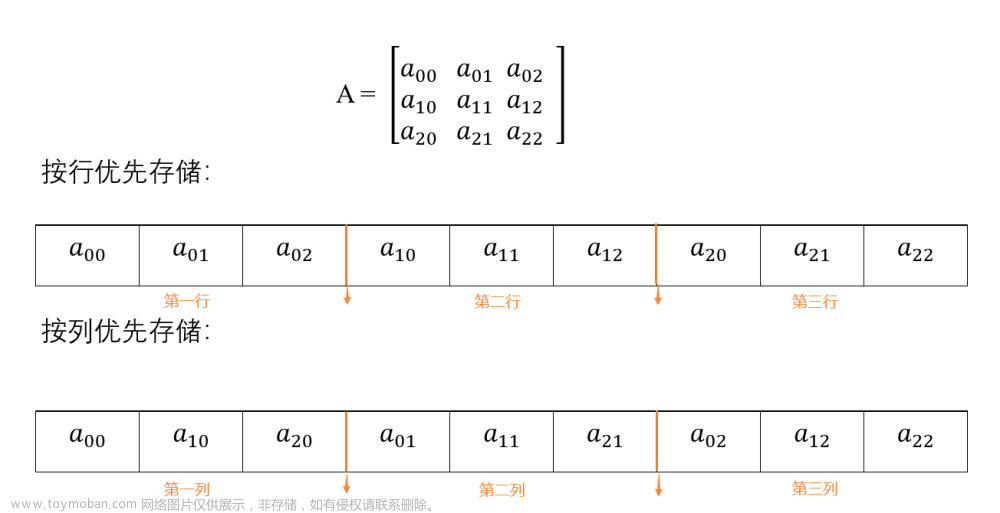

有两种表示方法:一种是verilog语法的多维数组,另一种是system verilog语法的多维数组。

这是verilog语法:

reg [A1:A0] a [B1:B0] [C1:C0] [D1:D0] ;

引用顺序是:a[B][C][D][A],

定义的a 的左边只有位宽,一对方括号[],a的右边可以扩展维数,多对方括号[],变化速度:B<C<D<A

这是system verilog语法:

packed维度:

packed数组是一种将1个向量细分为若干子字段的机制,这些子字段可以作为数组元素方便地访问;当一个打包数组作为主数组出现时,它将被视为单个向量。

多维矩阵是矩阵的矩阵,单个声明包含多个维度。标识符前面的设置packed维度。标志符后面的维度设置unpacked维度。

不管是packed还是unpacked,都是右边比左边变化快。

reg [A1:A0] [B1:B0] a [C1:C0] [D1:D0] ;

a[C][D][A][B],a的左右两边都可以扩展维数,变化速度:C<D<A<B文章来源:https://www.toymoban.com/news/detail-481850.html

standard-for-systemverilog文章来源地址https://www.toymoban.com/news/detail-481850.html

到了这里,关于【Verilog语法013】verilog多维数组(多维矩阵)的写法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!