教材:《计算机组成原理(第六版)》白中英等著

概述

电子计算机分类

- 电子模拟计算机

- 电子数字计算机=电脑

- 专用计算机:如嵌入式

- 通用计算机

- 超级计算机

- 大型机

- 服务器

- PC机

- 单片机

- 多核机 多于一个处理器的芯片

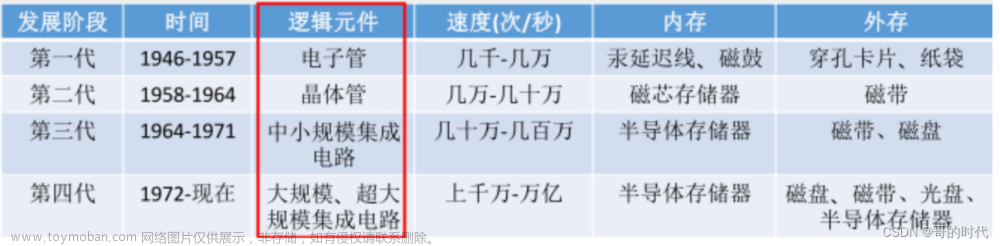

计算机的发展历史

第一代:电子管计算机 数据处理机 ENIAC EDVAC 冯·诺伊曼结构

第二代:晶体管计算机 工业控制机

第三代:中小规模集成电路计算机 小型计算机

第四代:大规模和超大规模集成电路计算机微型计算机

第五代:巨大规模集成电路计算机 单片计算机

存储器发展过程

铁磁体环

半导体存储器

微处理器发展历史

摩尔定律

计算机的性能指标(重点)

吞吐量:整体性能

响应时间:CPU执行时间+等待时间

- cpu执行时间=时钟周期数*时钟周期=指令条数 ∗ C P I ∗ *CPI* ∗CPI∗时钟周期

- CPU时间=用户CPU时间+系统CPU时间

处理机字长=机器字长:运算器一次整数运算处理的二进制位数

总线宽度:cpu中运算器与存储器之间互连的内部总线二进制位数

存储器容量

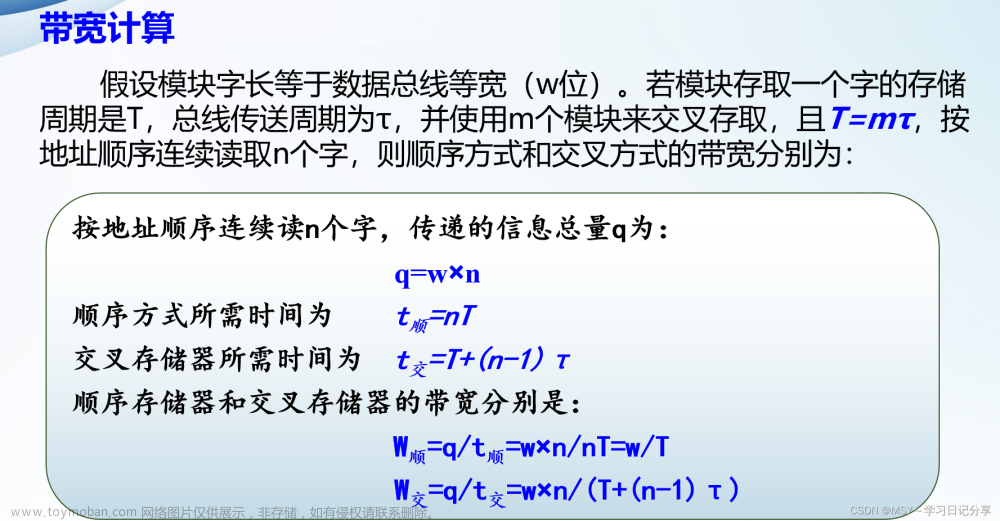

存储器带宽:单位时间内从存储器读出的二进制数信息量,单位字节数/s

主频:cpu工作频率

时钟周期:1/f,单位微秒

CPI(cycle per instruction)每条指令周期数:执行一条指令需要的平均时钟周期数

IPS(instructions per second)每秒执行指令数:MIPS:每秒执行百万条(million)定点指令数

FLOPS(floating-point operation per second):每秒执行浮点操作次数

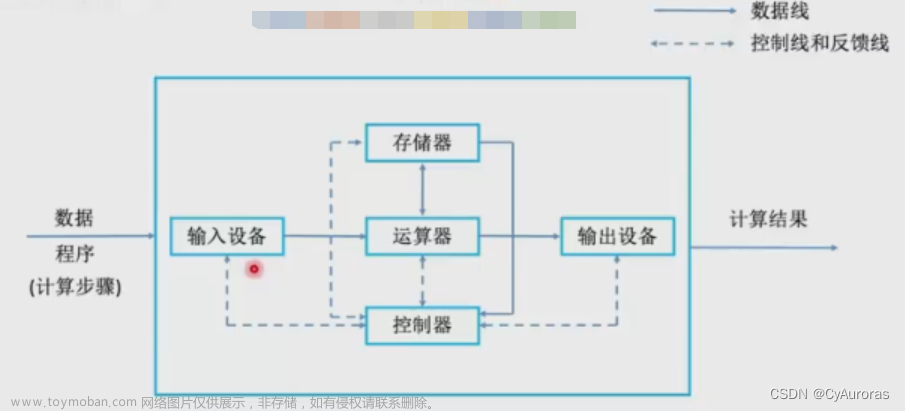

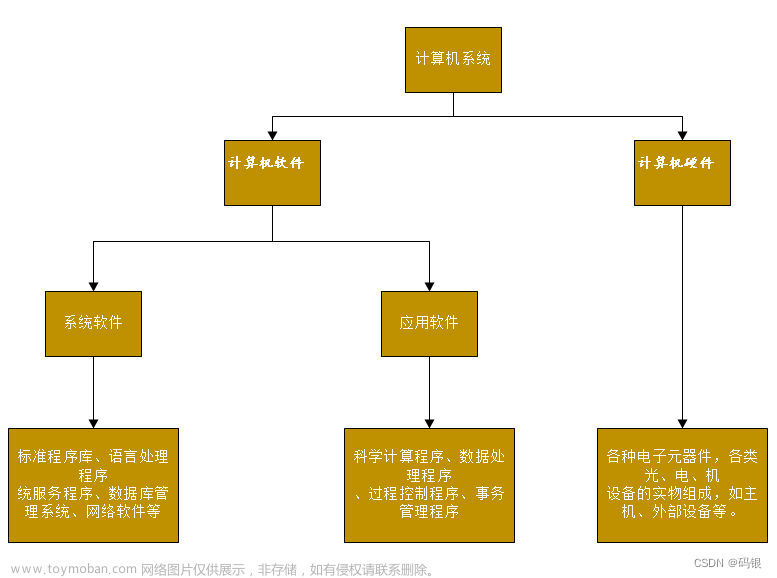

硬件组成

实际电脑:

主板

CPU

GPU(显卡)

内存

硬盘

网卡

散热器、风扇

电源

抽象术语:

- 运算器(alu):算术运算和逻辑运算,长度一般是8-64

- 控制器:指令:操作码+地址码->指令系统

取指周期+执行周期

指令控制,时序控制,总线控制,终端控制 - 存储器:由触发器构成,包括外存和内存

- 冯 诺依曼结构

- 哈佛结构

- 输入输出设备:需要适配器

- 总线

单位

位bit(b)

字节Byte(B)=8b

字word:8~64位,即1-8字节

数据的表示&运算

数据

数值数据

定点数

| 符号Xn | 尾数Xn-1 ~ X0 |

|---|

整数表示范围:

0

≤

∣

x

∣

≤

2

n

−

1

0\le |x|\le 2^n-1

0≤∣x∣≤2n−1

纯小数表示范围:

0

≤

∣

x

∣

≤

1

−

2

−

n

0\le |x|\le 1-2^{-n}

0≤∣x∣≤1−2−n

浮点数

| 阶符E | 阶码 | 数符M | 尾数 |

|---|

规格化浮点数:

尾数最高有效位为1,即0.1xxxx

原码:正数0.1xx 负数1.1xxx

补码:正数0.1xx 负数1.0xx

IEEE754

float(重点) 32位

( − 1 ) S ∗ ( 1. M ) ∗ 2 E − 127 (-1)^S*(1.M)*2^{E-127} (−1)S∗(1.M)∗2E−127

| 数符S | 阶码E(移码) | 尾数M(原码) |

|---|---|---|

| 1位 | 8位:0-255 | 23位(实际表示24位) |

数符:0正1负,表整个数的正负

阶码:E-127,真实表示范围为-127~128

尾数:隐含了首位的1,多存一位

正常范围:

1<=E<=254,真实范围是-126~127

因此数据表示范围是1e-38~1e38

尾数精度达不到阶码这么高

特殊情况:

E=0,M!=0,非规格化小数,隐藏位变为(0.M)

E=0,M=0,正负0

E=255,M!=0,NaN

E=255,M=0,

±

∞

\pm \infin

±∞

double 64位

| 数符S | 阶码E(移码) | 尾数M(原码) |

|---|---|---|

| 1位 | 11位:0-1024 | 52位(实际表示53位) |

十进制数串

要指明起址和长度

- 压缩的十进制数串 每个数位占半字节,用BCD码或ASCII码的低四位表示,正负号用冗余值中的相关值表示,如正C负D。数位加符号位之和必须是偶数,不为偶数需在最前面补零。

- 前分割数字串:

符号位:+ 2B - 2D

符号数据

字符

ascii码,8位,最高位是校验位

汉字(不考)

编码方式

原码

符号位 0正 1负

反码

正数和原码相同

负数将符号位以外的数位取反

补码

正数和原码相同

负数将符号位以外的数位取反再+1

考研速算:固定符号位,从右向左看第一个1不变,在它之前的数位取反

移码

常用于表示浮点数的阶码 +2^k

移码的符号位和上面的相反

校验码

奇偶校验:

奇数个1异或=1

偶数个1异或=0

优点:开销小,常用于检验一个字节长的数据

常用于:存储器读写校验、按字节传输过程中的数据校验,计算机网络

缺点:只能监测奇数或偶数个错误,无法定位错误位置

定点加减法(重点)

- 补码加法:

x补+y补=(x+y)补 mod 2^(n+1)

符号位要参与运算,溢出要舍弃 - 补码减法:

(x-y)补=x补-y补=x补+(-y)补

溢出判断

上溢,下溢

双符号位(变形补码):不同表示溢出,最高位始终表示正确的符号

标志位

阶码溢出

加法器

- 半加器

- 全加器

N位行波进位补码加法器(双高位判别)

need to be reviewed

定点运算器的构成(重点)

ALU(74181)+阵列乘除器+寄存器+多路开关+三态缓冲器+数据总线

后续复

ALU 算数逻辑运算单元(待学习)

基本构成是全加器

串行4个FA,构成4位ALU

需要先行进位发生器(CLA,Lookahead Carry Adder)

16位ALU需要片内先行进位,片间串行进位

单总线结构

把两个操作数输入到ALU需要两次,完成ALU计算任务需要三次串行选通操作

双总线结构

把两个操作数输入到ALU需要1次,完成ALU计算任务需要2次串行选通操作

三总线结构

完成ALU计算任务需要1次串行选通操作

浮点数加减

(都是在补码下的)

- 0操作数检查

- 对阶:小向大看齐,阶码增大,尾数右移(右规)

- 尾数求和

- 规格化:

向左规格化:00.0xxx或11.1xxx 不符合规格化,左移尾数,阶码减小

向右规格化,01.xxx或10.xxx 符号位不等,阶码+1,尾数右移,01补0,10补1 - 舍入处理:对阶或右规时尾数右移,低位被舍弃,需要舍入处理

- 四舍五入

- 朝0舍入

- 朝正无穷舍入

- 朝负无穷舍入

- 溢出处理:右规之后看阶码是否溢出

浮点运算流水线

实现时间并行性

流水线中各段的时间应该尽量相等

有装入时间和排空时间

具有k级过程段的流水线处理n个任务需要的时钟周期数为k+n-1

加速比:

n

∗

k

k

+

n

−

1

\frac{n*k}{k+n-1}

k+n−1n∗k

存储器

冯诺依曼架构以运算器为中心

以存储器为中心的计算机架构

分类

按存储介质

- 磁性材料:磁芯,磁带,磁盘

- 光存储器:光盘

- 半导体存储器:双极性,mos型(ram,rom)

- 其他:纸带

存取方式

- 随机 RAM random access memory

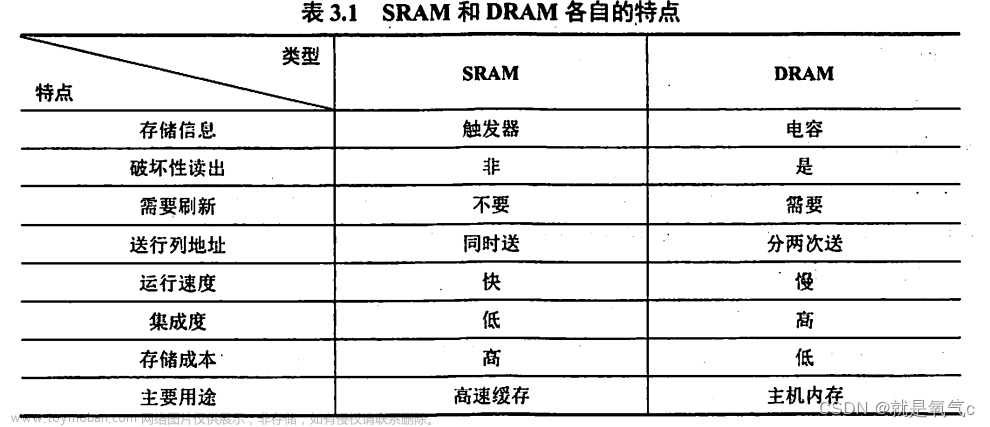

- SRAM 静态 static ->cache 更快,更贵

- DRAM 动态 dynamic->内存 一段时间必须刷新一次

- 顺序

- 串行访问存储器SAS(serial access storage)

- 顺序存取存储器SAM (sequential access memory)磁带

- 直接存取存储器DAM (direct access memory)磁盘

- 串行访问存储器SAS(serial access storage)

读写功能

- 只读存储器ROM(read only memory)(也可随机访问)

以前BIOS存在ROM上,现在在Flash上 - 随机访问存储器RAM=读写存储器

信息的保存性

- 永久 rom

- 非永久 ram

在计算机中的作用

- 主存 memory:RAM,ROM

- 辅存 storage:磁盘,固态,光盘

- 缓存 cache

- 控制存储器(存放微程序)

存储系统

cpu内:寄存器 多级cache

主板内:主存

主板外:磁盘 光盘

离线:磁带

端模式(不考)

大端:高字节放低地址端

小端:低字节放低地址端(常用)

ROM(read only memory)(也可随机访问)

非易失性,访问速度比RAM慢

在运行过程中只读,更新方式实际上是编程

分类

- 掩膜型 MROM masked

一次性的,厂家写入 - 可编程PROM programmable

- 可擦除可编程EPROM 用紫外线擦除

- 电可擦除可编程EEPROM

以上都不可在线改写内容

- 闪速存储器(闪存)Flash ROM 可在线改写内容

- NAND 与非门 非线性闪存 非随机访问 性能均衡 SD卡,U盘,SSD,容易坏

- NOR 或非门 线性闪存 接近传统ROM 放BIOS 可随机读出任意地址,读取速度高,写入慢

RAM

SRAM 静态随机存取存储器(重点)

用锁存器作为存储元

双译码方式

读周期:地址线有效->片选&读出使能有效->读出数据->撤销片选&使能->地址线改变

写周期:地址线有效->片选&读出使能有效->写入数据->撤销片选&使能->地址线改变

用作高速缓存 cache

DRAM 动态随机存取存储器(重点)

元件简化,会漏电,需要刷新,读出是破坏性的,需要刷新。需要额外的电路支持。

有刷新计数器,行地址锁存器,列地址锁存器,行、列使能端,读写使能端

分时传送地址码

读周期:地址线传行地址->行选通信号将其打入行地址锁存器->地址线传列地址->列选通信号将其打入列地址锁存器->行列地址译码&读出使能有效->读出数据

写周期:地址线传行地址->行选通信号将其打入行地址锁存器->地址线传列地址->列选通信号将其打入列地址锁存器->行列地址译码&写入使能有效->写入数据

刷新策略:

周期性刷新和读写操作交替进行,通过2选1多路开关实现

有片内刷新计数器自动生成地址来刷新

- 集中式刷新:一个刷新周期内,前一半正常读写,后一半集中刷新

- 分散式刷新:每一行的刷新操作被均匀分配的刷新周期内,逐行刷新

新型DRAM:

-

同步 SDRAM synchronous

-

快速页模式 FPM DRAM Fast Page Mode DRAM

根据局部性原理实现

允许在选定行的情况下,对每个列地址快速读写 -

高速缓冲 Cached CDRAM

在DRAM里放一个小容量的SRAM(cache),存放最后一次访问数据

更快的存储可以给较慢的作缓存 -

双倍速率 DDR DRAM double data rate

在时钟上升沿和下降沿都能传输数据

扩展

芯片数=要求容量/单片容量

注意DRAM的扩展,地址线只需要SRAM的一半,因为分时复用

位扩展

字数够,但位数不够,不满足字长。

地址线、控制线公用,数据线分高x位和低x位分别与两片IO端相连接,两片同时工作

画图

字扩展

位数够,扩充容量。地址总线和数据总线公用,读写信号线公用,由地址总线的高位译码产生片选信号,让各个芯片分时工作

画逻辑框图

字位扩展

并行存储器(不考)

时间:多模块交叉存储器

空间:双端口存储器

- 双端口存储器

两组独立的读写控制电路,无冲突读写控制,busy控制端防止写冲突 - 多模块交叉存储器

线性编址- 顺序方式

- 交叉方式 √

多模块流水式并行处理

τ = T / m \tau=T/m τ=T/m

cache(重点)

程序的局部性原理,多级cache

SRAM+控制逻辑(cpu提供,或主存/cache控制器提供)

命中率h

平均访问时间ta

访问效率e=tc/ta

cpu与cache 以字为单位传输

cache与主存 以块为单位传输

cache与主存的映射方式:

主存块对应cache行、槽

直接映射

主存块映射到cache的固定行中

| 主存标记(块群号) | cache槽号 | 块内地址 |

|---|

全相联映射

主存块映射到cache的任意行中

| 块号 | 块内地址 |

|---|

访问内存单元时先查cache中有无块号,如果miss则去内存里找

n路-组相联映射

主存块映射到cache的固定组的任意行中

| 标记 | 组号 | 块内地址 |

|---|

减少查找次数,但命中率低

失靶率和命中时间成负相关

替换策略

FIFO

LRU 计数器 命中行清零,其他+1

LFU 计数器 调出最小计数器的行,清零

随机替换Random

写策略

写回法:调出时才写回

全写法:分为WTWA和WTNWA法

写一次法

虚拟存储器(操作系统考了,不考)

固态硬盘SSD(考研考,不考)

指令系统

本节可在 汇编语言&微机原理 课程继续学习

指令集体系架构ISA(instruction set architecture)

指令集是存储在cpu内部,对cpu运算进行指导的硬程序

- CISC Complex Instruction set architecture 复杂指令集

指令数目多,字长不固定,一条指令包含很多内容,微程序控制 - RISC reduced Instruction set architecture 精简指令集

指令数目少,字长固定,硬布线控制

常见:

x86-16,x86-32(IA32),x86-64(x64)

IA64

MIPS,ARM,RISC-V,PowerPC

高级语言(宏指令)

汇编语言

机器指令——指令 √

微程序

伪指令

微命令

微操作

完备性,有效性,规整性,兼容性

指令格式

指令=指令字=包含一条指令的机器字

| 操作码字段OP | 地址码字段A |

|---|

地址码

三地址指令 A3是结果地址 通常三个都是通用寄存器里的地址

| OP | A1 | A2 | A3 |

|---|

二地址指令(常见) A1既是操作数又是存放结果的地址

| OP | A1 | A2 |

|---|

SS存储器-存储器

RS寄存器-存储器

RR寄存器-寄存器

一地址指令 指定一个操作数,另一个隐含,结果隐含

| OP | A1 |

|---|

零地址指令 无需操作数或隐含在寄存器中,如HALT信号,return,clear

| OP | 空 |

|---|

为了保证等长,操作码会占用消失的地址码长度,但实际上指令也没有那么多,高位可能会占一些无意义的东西

操作数类型:

- 地址数据

- 数值数据

- 字符数据

- 逻辑数据

指令字长度

一个指令的位数

单字长指令:指令字长度=机器字长

半字长指令

双字长指令

多字长指令

等长指令字结构(现代多用)

变长指令字结构

取值-》译码-》取操作数-》执行-》存结果-》下一条指令

典型指令:

数据传送

算术运算

逻辑运算

程序控制

输入输出

字符串处理

特权

其他

寻址方式

指令寻址

顺序寻址

程序计数器PC累加

跳跃寻址

数据寻址

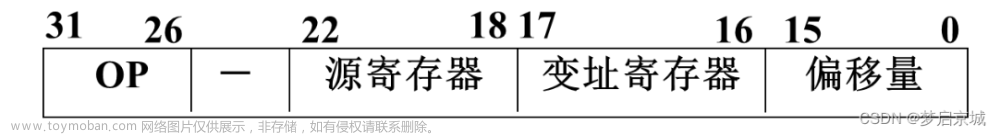

| OP | 变址X | 间址I | 形式地址A(偏移量) |

|---|

如果无间址和变址,则形式地址就是有效地址

如果有,需要地址变换,这就是寻址过程

隐含寻址

隐含了累加器作为目的寄存器

立即寻址

地址字段给的是操作数本身,立即数

直接寻址(绝对寻址)

不需要变换直接寻址

间接寻址

间址I=0 直接寻址

间址I=1 间接寻址 两次访存

寄存器寻址

- 寄存器直接寻址

- 寄存器间接寻址 寄存器里的东西不是操作数而是内存地址

偏移寻址

直接寻址+寄存器间接寻址

相对寻址 PC

基址寻址 基址寄存器

变址寻址 变址寄存器

段寻址

堆栈寻址

寄存器堆栈

存储器堆栈

中央处理器CPU(central processing unit)

功能:指令控制,操作控制,时间控制,数据加工

包含

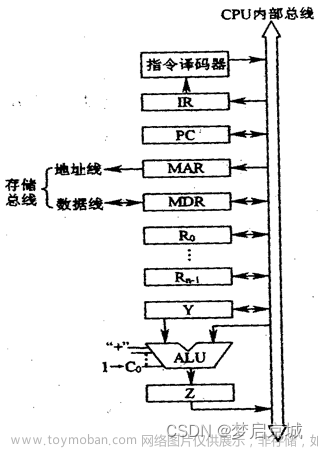

- 运算器:ALU(Arithmetic Logic Unit)算数逻辑单元+通用寄存器+数据缓冲寄存器DR+程序状态字寄存器PSWR

- 控制器:程序计数器PC+指令寄存器IR+指令译码器+时序产生器+操作控制器OC

- 外部逻辑功能部件集成:浮点运算器,cache,总线仲裁器

cache包括地址寄存器AR,数存,指存

从cache的指存中取指令(取哪条是从程序计数器PC中通过地址总线ABUS取出指令地址,PC++),送到控制器的指令寄存器IR,指令分为操作码和地址码,把操作码送给指令译码器,把地址码通过地址总线送给地址寄存器AR,同时译码成功,时序发生器和操作控制器产生控制信号,通过数据总线DBUS在cache的数存中取数据放到运算器的数据打入ALU,ALU计算出结果放入数据缓冲寄存器,之后送到相应的地方,检测异常,处理异常,处理中断,进入下一条指令

寄存器:

数据缓冲寄存器DR 用来暂时存放ALU的运算结果

指令寄存器IR 用来保存从指存中读出的数据

程序计数器PC program counter=指令计数器

数据地址寄存器AR 保存当前访问数存的地址

通用寄存器 有64个,为ALU提供工作区

程序状态字寄存器PSWR program state word register

操作控制器

硬布线

微程序

指令周期(重点)

指令周期由若干机器周期=CPU周期组成,机器周期又由时钟周期(节拍)组成

指令周期可能包含取指周期,间址周期,执行周期,中断周期(最全版)

单CPU周期:在一个时钟周期内完成指令所有工作

多CPU周期:√

取指,间址,执行,中断

MOV

MOV R0,R1 是RR指令

- 取指需要一个CPU周期

从指存中取指

PC++

对指令操作码进行译码 - 执行需要一个CPU周期

- 控制信号控制R1作为源寄存器,R0作为目标寄存器

- ALU传送,计算

- ALU将结果输出到数据总线上

- 打入数据缓冲寄存器

- DR打入目标寄存器R0

LAD

LAD R1,6

RS,三个CPU周期,一次访问指存,一次访问数存

ADD

ADD R1,R2

RR 两个cpu周期

STO

STO R2,(R3)

RS 三个CPU周期

JMP

JMP 101

1个CPU周期

AND

AND R1,R3

用方框图表示指令周期

操作控制器

有时钟,控制单元CU,标志,指令寄存器

硬布线

逻辑电路

微程序控制器(重点)

微指令:操作控制+顺序控制,字长可为32位

每位代表一个微命令

微程序控制器:控制存储器+微指令寄存器(微地址寄存器+微命令寄存器)+地址转移逻辑

好东西

直接表示法

编码表示法

混合表示法

微地址的形成方式

多路转移方式

计数器法方式

微指令格式

水平型微指令

垂直型微指令

流水cpu

并行的三种:时间、空间、两个都(超标量流水线)

组成:

指令流水线(指令部件)

指令队列

运算流水线(执行部件)

n条指令需要时间:t=4+n-1

流水线分类:

算术流水线

处理机流水线(宏流水线)

指令流水线

主要问题:

资源相关

数据相关:写后读,读后写,写后写

控制相关

为减小转移指令的影响,常用两种技术:延迟转移法,转移预测法

总线

分时,共享

总线由适配器(接口,adapter)构成

常见:ISA,EISA,VESA(video electronics standard association),PCI(Peripheral Component Interconnect,“外围器件互联”),PCI-E(pci-express),AGP(Accelerated Graphics Port,图形加速端口),RS-322,USB(Universal Serial Bus,通用串行总线),SCSI(small computer system interface),SATA(serial advanced technology attachment)

总线功能:传输指令,数据,io操作

接口功能:控制、缓冲、状态、转换、整理、程序中断

分类

片内总线(cpu内)

系统总线(cpu外部,主板内)

通信总线(io总线)

结构(重点)

桥,具有缓冲、转换、控制功能的逻辑电路

地址线、数据线、控制线

单总线

一根总线连cpu,内存和io设备

双总线

cpu和主存专门一套(系统总线)

三总线

在双总线系统上增加IO总线

cpu总线-北桥-pci总线-南桥-isa总线(比较老旧的版本了,现在也不用了)

传送方式:

串行(pcie),并行(pci),分时传送

性能指标

总线宽度:数据线的根数

总线带宽:数据传输速率 MBps million Byte per second

时钟:同步、异步

总线复用:地址线与数据线是否复用

信号线数

总线控制方式:链式、计数、独立

总线仲裁(重点)

集中式仲裁

链式查询方法:菊花链查询,计数器定时查询,独立请求方式

分布式仲裁

以优先级仲裁策略为基础,多个仲裁器竞争使用总线,获胜的仲裁号保留在仲裁总线上

总线定时

信息传送过程分为五个阶段:请求总线,总线仲裁,寻址,信息传送,状态返回

定时:事件出现在总线上的时序关系

- 同步定时

- 异步定时 典型的是网络传输 TCP/IP

非互锁,半互锁,全互锁(三次握手,网络)

总线数据传送模式

- 读写操作

- 块传送操作

- 写后读,读-修改-写操作

- 广播、广集操作

外围设备

磁盘(机械硬盘)

存储介质,驱动装置,控制电路

磁头:可移动、固定(一个磁道对应一个磁头)

盘片:可换、固定

温彻斯特盘(温盘)是一种可移动磁头固定盘片的磁盘机

盘面(一个磁盘有两面),磁道,扇区,柱面,块block/簇bluster

一个扇区:头空+序标+数据+校验字+尾空、

T=寻道时间+旋转等待时间+数据传输时间

Ta=Ts+1/2r+b/rN

数据传输率Dr=旋转速度*磁道容量 (字节/秒)

地址格式

| 台号 | 柱面号(磁道号) | 盘面号(磁头号) | 扇区号 |

|---|

性能指标

存储密度:道密度,位密度,面密度

存储容量:面密度+记录面数

注意:磁盘的单位进制是1000而不是2e10

磁盘阵列RAID(redundant arrays of independent disks)

独立磁盘冗余阵列

0:数据分布在阵列所有的磁盘上,速度快,不安全

1:备份,利用率50%,可靠性高

5:奇偶校验块分布在各个盘中

不考的:

2:海明校验法,冗余盘存校验码

3:奇偶校验盘(一个)

4:奇偶校验盘(一个)

6:冗余分布在所有磁盘上,数据以块交叉方式存放

7:带cache

光盘和磁光盘

显示设备

CRT,LCD,等离子体

输入输出系统

统一编址方式,IO独立编址方式

IO接口与外设之间的数据传送方式:

- 无条件传送方式

- 应答方式(异步传送方式)网络中常见

- 同步传送方式(和cpu时钟周期同步)

cpu与IO接口之间的传送方式

- 无条件传送方式

- 程序查询方式(轮询)

- 程序中断方式

- 直接内存访问方式(DMA)

- 通道方式

常用IO标准接口:SCSI,IEEE1394

程序查询方式

置1或置0,测试设备的状态,传送数据

程序查询接口:设备选择电路,数据缓冲寄存器,设备状态标志

限制:cpu在查询时不能做其他工作&不能实时数据交换,可能造成丢失

程序中断方式

外围设备主动告诉cpu中断

中断源:握手联络,故障处理,实时处理,程序调度,软中断(打断点)

响应中断时机:在cpu执行当前指令完毕后转入公操作

断点保护

原子操作:开中断和关中断问题

单级中断:串行排队链法

多级中断:挂起入栈

DMA方式(direct memory access)

通过硬件实现主存与IO设备的直接数据传送,数据交换不经过CPU而在内存和设备之间进行,不需要保护现场

需要在主存中有专用缓冲器

在数据传输前后需要用中断对缓冲器和DMA控制器进行预处理和后处理

- 成组连续传送方式=cpu暂停方式

- 周期挪用方式(cpu暂停工作一个周期)

- DMA和cpu交替访问内存工作方式

选择型和多路型DMA控制器

以上三种方法都需要CPU的介入,都需要接口硬件支持文章来源:https://www.toymoban.com/news/detail-482167.html

通道方式

一种特殊的处理机

选择通道

多路通道文章来源地址https://www.toymoban.com/news/detail-482167.html

到了这里,关于计算机组成原理 期末提纲的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!