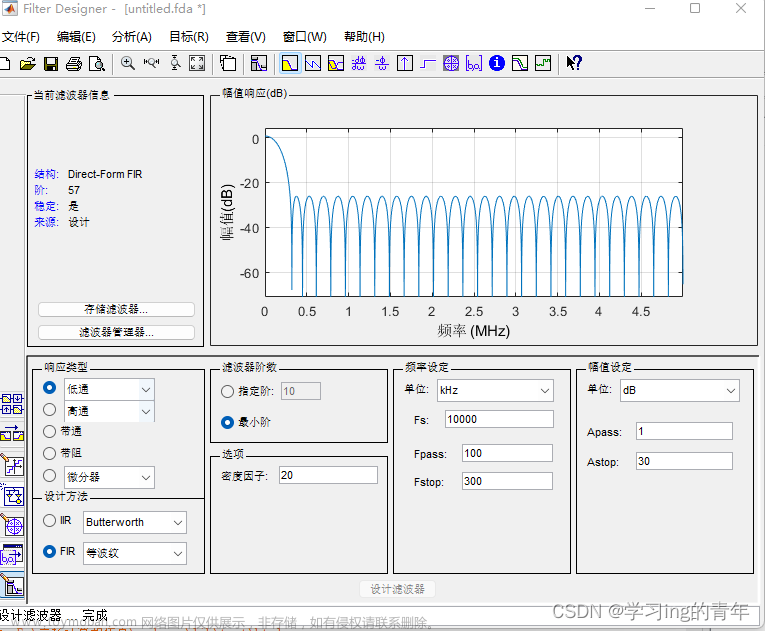

有限脉冲响应(finite impulse response,FIR)数字滤波器

一、FIR数字滤波器理论介绍

FIR滤波器的实质就是输入序列与系统脉冲响应的卷积,即:

其中,N为滤波器的阶数,也即抽头数;x(n)为第n个输入序列;h(n)为FIR滤波器的第n级抽头系数。

FIR滤波器基本结构如下:

FIR数字滤波器的基本结构有直接型、级联型、频率抽样型。

二、运用FPGA实现FRI滤波器的几种结构

2.1串行结构

由FIR滤波表达公式可以看到,其实质是乘法和累加运算,其滤波器的阶数N决定了乘法和累加运算的次数。

串行结构使用1个乘法器和1个加法器,每个时钟计算1次乘法和加法,需要计算N次(N为阶数)。结构图如下:

图中标注乘法结果、累加结果处,可以根据FPGA设计增加D触发器,进行节拍处理。当处理完N阶的累加后,累加结果即为有效的y(n)。

串行结构的FIR滤波器需要非常多的时钟周期才能获得一个序列值得滤波结果,处理速度非常慢,适用于滤波阶数比较低或者处理速度要求低的场景。

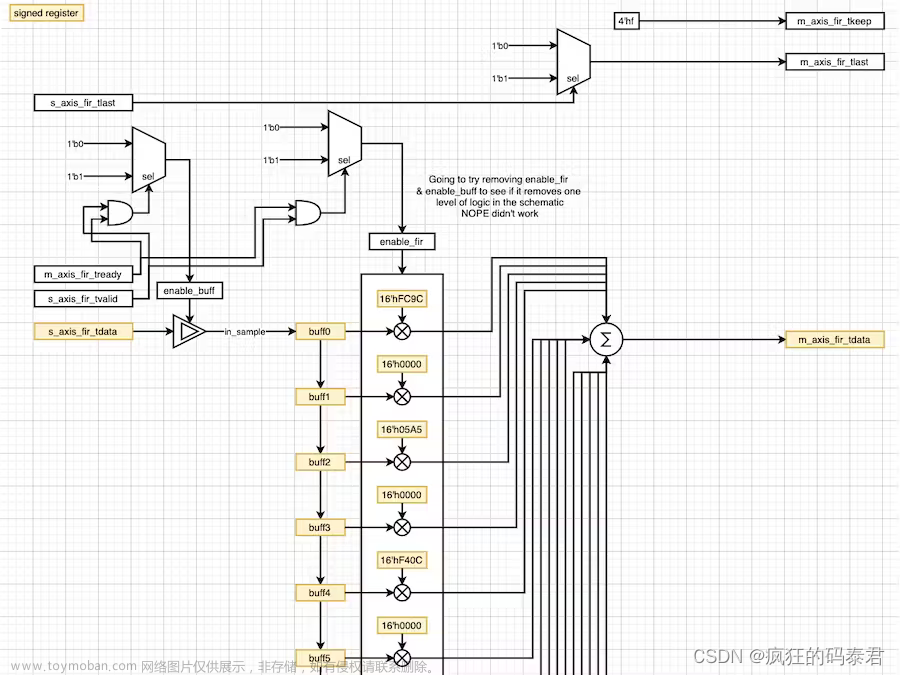

2.2 并行结构

在串行结构的基础上,增加乘法器和加法器的数量,得到并行的FIR滤波器结构如下,可以同时进行多个系数的乘法和加法运算,增快FIR运算速度。

由于FIR滤波器系数h(n)具有对称性,因此可以先进行1次加法,再进行乘法运算,最后再将所有的乘法运算结果进行相加,这样可以减少乘法器的使用数量。得到如下的架构:

并行结构又称为直接型FIR滤波器结构,如上图所示。用多个加法器和乘法器并行实现,可以达到1个时钟周期输出1个y(n),使用资源角度。N阶的滤波器,需要使用到N/2个乘法器。

2.3转置型结构

先回顾一下转置定理:如果将源网络中所有的支路方向加以反转,支路增益保持不变,并将输入x(n)和输出y(n)相互交换,则网络的系统函数不会改变。

根据转置定理,将上述所说的并行结构进行转置。以下以4阶FIR滤波器介绍转置型结构的由来。

转置定理转换:

A.并行结构初始形态

在硬件设计中,加法器可以看成信号的叠加,也可以表述成下图:

B.按照转置定理,将所有支路信号方向反转,输入输出位置互换。

信号叠加处,使用加法器表示如下:

C.转化成输入在左,输出在右的结构

另一种转换方式:

A.并行结构初始形态

四阶并行结构图如上所示,编写乘数学公式如下:

B.改变y(n)位置

此时y(n)的表达式不变,依旧是:

C.改变延时单元位置

此时直观上,y(n)的表达式发生了变化。但是经过转换:

可以发现,y(n)表达式不变

D.按照阅读习惯,将输出放在右侧。

可以发现,y(n)表达式不变

上图即为转置后的滤波器结构。

由此引申出转置示波器结构如下:

转置FIR滤波器相比较于并行FIR滤波器,不需要给输入信号x(n)提供额外的节拍寄存器,在执行乘法器累加时,一般考虑到时序路径问题,会对乘法结果打一个节拍,作流水线处理(因转置结构中刚好在乘法器后包含一个延时寄存器,这样就无需额外增加流水线寄存器),对于时序的优化具有帮助。即转置FIR滤波器相比较并行FIR滤波器,具有更小的延迟,且能节省FPGA资源。

并行结构和转置结构,实质是同一种结构,只是运算顺序发生了变化而已。其又称为横截型、卷积型或者直接型结构。

2.4 基于FFT的结构

已知输入与输出之间的关系是,其频域上的关系为Y(w)=X(w)H(w)。快速傅里叶变换FFT可以快速实现信号的时序频域转换,如下图:

文章来源:https://www.toymoban.com/news/detail-482462.html

文章来源:https://www.toymoban.com/news/detail-482462.html

在FFT的滤波结构中,通过频域的乘法得到输出信号的频域函数,再利用快速傅里叶反变换,还原时域信号,即目标信号y(n)。文章来源地址https://www.toymoban.com/news/detail-482462.html

到了这里,关于解析使用FPGA逻辑实现FIR滤波器的几种架构的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!