Aurora 8b/10b,官方提供了demo工程,但是数据生成模块、Aurora IP核、数据校验模块之间并不是直接使用AXI4-ST总线通信,本文会将demo工程进行相关优化修改,并将优化修改后的demo工程进行仿真、分析、说明:

1 IP核设置

例化Aurora 8b10b IP核,lane的数据位宽选2字节,速率选1.25Gbps,GT参考时钟125MHz,INIT时钟和DRP时钟均选50MHz。

这里我们的开发板上有两个光口,仅使用1个光口(1条Lane)进行内部自环测试、以及两块A7开发板的回环测试;如果使用同一块开发板上的2个光口做回环测试,首先要确认使用光模块连接后的两个光口的TX和RX是如何对接的,另外还需要考虑通信数据的高字节与低字节顺序问题。

这里我们不搞这么复杂,直接用1个光口做内部自环测试、两块A7开发板的光口回环测试。

设置的是用1条Lane(Lane0和Lane1),单条Lane的数据位宽是2Bytes,通信数据位宽1*2Bytes = 16bits。

这里计算一下Aurora提供的USER_CLK,线速率 * 8b10b / lane的位宽 = 1.25Gbps线速率 * (8/10) / 16 = 62.5MHz

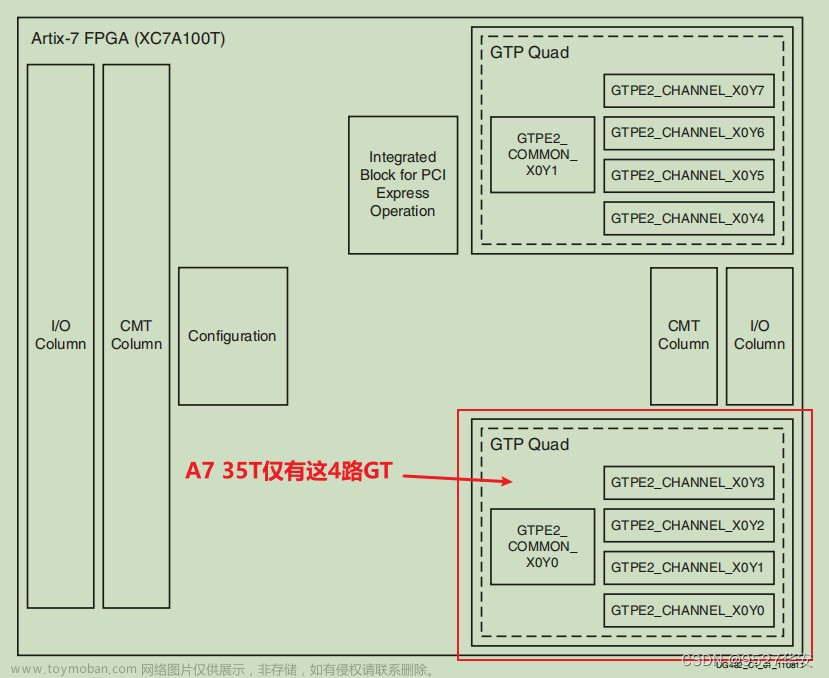

做仿真测试使用了1条Lane,例如选择了X0Y0这1条Lane:

Transceiver quad PLL、differential refclk buffer、clocking和reset逻辑包含在IP core中,我们用开发板上的50MHz单端晶振时钟给INIT CLK用,所以这里INIT CLK设置为单端:

2 IP核接口设置

2.1 Framing接口

IP核设置中选择的是Framing接口

2.2 Streaming接口

2.3 AXI4-Stream数据大小端

Aurora IP核默认按照MSB大端模式传输数据:

可以在IP核中设置小端模式:

3 官方demo工程分析及优化

3.1 demo仿真工程结构

demo工程中主要包含如下几个模块:

(1) aurora_8b10b_0_exdes.v

demo工程的顶层

(2)aurora_8b10b_0_frame_gen

数据帧生成模块,对外使用ll接口

(3)aurora_8b10b_0_ll_to_axi_exdes

ll接口 —> aurora_8b10b IP核1 axi4-st tx

(4)aurora_8b10b_0.xci

Aurora 8b10b IP核,demo工程中例化了2个Aurora IP核,IP核1的axi4-st tx —> IP核1的tx —> IP核2的rx —> IP核2的axi4-st rx

(5)aurora_8b10b_0_axi_to_ll_exdes

aurora_8b10b IP核2 axi4-st —> ll接口

(6)aurora_8b10b_0_frame_check

数据帧校验模块,对外使用ll接口

(7)tb

TB中例化了双份demo工程:

例化的两个demo做了回环配置,每个demo都是1条Lane。

3.2 demo仿真工程优化

由于demo工程中多的两个总线转换模块(aurora_8b10b_0_ll_to_axi_exdes和aurora_8b10b_0_axi_to_ll_exdes),分析起来有些冗余,我们对demo工程进行优化测试,这里省去这两个总线转换模块。将原先的数据流:aurora_8b10b_0_frame_gen —> aurora_8b10b_0_ll_to_axi_exdes —> aurora_8b10b_0.xci —> aurora_8b10b_0_axi_to_ll_exdes —> aurora_8b10b_0_frame_check,改为:aurora_8b10b_0_frame_gen —> aurora_8b10b_0.xci —> aurora_8b10b_0_frame_check。数据流直接采用AXI4-ST进,AXI4-ST出。测试结果:

进Aurora的数据,与出Aurora的数据进行对比校验,无误。

这里我们重点分析改写后的aurora_8b10b_0_frame_gen模块和aurora_8b10b_0_frame_check模块。

3.2.1 aurora_8b10b_0_frame_gen

(1)我们通过状态机控制Framing接口的s端:

(2)帧长从8'h01累加至8'hff,第8'h01帧包含1个16bit数据。。。第8'hff帧包含8'hff个16bit数据:

(3)使用种子值16'hABCD,按照下图中的计算公式产生测试用的伪随机数16位的data_lfsr_r:

(4)将16位的伪随机数赋给16位的AXI4-ST数据:

Aurora IP初始化完成产生CHANNEL_UP信号后,使用USER_CLK做了5'h1f * USER_CLK的复位延时。

3.2.2 aurora_8b10b_0_frame_check

(1)我们通过状态机控制Framing接口的m端:

(2)将接收到的AXI4-ST数据,与计算的伪随机数w_random_data进行对比,检验二者是否一致。

注意:Aurora 8b/10b的初始化时间无法修改,每次仿真需要等到初始化完成(CHANNEL_UP拉高)之后才能正常通信,这个耗时相对较长,仿真一次差不多15min左右;如果例化的是2条Lane,那么仿真的时间会相应的增加。

3 上板调试

3.1 单板自环测试

(1)Near-End PMA

(2)Near-End PCS

3.2 两块板卡回环测试

将两块板卡的光口用光模块进行互联,设置loopback为非自环模式,在线调试结果校验无误。

(1)板卡1

(2)板卡2

文章来源:https://www.toymoban.com/news/detail-484010.html

文章来源:https://www.toymoban.com/news/detail-484010.html

3.3 调试小结

frame_gen S端的AXI4-ST总线信号中,valid、ready、last右边沿需要保证对齐,否则会导致frame_check M端接收到的AXI4-ST数据与生成的伪随机数校验错误。文章来源地址https://www.toymoban.com/news/detail-484010.html

到了这里,关于Aurora 8b/10b AXI4-ST回环测试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!