简单介绍

赛普拉斯将CYUSB3014简称为EZ-USB FX3,该芯片用于USB3.0的外设控制。

FX3有一个用于并行传输的通用接口:GPIF II。该接口可以与FP GA直接连接。

FX3功能及其强大,它集成了USB3.0 PHY物理层还有ARM核,i2c,uart等。

FX3主要功能是传输USB主机与外设之间的数据,可实现对高带宽数据的传输。

接口介绍

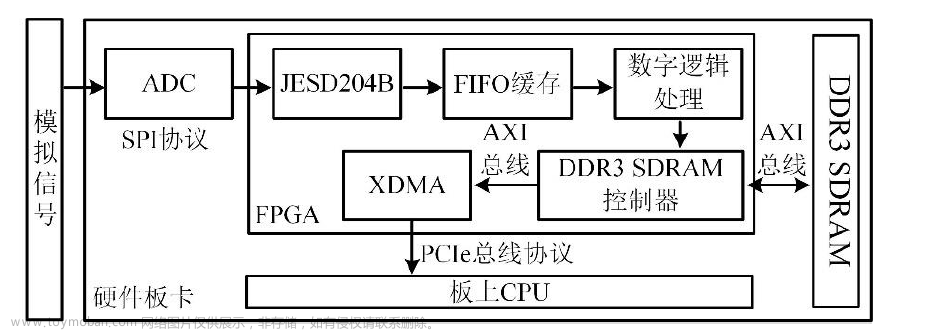

如图就是与FPGA,PC端的连接示意图。通过GPIF II接口的实现实例是异步和同步从器件FIFO的接口。如下图所示。FX3相当于是FPGA与上位机之间的桥梁,FX3内部会将收到的数据打包成usb3.0协议的数据包。

如图就是与FPGA,PC端的连接示意图。通过GPIF II接口的实现实例是异步和同步从器件FIFO的接口。如下图所示。FX3相当于是FPGA与上位机之间的桥梁,FX3内部会将收到的数据打包成usb3.0协议的数据包。

接口频率可高达 100 MHz。提供 256 种固件可编程状态 。支持 8 位、16 位和 32 位并行数据总线。

对上图接口功能简单介绍:D是32bit数据线,A是选择用内部的哪个缓冲区,每个缓冲区16kb

上图是同步读FIFO 时序图(FPGA读FX3),当SLRD#有效延迟的两个周期数据输出。SLRD#是FIFO读使能,这个使能的开启一定非空,通过FX3的输入信号来判断是否为空,这个信号就是flaga,只有当FX3输出了有效信号,才可以使SLRD#有效。

从FIFO中的地址读出数据到总线延迟三个周期。即片选有效以后的三个时钟周期以后数据才会出现在总线上。

当FLAGA拉低证明FIFO读空,该信号与SLRD#延迟两个时钟周期。

同步读和异步读的区别:同步读的FIFO指针是跟着时钟上升沿变的。而异步读FIFO的指针是随着SLRD#从有效至无效变化的。

上图是同步写数据时序图。

PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输。

当SLWR#有效时,在时钟上升沿数据被写入FIFO.在vivado写的时候可以认为写使能和数据是同时的不需要提前拉起(和一般fifo一样)。文章来源:https://www.toymoban.com/news/detail-484918.html

---------------------------------------------------------------------------------------------------------------------------------文章来源地址https://www.toymoban.com/news/detail-484918.html

到了这里,关于FPGA与CYUSB3014实现USB3.0数据传输学习笔记(1)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!