参考教材:数字电路与逻辑设计(第2版)邬春明

目录

1. 边沿触发器(D触发器)

2. 时序电路描述/构成

3. 时序逻辑电路的功能描述方法

1. 边沿触发器(D触发器)

组合逻辑电路掌管了电路中的逻辑运算,基本单元是与或非门。而时序逻辑电路则掌管了电路中数据的存储。触发器就是构成时序逻辑电路的基本单元。

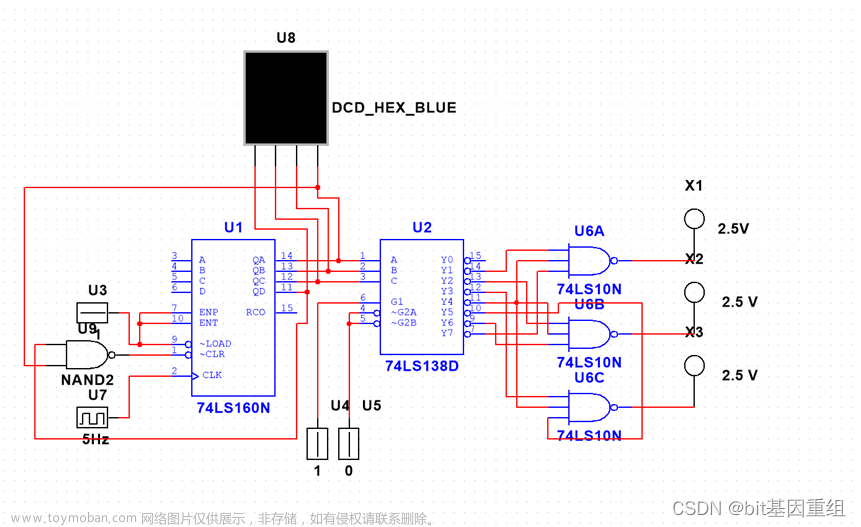

D触发器是最常用的触发器,其中主要信号如下图。

RD非,SD非分别是异步复位和异步置位信号。异步的意思就是不管CP(时钟脉冲),直接可以决定输出Q,两个都是低有效信号,分别为0的时候,Q分别为0(被R复位)和1(被S置位)。只有当RD非和SD非都为1的时候,D触发器才能正常运转,D触发器又称为跟随触发器,输出跟着输入走(当CP上升沿到达的时候判断)。

2. 时序电路描述/构成

组合逻辑电路的输出只与输入有关,而如果将部分输出迁回去作为部分输入,那么输出就不仅与输入有关,还与原来的状态(原来的输出)有关,这就变成了时序逻辑电路。

Qn+1不仅与X有关,还与Qn有关,这就是时序逻辑电路

时序逻辑电路的分类:

按照触发器变化是否同步分为了同步时序电路和异步时序电路。同步时序电路中的触发器都跟随时钟同步变化,而异步时序电路中没有统一的时钟。

已知时序电路的输出与上一状态有关,那么再根据是否与输入有关又可以分为米里型(Mealy)和摩尔型(Moore)。米里型与输入有关,而摩尔型与输入无关(记忆:摩尔型的输出与尔等输入无关)。

3. 时序逻辑电路的功能描述方法

已知组合逻辑电路可以通过五种方式来描述其功能,分别是逻辑表达式,真值表,电路图,卡诺图,波形图。而时序逻辑电路则有逻辑表达式,波形图,状态迁移表,状态转移图。

状态转换表每一行对应了一个状态的转换。x和Qn是输入和现态,Qn+1和Y是次态和输出。

状态表和状态转移表大同小异。

状态图是通过一种可视性强的方法来描述状态的转化。

总结:文章来源:https://www.toymoban.com/news/detail-485899.html

数字电路的知识中,掌握上述部分已经足够应对后续的知识。后面会根据学习的深入再进行补充。文章来源地址https://www.toymoban.com/news/detail-485899.html

到了这里,关于IC验证必备的数字电路基础知识(三):时序逻辑电路的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!