目录

一、题目

二、时钟发生电路

1、施密特触发电路

2、单稳态电路

3、多谐振荡电路

三、 N进制计数器

1、M的情形<>

2、M>N的情形

2、1 193实现

2、2 192实现

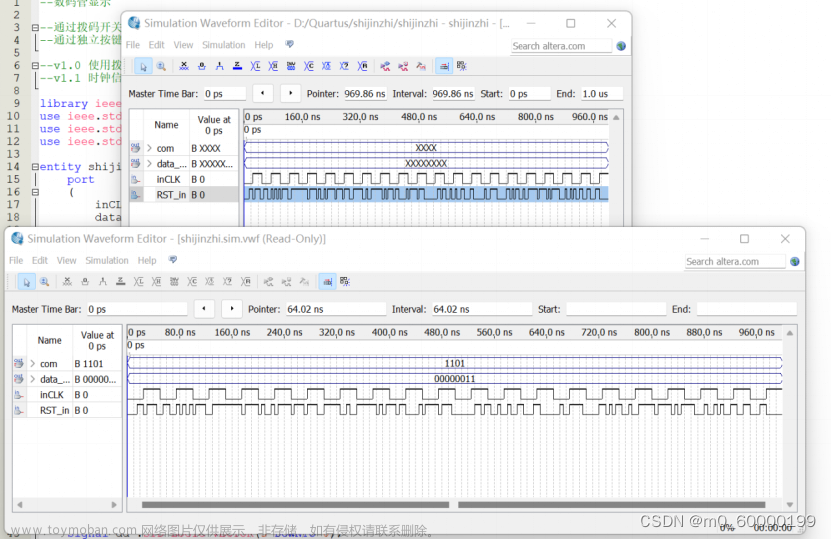

四、设计的小bug

1、两个bug

2、bug的原因及解决

五、仿真源文件的获取

一、题目

图一 题目要求

如题,我们要设计三部分电路,一个时钟发生电路,一个N进制计数器,一个数码管显示电路,这里说明一下,第一问说要连接7进制电路,后面要求中又说要8进制计数器30分,我们这里就设计8进制计数器,原理都一样。

二、时钟发生电路

题目要求要用555设计一个时钟发生电路,555芯片能产生施密特触发电路、单稳态电路、多谐振电路。

1、施密特触发电路

我们可以通过施密特触发电路的传输特性来了解它的作用。

图二 施密特触发电路的传输特性

当我们不接555芯片的控制端的时候,他的传输特性就是图二,显然施密特触发电路不能满足我们时钟发生电路的需求。

图三 施密特触发电路的典型电路

施密特触发电路需要我们输入一个信号,可以用来做波形的整形,可以将正弦波整成矩形波,而不能做时钟发生信号。

2、单稳态电路

我们可以通过单稳态电路进行分析,单稳态电路的作用。

文章来源地址https://www.toymoban.com/news/detail-486336.html

图四 单稳态电路

由图四可知,单稳态电路也是需要输入的(触发源),当没有触发源或者刚通电的时候,为0,当触发脉冲的下降沿到来时电容机会进行充放电,先变为1在变为0,其中输出脉冲宽度为1.1RC。显然单稳态电路是不能满足我们的时钟发生电路的,单稳态电路可以实现定时、延时、整形。

3、多谐振荡电路

三个电路剩下一个,让我们看看能不能用多谐振荡电路实现时钟发生电路。

图五 多谐振荡电路

我们可以清楚的发现,多谐振荡电路不需要任何输入,这很符合它的名字:多谐振荡电路,它的输入其实是电容充放电提供的,输出的波形正好是个矩形波。

图六 多谐振振荡电路输入与输出

这里就不详细介绍原理性的知识了,就写几个重要公式了解振荡周期与占空比就可以了。

式(1)为电路的震荡周期

式(2)为电路的输出脉冲占空比。

所以我们连接出时钟发生电路。

图七 时钟发生电路

三、 N进制计数器

我们分别使用十进制计数器74HC192和十六进制计数器74HC193实现N进制计数器。

1、M<N的情形

以192为例,192为十进制计数器输出0-9十个数,7进制计数器输出0-7八进制计数器,那么我们就要跳过8(1000)、9两个状态,所以要将PL‘引脚接Q3,那么这样的话,计数器加到8的时候就会产生进位,跳过了8、9两个状态,当然我们没用到MR端,所以将MR端接地,值得一提的是我们也可以接MR端实现8进制计数器,只需要将与门接到MR端,将VCC接到PL’端其余不变即可。

图八 74HC192的引脚功能图

再接上我们之前连接出来的时钟发生电路,那么8进制电路就能连接出来了。

图九 8进制计数器电路

我们会了8进制电路的连接,那么是不是就会了2进制3进制等M<N的电路的连接了,就将PL‘端的与门修改一下就能实现你所要的进制的电路。

2、M>N的情形

我们就以题目中的24进制计数器为例来连接电路。

2、1 193实现

193为16进制计数器,显然一片193是不可能实现24进制计数器的,所以我们至少需要两片193,大体思路为:1片193从0-10开始计数,只要一到10,那么就产生进位,同时对第一片193芯片的数据清零,并且给第二片193一个加数信号,第二片193加1,这样就实现了多进制的加法计数器了,怎么实现24进制的计数器呢?很简单,让第二片193到了24就清零,那么计数器就会回到00。

图十 24进制加法计数器(193实现)

2、2 192实现

192为十进制计数器,只能输出0-9,无法输出10,所以我们不能用上述方法实现,我们知道,当192芯片从0加到9后再加一就会产生进位也就是TC’U引脚会置零,利用这个特性我们对两个芯片进行扩展,将第一片的TC‘U引脚连接到第二片的CPU脚上当作时钟信号,于是当第一片192产生进位的时候第二片192加一,加上清零端就实现了24进制加法计数电路,即将两片192的清零脚接在一起,当计数器达到24的时候全部清零,计数器回到00。

图十一 24进制加法计数器(192实现)

四、设计的小bug

说是bug其实也不算bug。

1、两个bug

1、我设计的24进制加法计数器(192实现)一上电的时候高位为9。

2、24进制加法计数器(193实现)的时钟发生电路有时候周期会出现占空比不一样的现象。

2、bug的原因及解决

我问了问大佬bug的原因和解决方法,得到了一个比较好的回复,由于我没有问大佬能否公开头像,所以这里就不公开了。

图十二 关于bug的回复

五、仿真源文件的获取

链接放在这,点赞才能下载。

链接:https://pan.baidu.com/s/1QfAtRH6NRhG9Y_t18lHsJg?pwd=cfhc

提取码:cfhc文章来源:https://www.toymoban.com/news/detail-486336.html

到了这里,关于任意进制加法计数器电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!