👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

1 Flash存储阵列结构及存储原理

1.1 NOR flash

1.2 NAND flash

1 Flash存储阵列结构及存储原理

1.1 NOR flash

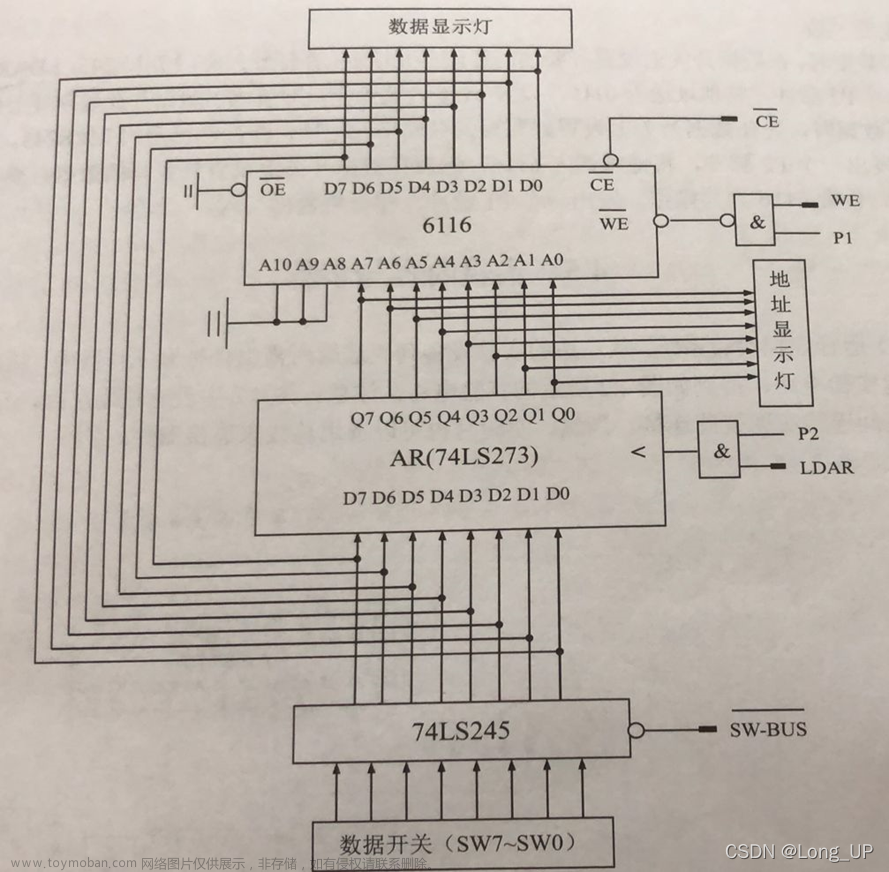

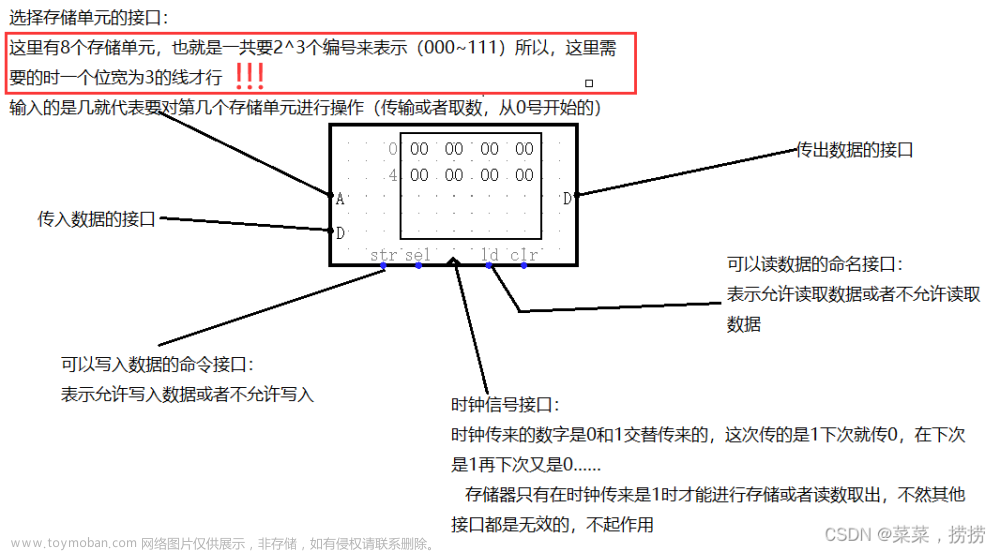

我们有了基本存储单元后,就要通过某种方式将基本存储单元连接到字线和位线上,通过选中字线和位线来访问对应的存储单元。

如下为一个2字x 8位的nor flash结构存储阵列示意图。WL为字线、BL为位线。其中位线在正常读操作过程会被充电到高电平,且位线输出还有一个反相器,这个图里没有画出。数据存储单元并联在位线上,其结构类似一个NOR或非门,所以叫NOR flash。

下面说明其读、写、擦的工作原理:

擦除:WL0、WL1接地,BL0~BL7接地,VS加12V电压,浮栅中的电子通过FN隧穿效应被拉回到源极,即都被改写成了1。

写入:注意写只能写0,写1和擦除原理一样。假设要对WL0字线单元写入10100010,此时VS接地,WL0加12V电压,WL1接地,同时,将要写0的单元,也就是需要电子注意浮栅的单元的漏极接高压来产生热电子注入,也即BL6、BL4、BL3、BL2、BL0接12V,并使BL7、BL5、BL1浮空。则存储单元T06、T04、T03、T02、T00发生热电子注入使浮栅充电,使管子的开启电压阈值升高(约7V),从而写入0。T07、T05、T01无法发生热电子注入,故其保持擦除时的“1”信息。而WL1因接地,存储电源里的信息不变。

读取:假设要对WL0字线单元进行读出。VS接地,位线BL0~BL7均被预充电至高电平,约1V~2V,WL1接地。WL0接3V~5V的电压,浮栅中已经注入电子的T06、T04、T03、T02、T00单元,其开启电压为7V,所以管子不会导通,所以位线BL6、BL4、BL3、BL2、BL0电压保持预充的1V~2V不变,而T07、T05、T01浮栅中没有电子,管子会导通,将位线BL7、BL5、BL1下拉至0V,然后位线电压反相后输出10100010。

1.2 NAND flash

从以上NOR flash的阵列结构可以注意到,整个阵列中所有晶体管的源极都连接到了VS,所有漏极都连接到了位线上,这些连接在芯片版图里将占据较大面积。为了避免这些开销,采用了另一种阵列结构,也就是nand。

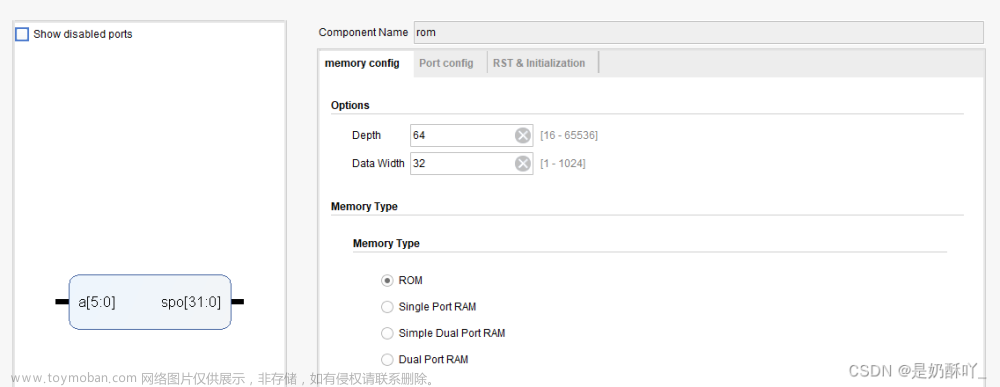

如下是一个8字x 8位的nand flash结构存储阵列示意图。一串存储单元串接在位线上,另外最上方还有一个位线选择晶体管,最下方还有一个地线选择晶体管,用着两个管子来选中相应的位线。同样位线的充电和输出反相没有画出来,其结构类似于NAND与非门,所以叫nand flash。

擦除:WL0~WL7接地,VS、BL0~BL7浮空,衬底加高压20V,浮栅中的电子通过FN隧穿效应被拉回到衬底,即都被改写成了1。擦除的单位是所有共衬底的单元中字线接地的部分,一般是一个block,通常一个block是由多根字线(比如64根)构成的阵列组成。

写入:注意nand flash不能随机编程,只能按地址顺序编程(我个人理解从阵列本身操作来说是可以随机编程的,给相应的字线、位线电压即可。其实这个是和ECC相关,具体原因我们后续分享),只能WL0,接着WL1~WL7,写入最小单位为page。编程时,写入的字线加高电压20V,其余字线加10V,衬底接地,VS浮空,若要写0,将相应的位线接0V,即漏极接0V,则控制栅和漏极间的20V 将产生FN隧穿效应,使浮栅充上电子,抬高此管的开启电压,完成写0。若要写1,将相应的位线接10V,即漏极接10V,则控制栅和漏极间的只有10V压差,无法产生FN隧穿效应,则浮栅上没有充上电子,即保持为1。文章来源:https://www.toymoban.com/news/detail-486877.html

读取:位线预充电至2V,VS接地,未选中的字线加10V,选中的字线加3V,未选中的字线无论浮栅中有没有电子,管子都导通,就相当于被选中的单元漏极直接接在位线上,若被选中的单元浮栅中有电子,则管子不导通(充了电子后管子开启电压抬高到7V),位线仍为2V,经反相器后输出0,若被选中的单元浮栅中没有电子,则管子导通,位线被拉至VS,经反相器后输出1。读取过程只能顺序读,不能随机读(同样和ECC相关,如果软件没有适配ECC功能,原理上可以随机读)。文章来源地址https://www.toymoban.com/news/detail-486877.html

到了这里,关于【FLASH存储器系列三】FLASH存储阵列结构及存储原理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!