目录

第一部分、新建工程

第二部分、添加顶层文件

第三部分、添加管脚约束文件

第四部分、生成bit文件

第五部分、连接开发板,下载bit文件

第六部分、总结

第一部分、新建工程

第一步、如果提前建立了工程文件夹,那么这里就需要去掉生成子文件夹的路径。

因为ISE软件输入工程名称后自动在当前文件夹下创建一个新文件夹。

第二步、删除后的效果

第三步、选择所用FPGA的芯片的型号

第二部分、添加顶层文件

第一步、添加写好的顶层文件模块

第二步、保持默认

第三部分、添加管脚约束文件

第一步、新建一个执行约束文件

第二步、选择第三个

第三步、添加执行约束文件名称

第四步、编辑约束文件,后缀为.ucf

第五步、添加约束代码,端口,管脚,电平

第四部分、生成bit文件

第一步、点击顶层模块

第二步、编译文件

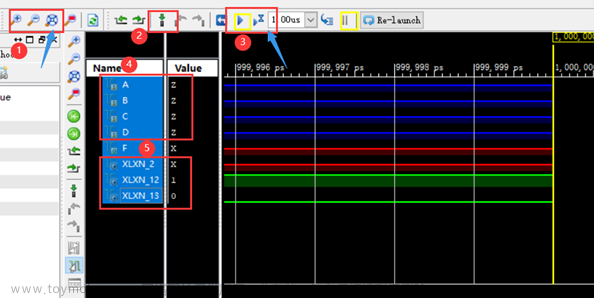

第五部分、连接开发板,下载bit文件

第一步、双击iMPACT目录

第二步、连接开发板

第三步、关闭这个弹窗

第四步、也关闭这个弹窗

第五步、双击芯片

第六步、选择刚刚生成的bit文件

第七步、不下载到rom中,取消

第八步、program

第九步、下载成功后的标志

文章来源:https://www.toymoban.com/news/detail-488285.html

文章来源:https://www.toymoban.com/news/detail-488285.html

第六部分、总结

学会上面这些步骤,我个人觉得ISE软件你基本学会了80%,后面就是灵魂,如何写代码。文章来源地址https://www.toymoban.com/news/detail-488285.html

到了这里,关于【FPGA入门】第二篇、ISE软件的使用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!