总线控制实验

一.实验目的

1.理解总线的概念及特性;

2.掌握总线传输控制特性。

二.实验原理

总线的基本概念:

总线是多个系统部件之间进行数据传输的公共通路,是构成计算机系统的骨架。借助总线连接,计算机在系统各部件之间实现传送地址、数据和控制信息的操作。所谓总线就是指能为多个功能部件服务的一组公用信息线。

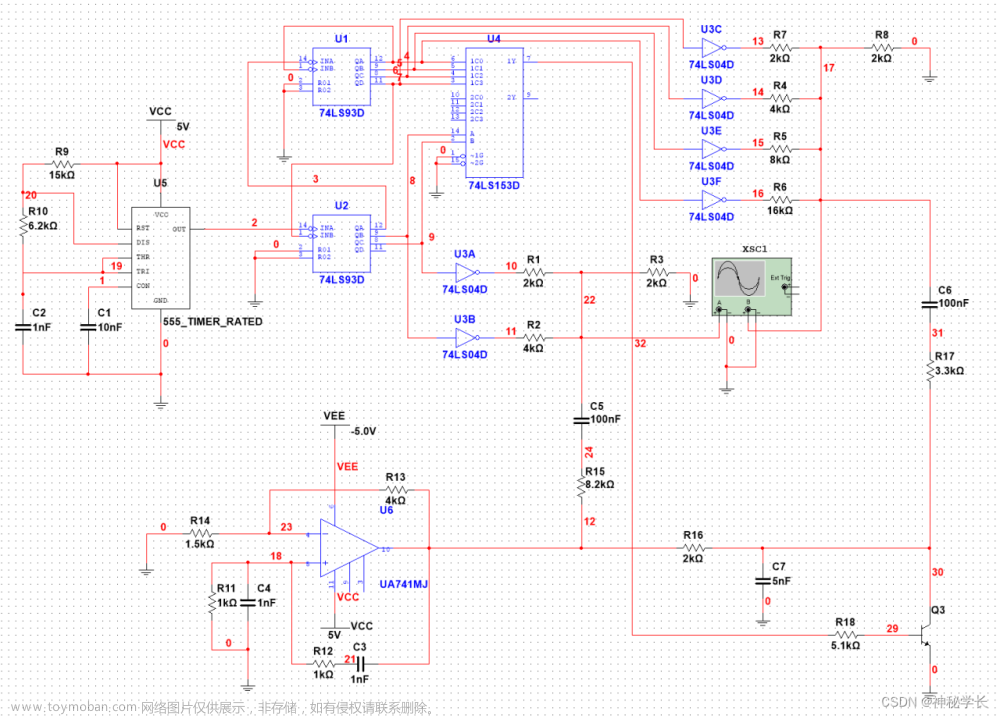

实验所用总线实验传输框图如图5-1所示。它将几种不同的设备挂在总线上,有存储器、输入设备、输出设备、寄存器。这些设备在传统的系统中需要有三态输出控制,然而在FPGA的内部没有三态输出控制结构,因此必须采用总线输出多路开关结构加以控制。按照传输要求恰当有序地控制它们,就可以实现总线信息传输。

三.实验内容

1.实验任务

根据挂在总线上的几个基本部件,设计一个简单的流程。

(1)输入设备将数据打入寄存器R0。

(2)输入设备将另一个数据打入地址寄存器AR。

(3)将寄存器R0中的数据写到当前地址的存储器中。

(4)将当前地址的存储器中的数用数码管显示。图5-4是总线控制的波形图。

2.实验步骤

(1)实验电路如图5-2所示。写使能WE=1允许写,WE=0禁止写,允许读;inclock为数据DATA锁存时钟。具体操作可参考图5-3。

(2)文件是BUS-4.bdf,下载BUS-4.sof到实验台的FPGA中;

(3)实验内容1

根据图5-2完成实验操作:选择实验模式“0”;再按一次右侧的复位键(用一接线将实验板上键9的输入端插针与适配板上FPGA的第P196针相连,以便能用键9控制OUT锁存器的时钟;):初始状态;1、键4、键3控制设备选择端:sel[1…0]=00(键4、键3=00);2、此时由键2、键1输入的数据(26H,显示于数码管2、1)直接进入BUS(数码管8、7显示),键5、6、7为低电平;3、键8=1(允许RAM写入)完成图5-2所示的操作:4、键5发正脉冲(0-1-0),将数据打入寄存器R0;5、键2、键1再输入数据(如37H);6、键6发正脉冲(0-1-0),将数据打入地址寄存器AR;7、键2、1再输入数据(如48H);8、键7发正脉冲(0-1-0),将数据写入RAM(此时必须键8输出‘1’,注意此时进入RAM的数据48H是放在地址37H单元的);9、键2、键1再输入数据(如59H);10、键9发正脉冲(0-1-0),将数据写入寄存器OUT(数码管6、5将显示此数);11、键4、键3分别选择sel[1…0]=00、01、10、11,从数码管8、7上观察被写入的各寄存器中的数据。

(4)实验内容2

先将数据28H写入RAM的地址(4AH),再将数据1BH送进R0,最后将刚才写入RAM中地址(4AH)的数据读出送到OUT口。依据总线电路图5-3,操作如下:

1、用一接线将实验板上键9的输入端插针与适配板上FPGA的第P196针相连,以便能用键9控制OUT锁存器的时钟;键3、4、5、6、7、8都为低电平,使键4、键3=00,即总线多路选择器sel[1…0]=00,选择由键2、键1输入的数据4AH(地址),直接进入BUS;

2、按键6两次(0-1-0),产生一个正脉冲,将地址数据4AH(地址)锁入地址寄存器AR,如图5-3所示,此数据直接进入RAM的address端;

3、按键2、键1,输入数据28H(数据),此时直接进入总线BUS,并进入RAM的data数据端;按键8=1(RAM写允许);按键7两次,将数28H写入RAM(地址为4AH),最后按键8=0,写禁止,读允许。

4、由键2、键1输入的数据1BH,按键5两次(0-1-0),产生一个正脉冲,即此数写入R0寄存器。

5、读RAM送到OUT:由键2、键1输入的数据4AH,按键5两次,使4AH进入AR;

6、按键7两次,RAM中4AH单元中的数据28H输出,再使键4、键3=10,即总线多路选择器sel[1…0]=10,此时RAM数据口的28H进入总线BUS(可从数码管8、7上看到);

7、按键9一次(此键是单脉冲),RAM口的28H即被锁如输出口OUT寄存器,由数码管6、5显示。

8、键盘/显示定义详细说明:

(1)键2、键1输入D[7…0],输入的数据同时显示在数码2和数码3上。

(2)键9、键3输入控制设备选择端sel[1…0],如图5-2所示,键4、键3控制总线多路选择器,选择不同设备的数据进入总线:sel[1…0]= 00:输入设备INPUT数据进入总线BUS;= 01:寄存器R0中的数据进入总线BUS;= 11:地址寄存器AR的数据进入总线BUS;= 10:存储器RAM的数据进入总线BUS;

(4)总线BUS上的输出数据显示在数码8和数码7上;

(5)键5控制寄存器R0的输入选通锁存端;

(6)键6控制地址寄存器AR输入选通锁存端;

(7)键7控制LPM_RAM数据DATA输入锁存端;

(8)键8控制LPM_RAM写入允许WE端,=1有效;

(9)键9控制输出设备OUTPUT的输入选通端,输出数据显示在数码6和数码5上,要求首先用一接线将实验板上键9的输入端插针与适配板上FPGA的第P196针相连。

四.实验报告要求

(1)实验原理。

(2)在思考题中选作2~3题,给出实现方案和具体的操作步骤。

(3)绘制相应的时序波形图。

(4)实验结果分析、讨论。

五.实验结果

本次实验中我验证了实验内容1,具体操作步骤如下:

(1)选择实验模式“0”并置键8为高电平(允许RAM写入);

(2)利用键4、键3控制设备选择端并置键4、键3 为低电平;

(3)由键2、键1输入数据26H(显示于数码管2、1),该数据直接进入总线(由数码管8、7显示);

(4)键5发送一次正向脉冲,将数据打入寄存器R0;

(5)键2、键1输入数据37H,键6发送一次正向脉冲,将数据打入地址寄存器AR;

(6)键2、键1再输入数据48H,键7发送一次正向脉冲,将数据写入RAM(此时必须键8输出高电平)。由数据锁入规则可以知道此时进入RAM的数据48H存储在地址为37H的存储单元中。

用实验箱验证实验结果图如下:

六.思考题

1. 如何向RAM中输入多个数据,并在输出设备OUTPUT上显示这些数据?(将3个数据写入RAM的不同地址中,再将它们分别读出,在OUT上显示)

答:利用键一,键二,键三分别把数据输入,然后再用控制信号产生不同的脉冲将数据存入RAM中,然后再用相同的脉冲将数据读处来。

2.传输过程中是否会在总线上发生数据冲突?若发生冲突应怎样避免?

答:若指令设计不当,可能会出现总线竞争或冲突的风险。可以通过总线仲裁的方式来避免冲突。文章来源:https://www.toymoban.com/news/detail-488453.html

七.实验心得体会

通过本次实验,我将计组课本学过的总线相关理论知识和实验得到的实践结果相结合,深入理解了总线的概念及数据传输特性,掌握了总线传输控制的特点及传输数据的步骤,也锻炼了自己的实验箱实际操作能力。文章来源地址https://www.toymoban.com/news/detail-488453.html

到了这里,关于西电计组实验五 总线控制实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!