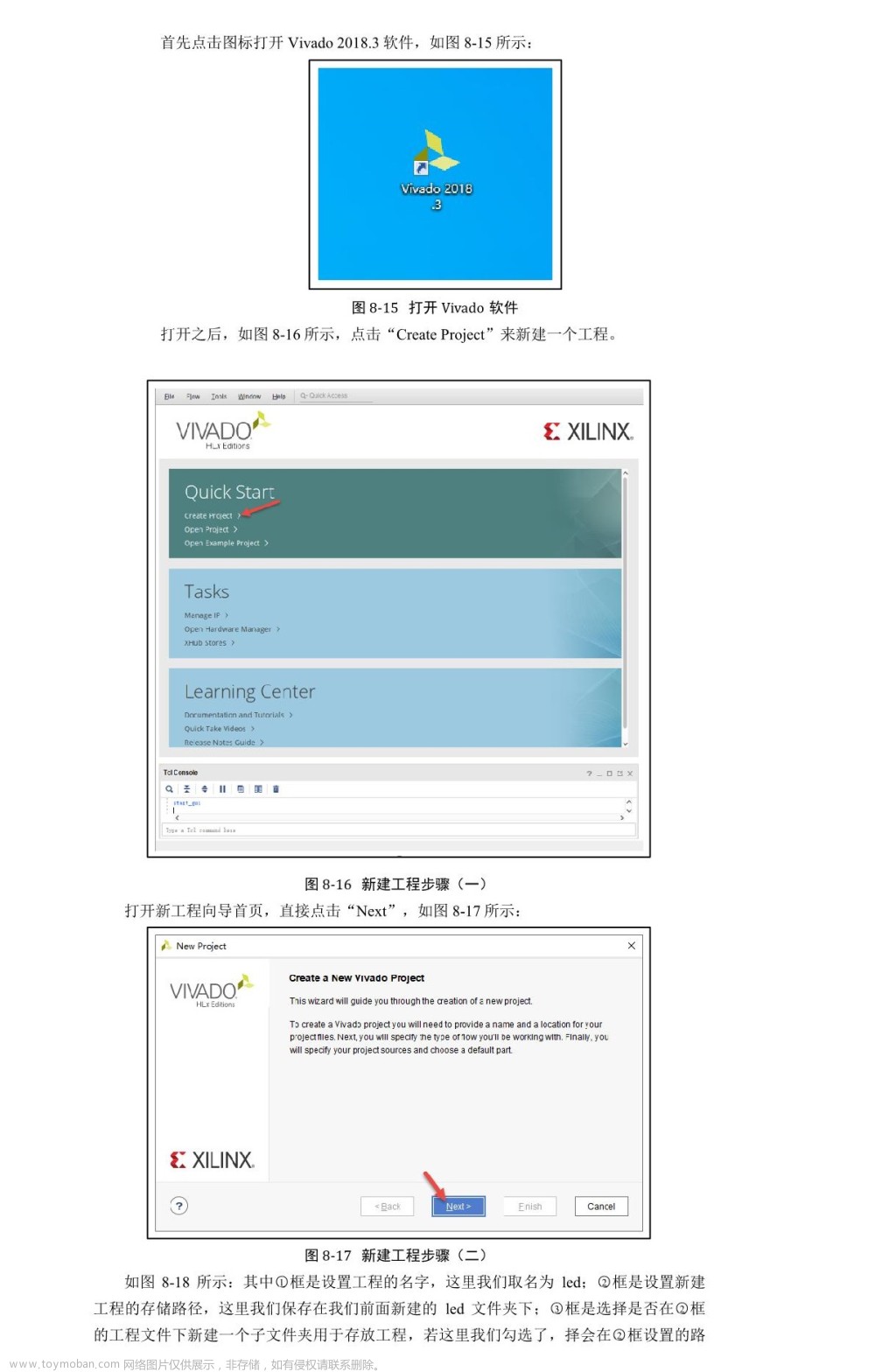

一、工程创建

注意一定要选verilog语言,后续才能配置mig

二、打开mig配置界面

1.如果创建了工程,但是没有创建MIG IP核

图1

2.如果是已经配置好了MIG IP核,想要修改其设置。

双击图中所示

图2

三、 配置步骤

说明:官方的教程可以点击配置界面左下方的user guide,去其网站上下载官方的英文说明文档**

1.确认一下器件**

图3

2.是否设置axi4接口配置

(1)纯FPGA的芯片(A系列(如正点原子的达芬奇开发板芯片为xc7a35t-fgg484(也就是A7-35T)或者xc7a100tfgg484-2等(也就是A7-100T)),K系列),一般DDR是直接连接到FPGA,采用native接口;教程参考正点原子达芬奇开发板。

(2)ZYNQ系列的(ZYNQ系列的DDR挂载在PS端),采用的AXI4总线连接DDR。教程参考正点原子ZYNQ sdk开发教程。

图4

两种不同类型对应的设计框图如下

这是native 接口

图5

下图是axi接口

图6

3.其他芯片的兼容性选择(一般不勾选)

图7

4.DDR控制器类型选择

图8

5.时钟配置

图9

根据选择的DDR芯片的数据手册对应的时间,可以计算出频率=1/1.25ns=800Mhz.

图10

官方手册的解释是这个频率是考虑到DDR和FPGA芯片

图11

位宽的问题,参考这篇博客

https://blog.csdn.net/m0_52840978/article/details/121191028

图12

图13

上图中的400M是什么意思呢?

对应的是DDR芯片的工作频率,也就是下图的右下角,DDR芯片的工作频率部分

整体的配置示意图如下

图14

高清的图片详见附件

https://download.csdn.net/download/qq_41869515/87583142

之后next下一页

这里是MIG IP核的系统时钟设置,一般设置为200M,截屏里边的是400M(器件限制了,所以没法设置到200M)

图15

next

图16

next

如果有提前设置好的引脚约束文件就选下边的设置fixed pin out.如果只是做仿真,就不需要和实际的FPGA引脚绑定,就选new design.

图17

其他默认点击yes就行文章来源:https://www.toymoban.com/news/detail-490425.html

有些地方如果有理解不到位,欢迎评论区更正。文章来源地址https://www.toymoban.com/news/detail-490425.html

到了这里,关于vivado DDR配置讲解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!