用于复习408或计算机组成原理期末考试。如有错误请在评论区指出。

So let's start studying with questions!

それでは、問題の勉強を始めましょう!

1. 设某浮点数真值为 0.125,若该浮点数用 IEEE754 标准表示,则该浮点数对应的机器数是什么?(用十六进制表示,不写步骤不得分)

答案:根据IEEE 754标准,单精度浮点数(32位)由三部分组成:符号位(1位)、指数位(8位)和尾数位(23位)。

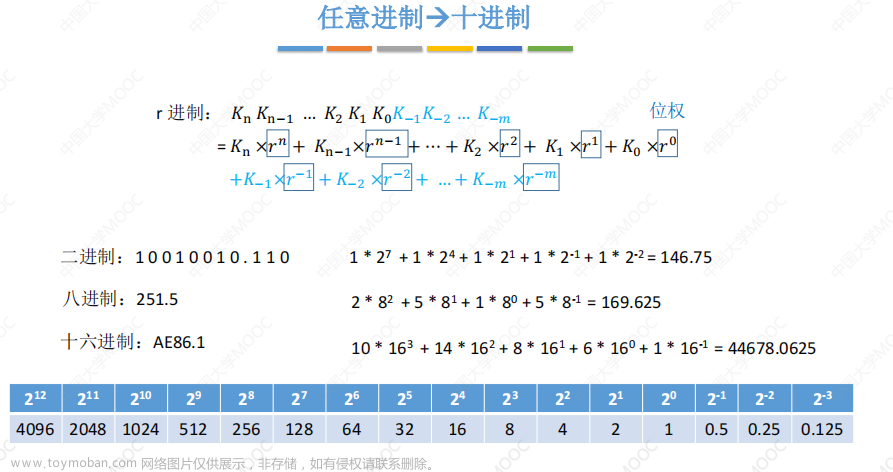

首先,我们将0.125转换为二进制的规范化科学计数法表示形式:

0.125 = 1.0 × 2^(-3)根据规范化科学计数法的表示形式,符号位为0(表示正数),指数位为-3+127=124(偏移值为127),尾数位为00000000000000000000000(23个0,因为尾数是规范化的,首位默认为1)。

将符号位、指数位和尾数位组合起来,得到32位的机器数表示形式:

0 01111100 00000000000000000000000将该32位二进制数转换为十六进制表示形式,得到结果:

0x3C000000因此,浮点数0.125在IEEE 754标准下的机器数表示为0x3C000000。

2. 设有 8 位补码,请写出该 8 位补码的表示范围。

答案:在8位补码表示中,最高位为符号位,剩下的7位用于表示数值。对于8位补码,其表示范围如下:

最小值:10000000(-128的补码)对应于 -128

最大值:01111111(127的补码)对应于 +127因此,8位补码的表示范围为-128到+127。

3. 利用 IEEE754 标准,计算浮点数 0.25+0.125 的计算过程。(不写步骤不得分)

答案:首先,将0.25和0.125转换为二进制的规范化科学计数法表示形式。

0.25 = 1.0 × 2^(-2)

0.125 = 1.0 × 2^(-3)根据IEEE 754标准,规范化科学计数法的表示形式包括符号位、指数位和尾数位。

将两个浮点数分别转换为对应的32位二进制表示形式:

0.25:0 01111101 00000000000000000000000

0.125:0 01111100 00000000000000000000000接下来,进行浮点数的加法计算。根据IEEE 754标准,需要对尾数进行对齐。

将0.125的尾数右移1位,得到0.0625的二进制表示形式:

0.0625 = 1.0 × 2^(-4)对齐后的两个浮点数表示为:

0.25:0 01111101 00000000000000000000000

0.0625:0 01111100 10000000000000000000000将尾数相加,得到结果:

0.25 + 0.125 = 0.3125 = 1.25 × 2^(-2)将结果转换为IEEE 754标准下的表示形式:

0.3125 = 1.25 × 2^(-2)

符号位为0(表示正数)

指数位为-2+127=125

尾数位为01000000000000000000000(23个0)将符号位、指数位和尾数位组合起来,得到32位的机器数表示形式:

0 01111101 01000000000000000000000将该32位二进制数转换为十六进制表示形式,得到结果:

0x3E400000因此,浮点数0.25+0.125在IEEE 754标准下的机器数表示为0x3E400000。

4. 什么是多重中断?实现多重中断的必要条件是什么?

答案:多重中断是指在一个计算机系统中同时发生多个中断请求的情况。中断是计算机系统中的一种机制,允许外部设备或其他事件中断正在执行的程序,以便处理紧急事件或执行特定任务。

实现多重中断的必要条件包括以下几点:

1. 中断控制器:计算机系统需要具备中断控制器的功能,用于管理和协调不同设备的中断请求。中断控制器负责接收、识别和分发中断请求,并确定中断优先级的顺序。2. 中断优先级:对于同时发生的多个中断请求,系统需要确定中断的优先级顺序。通常,每个中断都会被分配一个优先级,优先级较高的中断将被首先响应和处理。

3. 中断处理程序:针对每个中断类型,系统需要编写相应的中断处理程序,以执行与中断相关的操作。中断处理程序负责保存当前执行的程序状态,处理中断事件,并在中断处理完成后返回原来的程序继续执行。

4. 中断向量表:中断向量表是一个存储中断处理程序地址的数据结构。当发生中断时,系统根据中断类型查找相应的中断向量表项,从而确定要执行的中断处理程序的地址。

综上所述,要实现多重中断,计算机系统需要具备中断控制器、中断优先级机制、中断处理程序和中断向量表等必要条件。

5. 简述 CPU 的基本功能

答案:CPU(中央处理器)是计算机系统中的核心部件,负责执行指令和进行数据处理。CPU的基本功能包括以下几个方面:

1. 取指令(Instruction Fetch):从内存中读取指令,确定下一条要执行的指令的地址。

2. 解码指令(Instruction Decode):对取到的指令进行解码,确定指令的操作类型和操作数。

3. 执行指令(Instruction Execution):根据解码的指令类型,执行相应的操作,如算术运算、逻辑运算、数据传输等。

4. 访存(Memory Access):如果指令需要读取或写入内存中的数据,CPU会与主存储器进行数据交换。

5. 写回(Write Back):将执行结果写回寄存器或内存,以保存计算结果或更新数据。

6. 控制(Control):CPU控制电路负责协调各个功能部件的工作,根据指令的执行顺序控制数据的流动。

CPU的基本功能是通过时钟信号进行同步操作的,每个时钟周期完成一个基本功能操作。CPU的性能通常通过时钟频率(每秒钟的时钟周期数)来衡量,时钟频率越高,CPU的处理速度越快。

6. 简述指令周期,机器周期和时钟周期。

答案:在计算机体系结构中,指令周期、机器周期和时钟周期是描述计算机指令执行过程中时间相关的概念。

1. 指令周期(Instruction Cycle):指令周期是执行一条指令所需的时间,包括取指令、解码指令、执行指令、访存和写回等步骤。一个完整的指令周期包括从一条指令的开始到下一条指令的开始。

2. 机器周期(Machine Cycle):机器周期是指令周期的一个子周期,用于描述执行一条指令所需的基本操作。机器周期可以进一步细分为若干个时钟周期,每个时钟周期完成一个基本操作。

3. 时钟周期(Clock Cycle):时钟周期是指计算机系统中基本时钟信号的周期,也是计算机的最小时间单位。时钟周期是计算机操作的基本时间单位,所有的指令和操作都以时钟周期为基础进行计时和同步。

在一个计算机系统中,指令周期由多个机器周期组成,而每个机器周期由多个时钟周期组成。时钟周期是计算机系统中各个部件进行工作的时间基准,各个部件按照时钟周期进行协调和同步。时钟频率(Clock Rate)是指时钟信号的频率,即每秒钟发生的时钟周期数,通常以

赫兹(Hz)为单位表示。时钟频率越高,计算机系统的处理速度越快。

7. 请比较间接寻址和寄存器间接寻址

答案:间接寻址和寄存器间接寻址都是指令中用来获取操作数的寻址方式,它们的区别在于操作数的来源不同。

- 间接寻址(Indirect Addressing):指令中的地址字段表示一个内存地址,该地址存储了操作数的真实地址。在执行指令时,需要先通过地址字段获取到内存中的真实地址,然后再从该地址中读取操作数。

- 寄存器间接寻址(Register Indirect Addressing):指令中的地址字段表示一个寄存器的编号或名称,该寄存器存储了操作数的真实地址。在执行指令时,直接使用寄存器中存储的地址作为操作数的地址,无需再从内存中获取。

简单来说,间接寻址需要通过地址字段访问内存获取操作数,而寄存器间接寻址则直接使用寄存器中存储的地址作为操作数的地址。间接寻址适用于操作数在内存中存储的情况,而寄存器间接寻址适用于操作数已经存储在寄存器中的情况。寄存器间接寻址通常会比间接寻址更快速,因为直接从寄存器中获取操作数不需要额外的内存访问。

8. 设某计算机采用指令流水,并假设流水线由 5 段组成,流水线周期为 T。请描述该指令流水线分别采用顺序执行和流水执行时执行 n 条指令所需要的时间(不考虑相关)。

答案:在顺序执行中,每条指令依次经过取指、译码、执行、访存和写回等阶段,完成后才能开始下一条指令的执行。因此,执行n条指令所需要的时间为n倍的流水线周期。

在流水执行中,指令被分成若干个阶段,每个阶段由不同的流水线段处理,不同的指令可以同时处于不同的阶段。假设流水线由5段组成(取指、译码、执行、访存、写回),则每个阶段的处理时间为T。在流水执行中,第一条指令经过5个阶段后完成,同时第二条指令进入执行阶段,以此类推。因此,执行n条指令所需要的时间为(n-1)倍的流水线周期。

可以看出,在流水执行中,指令的执行时间可以大大缩短,提高了指令的吞吐量。然而,流水线执行也面临相关(依赖)问题,可能需要额外的控制和调度机制来解决相关导致的问题。

9. 简述指令流水线中的三种相关

答案:在指令流水线中,存在三种相关,即结构相关(Structural Hazard)、数据相关(Data Hazard)和控制相关(Control Hazard)。

- 结构相关:指多个指令在同一时钟周期内需要访问同一硬件资源,导致资源冲突。这种相关通常由于硬件资源的冲突而产生,例如多条指令需要同时访问同一个寄存器或存储器。解决结构相关可以通过合理的硬件设计和资源分配来避免或减少资源冲突。

- 数据相关:指后续指令需要依赖前面指令的结果,导致数据冲突。数据相关分为数据读相关(Read After Read,RAR)、数据写相关(Read After Write,RAW)和数据写相关(Write After Write,WAW)。这种相关通常由指令之间的数据依赖关系引起,例如一个指令的结果被后续指令使用。解决数据相关可以通过插入适当的等待周期(如空转周期或气泡周期)、使用旁路(Bypass)技术或进行指令重排等方法来消除或减少数据冲突。

- 控制相关:指由于分支指令的存在,导致后续指令的执行路径发生改变。当分支指令的条件满足时,会改变程序的执行顺序,从而影响后续指令的执行。控制相关通常由分支指令(如条件分支、无条件分支)引起。解决控制相关可以通过静态预测、动态预测、延迟槽(Delay Slot)等技术来提高分支预测的准确性和流水线的效率。

10. 在微指令控制器中,微指令分为操作控制字段和顺序控制字段,简述操作控制字段的编码方法,并对这些方法进行比较。

答案:操作控制字段是微指令中的一部分,用于指示执行微指令所需的操作控制信号。操作控制字段的编码方法可以采用以下几种方式:

1. 位编码:操作控制字段的每个位都对应一个操作控制信号,可以直接通过位的取值来表示相应的操作控制信号。这种编码方法简单直观,但对于较长的操作控制字段会占用较多的位数。

2. 字段编码:将操作控制字段分成若干个字段,每个字段对应一个操作控制信号。字段可以是连续的位,也可以是

非连续的位。每个字段可以使用不同的编码方式,如二进制、十进制或十六进制等。这种编码方法可以提高编码的灵活性和可读性,减少位数的占用。

3. 字段组合编码:将操作控制字段划分为若干个字段组合,每个字段组合表示一种操作控制信号的组合情况。每个字段组合可以使用位编码或字段编码的方式表示。这种编码方法可以进一步减少位数的占用,但需要额外的逻辑电路来实现字段组合的解码。

以上三种编码方法各有优缺点。位编码简单直观,但对于较长的操作控制字段会占用较多的位数。字段编码提供了更好的灵活性和可读性,但可能需要更多的位数。字段组合编码可以进一步减少位数的占用,但需要额外的解码电路。选择合适的编码方法取决于具体的微指令控制器设计需求,需要综合考虑位数的占用、可读性和电路复杂度等因素。文章来源:https://www.toymoban.com/news/detail-491353.html

文章来源地址https://www.toymoban.com/news/detail-491353.html

到了这里,关于计算机组成原理(考研408)练习题#4的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!