前言:设计一个能产生固定频率的电路,然后经过单片机处理后显示该固定频率的系统。

1、指标以及功能要求

指标:该系统要能够产生一个31KHz的方波,进过单片机脉冲采集后能够在液晶上显示出该频率。要求:所用的知识要涉及到模拟电路知识和数字电路知识。

2、设计分析

该设计要是能够产生一个固定频率的方波,而且能够将其测量显示出来的系统。目前市场上有很多芯片能够直接输出方波,但是为了体现模拟电路和数字电路的综合应用,本题目采用简单的RC振荡电路产生一个正弦波,之后经过比较器后输出方波,再经过一个分频器二分频后接入单片机采集处理后显示。该方案采用RC桥式振荡电路产生正弦波,电路简单、成本低廉,但此方案产生的最大的缺点是电路的工作频率一般低于1MHz。由运放构成的RC串并联正弦波振荡电路不是靠运放内部的晶体管进入非线性区稳幅,而是通过在外部引入负反馈来达到稳幅的目的,因此稳定性不是很高。得到正弦信号后进过一个过零比较器将正弦信号变成方波,之后经过数字芯片JK触发器或者是D触发器二分频后送单片机采集处理显示。

3、设计思路

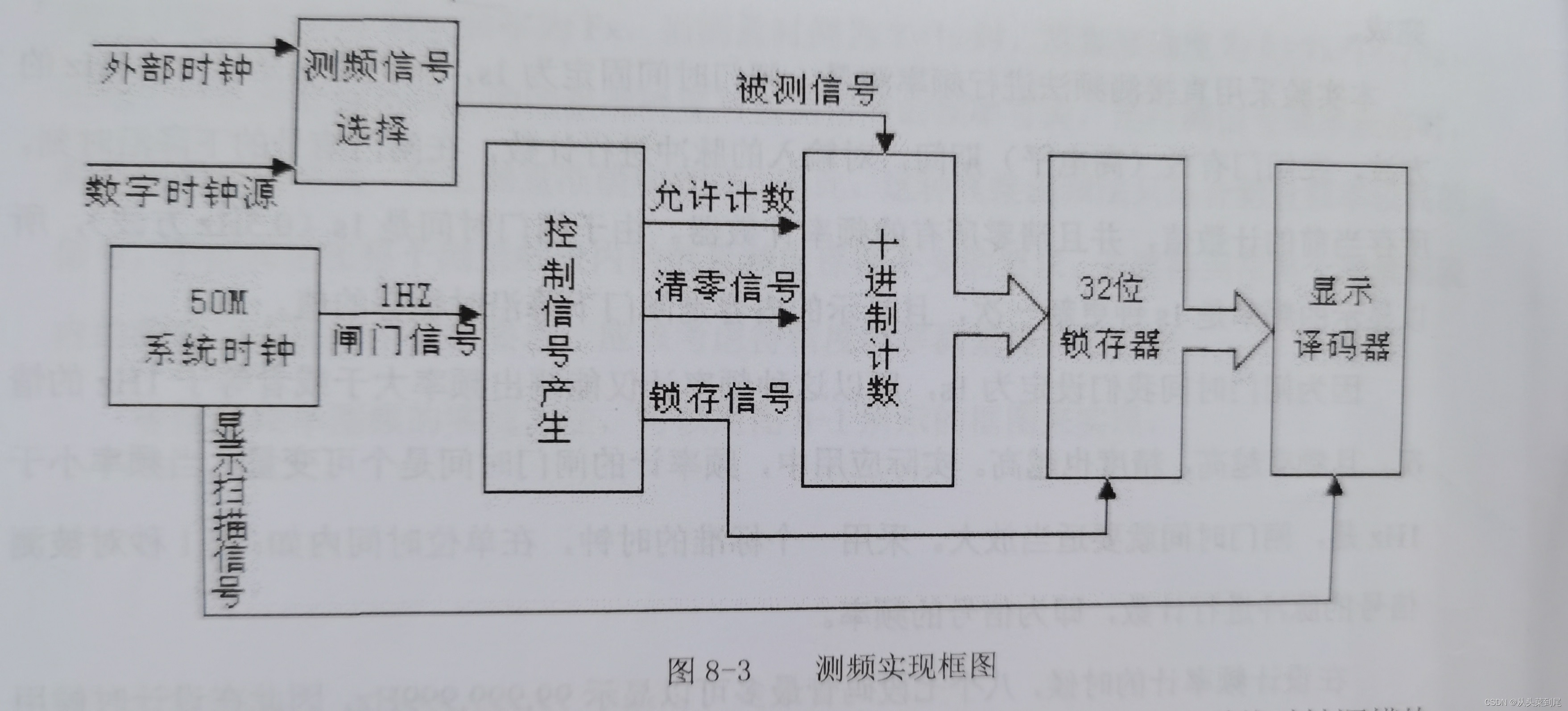

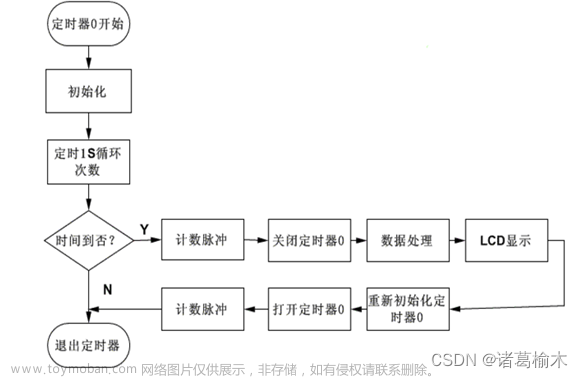

根据复杂程序设计思想——模块化程序设计,分析和确定程序总体设计目标:频率计基本功能及部分扩展功能后,将总体目标划分为若干模块(设计框图图1、子程序,具体可见下)。

程序设计的思路按以下顺序进行:

1. 分析与确定程序总体设计目标

2. 将总体目标划分为若干模块

3. 定义每个模块的具体任务,明确它与其他模块间的通信方式

4. 编写源程序,进行调试

4、总体设计框架及其电路

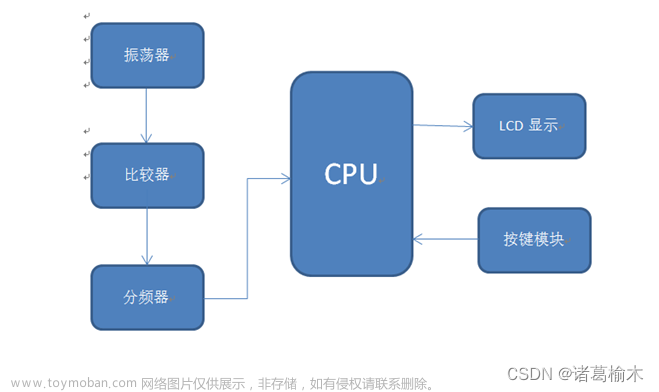

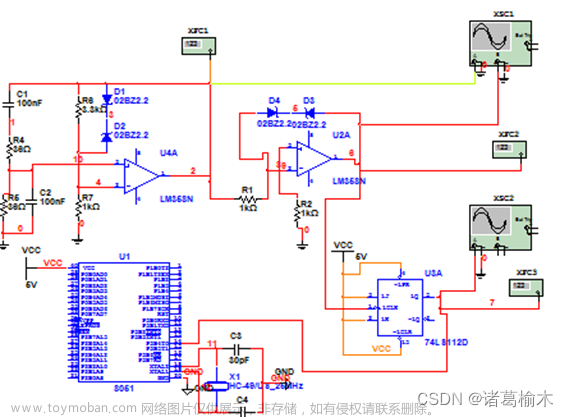

本方案设计的系统由单片机系统,RC振荡电路,比较器,分频器以及0.96OLED液晶显示。总体框架见以下图

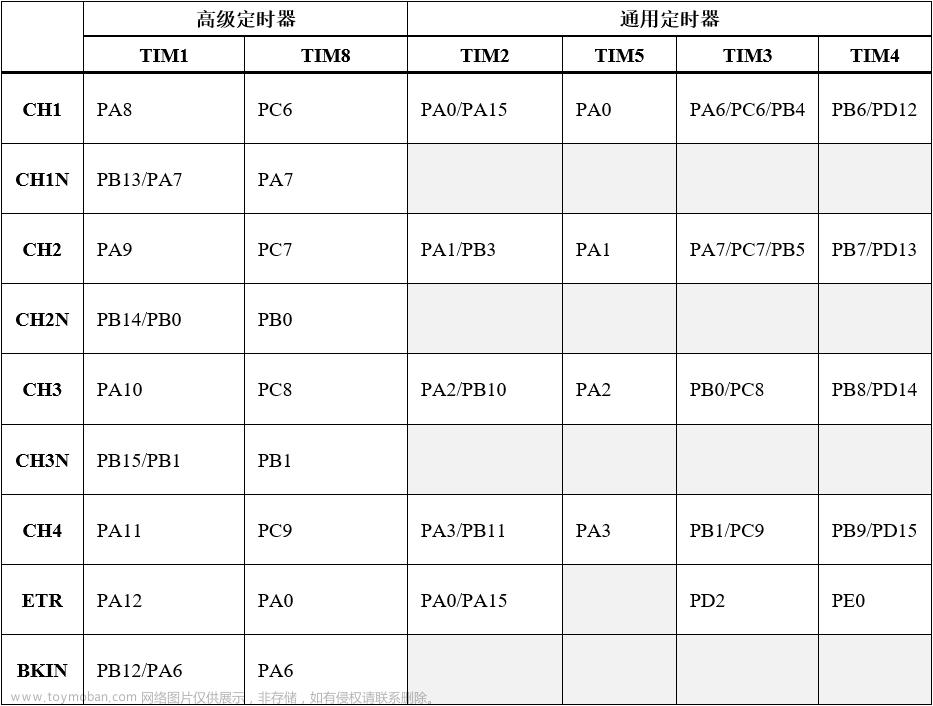

电路设计:STC89C52RC单片机最小系统+键盘+lm393N+LM358+液晶显示+74LS112D等

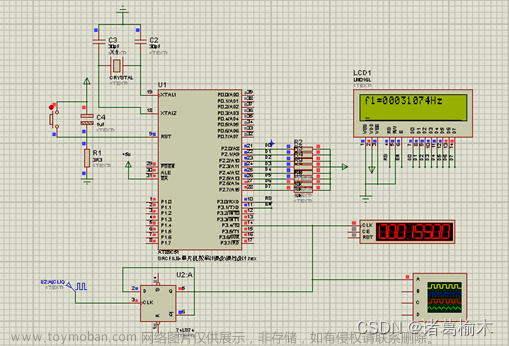

5、总体题电路图

下图产生方波的具体实现电路,它由三个部分组成:RC桥式振荡电路、过零比较以及分频电路组成。其能够产生一个固定频率的方波信号。

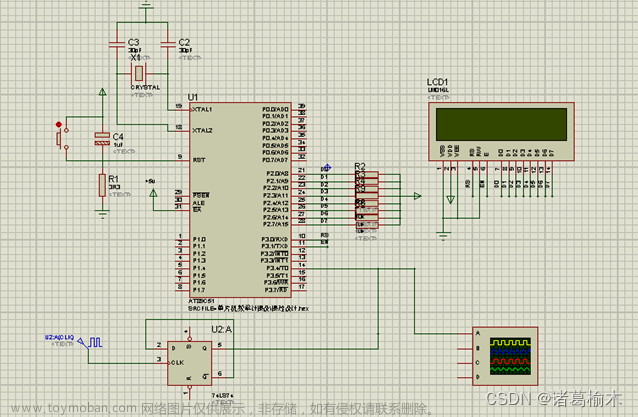

下图单片机显示电路,能够将电路输出的信号采集处理后用液晶显示出来。

6.各部分电路图

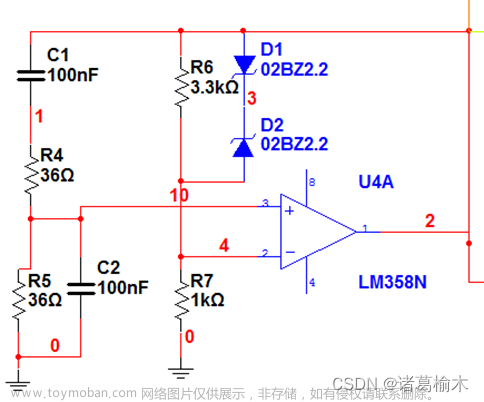

常见的RC正弦波振荡电路的RC串并式正弦波振荡电路,又称文氏桥正弦波振荡电路,其电路如下所示。电路由放大器和RC串、并联网络两部分组成,放大器部分由同比例放大电路组成,放大电路的输出电压与输入电压同相,输入信号放大后,再经过正反馈送到输入端。电路中的R5,R6,C1,C2等4个元件串、并联组成电路的选频环节和正反馈。自激反馈信号取自于C2,R5并联电路两端。RC正弦波振荡电路在振荡以后,振荡器的振幅会不断增加,直至受到运放的最大输出电压的限制,使输出波形产生非线性失真。为此,振荡电路需要加上如图所示的稳压二极管来稳定输出电压的幅值。

为了使电路能振荡,要满足起振条件,即要求|AF|>1,而F=1/(3+j(w/wo-wo/w)),|A|=1+Rf/R3。当w=wo时,要求|A|>3,即R6>2R7。

电路的振荡频率为

f=1/2πRC

采用过零比较器,来将正弦波整成方波。所谓过零比较器,就是参考电压为零的比较器。将集成运放的一个输入端接“地”,另外一个输入端接输入信号,就构成了过零比较器。电路输出高低电平取决于运放的幅值输出电压,当输入信号电压大于0时,输出正运放幅值电压,反之输出负的运放幅值电压。由于过零比较器电路简单,但其输出电压幅度较高,这时候用背靠背的稳压管实现限幅的过零比较器如上图所示。

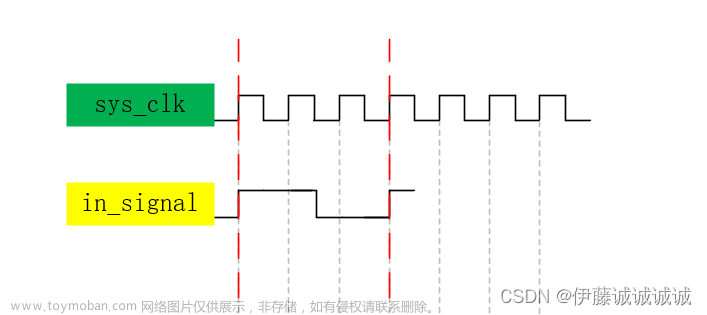

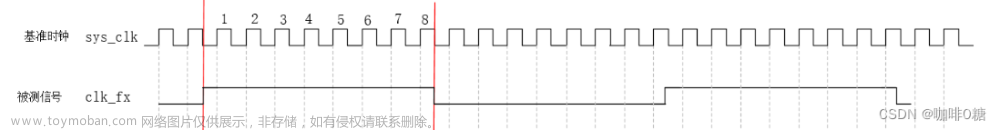

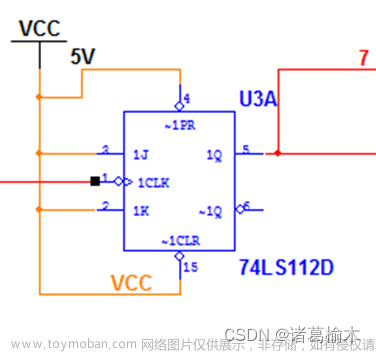

下图是数字芯片JK触发器,当就 j=k=1时,每输入一个脉冲下降沿来临时,其输出状态发生改变即实现了二分频的作用。

7、电路仿真结果

方波发生电路的最终的方波和二分频后的频率结果。在仿真过程中遇到选择电路参数不对,导致不能产生波形。解决方法:查阅书籍资料,查找电路工作的相位条件和起振条件,计算出相应的参数值重新仿真。实物制作过程中遇到如何给放大器供电、选用放大器的型号以及测量波形。解决方法:请教老师以及查找芯片使用手册,以及放大器参数性能等方面的知识,选择好专用性较强的芯片。

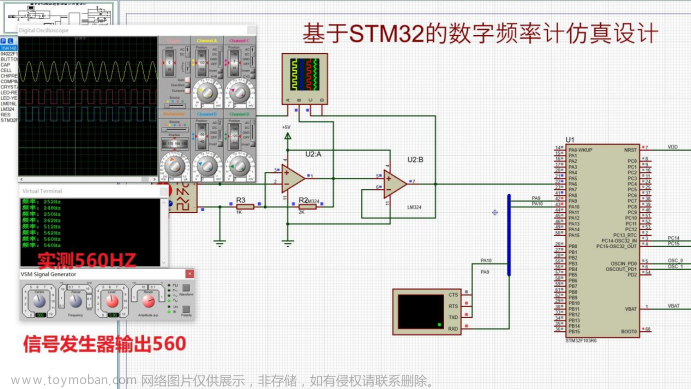

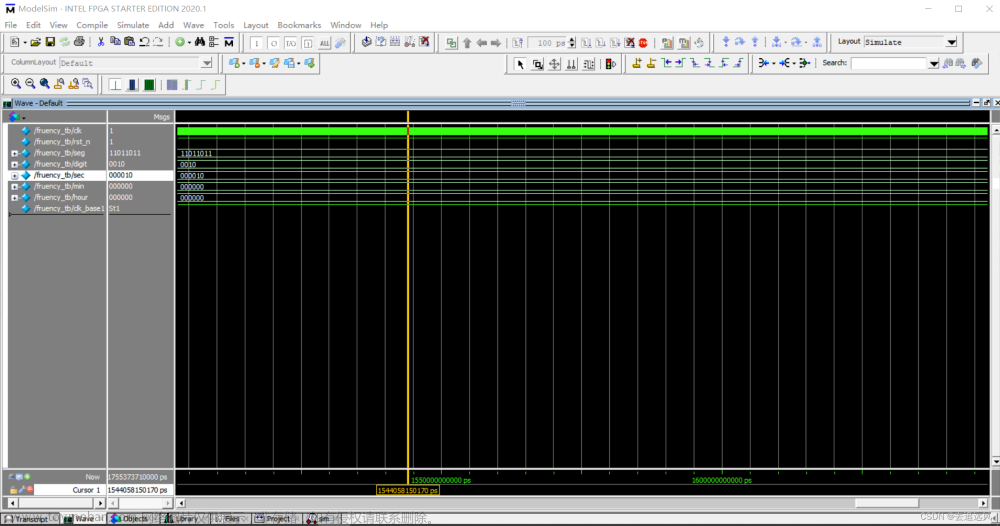

8、频率显示仿真结果

经单片机处理后显示电路产生的方波频率。遇到由于软件程序编写的不当导致测量输出的信号的频率相差很大或者不能正常显示。解决方法:用KEIL这款软件结合JLINK仿真器在线调试,排查错误,修改程序最终得到正确结果。

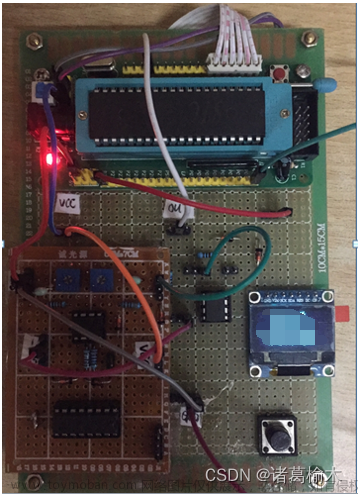

8、实物制作

最终实物图,在制作过程中遇到了将不同的模块连接到一起时电路不能达到最优工作以及所选的放大器性能不够导致波形不正。解决方法:优化电路参数,将电路数字地和模拟隔开,最后相连接;换用性能比较好的放大器,对软件方法做局部调整达到测量结果准确的目的。

(如果错误,欢迎批评指正,请大佬轻喷)文章来源:https://www.toymoban.com/news/detail-492202.html

代码在我的资源中下载即可文章来源地址https://www.toymoban.com/news/detail-492202.html

到了这里,关于基于51单片机的频率计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!