这篇具有很好参考价值的文章主要介绍了FPGA开发环境安装VIVADO。希望对大家有所帮助。如果存在错误或未考虑完全的地方,请大家不吝赐教,您也可以点击"举报违法"按钮提交疑问。

BASYS3开发板使用的是 Xilinx

厂商的

Artix-7 FPGA 芯片,所以要使用

Xilinx

提供的配套开发软件

Vivado

,我使用的是

Vivado 18.3

。Vivado 18.3

的版本相对来说是较为稳定的,所以推荐给大家这个版本当然 读者也可安装更新的版本,安装步骤都是大同小异的。

第一步: 找到 Vivado 2018.3

软件应用程序安装包。安装包可在我们提供的资料中获取,以

管理员身份运行“xsetup.exe”应用程序,

不用选择最新版

第二步:开始进入安装界面,按照步骤进行安装

框中勾上接受条款,然后点击“Next”。

这里我们直接点击 “Install”安装即可。

这里我们直接点击 “Install”安装即可。

安装完成后会提示你相关软件的安装

安装完成后会提示你相关软件的安装

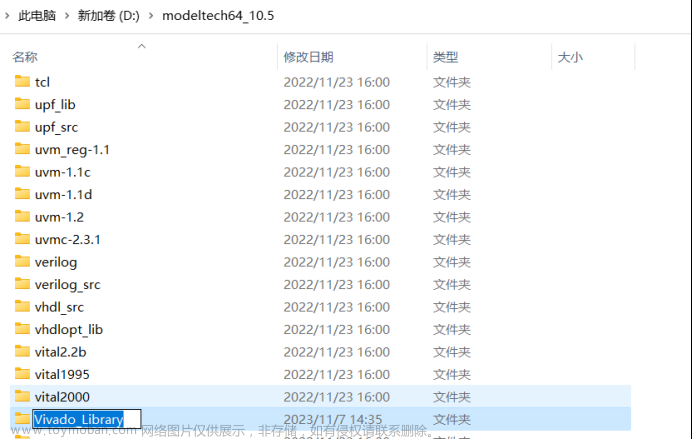

安装完成后我们需要导入license文件

安装完成后我们需要导入license文件

获取软件

百度网盘:https://pan.baidu.com/s/1PiQO1BeLSZNFn_BrqanyFw

提取码:TWp5 文章来源:https://www.toymoban.com/news/detail-492543.html

文章来源地址https://www.toymoban.com/news/detail-492543.html

到了这里,关于FPGA开发环境安装VIVADO的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处: 如若内容造成侵权/违法违规/事实不符,请点击违法举报进行投诉反馈,一经查实,立即删除!

这里我们直接点击 “Install”安装即可。

这里我们直接点击 “Install”安装即可。

安装完成后会提示你相关软件的安装

安装完成后会提示你相关软件的安装

安装完成后我们需要导入license文件

安装完成后我们需要导入license文件