推荐查看原文:硬件电路设计之泄放电路设计泄放电路就是将一部分电能转换成热能或者其它形式能量的电路。相信大家应该都有碰到过下面这些问题:单板下https://mp.weixin.qq.com/s/2DOr15hqAAaWzcq5QA-s-Q

1 简介

泄放电路就是将一部分能量转换成热或者其它形式能量的电路。单板断电后,LED灯长时间没有熄灭,就是对储能器件的能量没有合理的泄放掉。

余电快速泄放电路,即放电电路,用在需要快速反复开关电源,且负载电路上有大容量电容的场景。断开电源开关后,如果负载电路有大电容,会引起负载电路上的电压下降缓慢。此时如果重新接上电源开关,负载电路在未完全掉电的情况下重新上电,可能会导致电路不能正常复位启动,进而电路工作异常,出现开机死机等情况。

2 参考资料

推荐一款带泄放功能的电源芯片,资料获取方式:关注下面公众号,回复:SGM25661即可。

3 电路分析

3.1 上电过程分析

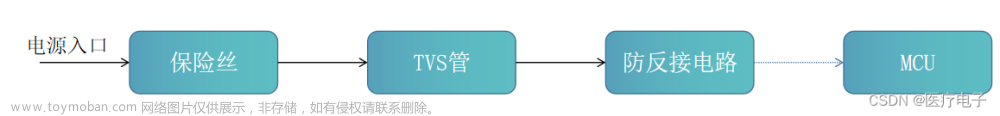

上电瞬间,三极管的基极b为高电平,三极管Q1截止,VCC通过D1给C1进行充电。

3.2 下电过程分析

下电瞬间,三极管Q1的基极b被电阻R1拉低,D1由于其单向导电性,相当远断开,电流从Q1的集电极流向发射极,最终构成回路。注意电阻R2的阻值不宜过大,否则会影响泄放的速度。

总结分析:

此电路图最大的一个优势就是关断时间极快,让MOS管栅源之间电容电压快速泄放,快速关断MOS,最大努力去保护电路。当我们需要打开MOS管时,电源IC的IO口输出一个高电平,驱动打开MOS管,即可给负载进行供电。当遇到特殊情况检测到短路或者其他情况需要快速关断MOS时,电源IC的IO口输出一个低电平,三极管Q5会被打开,MOS管栅源之间的电压会通过黄色回路,迅速释放以关断MOS。还有一个好处就是MOS管栅源之间的电压,泄放回路不需要经过电源IC,极大的提高了电路的可靠性。

4 应用场景

-

我们在设计电源指示灯时,常常会由于电容放电的原因,导致下电后,LED灯仍然常亮。

-

复位电路设计过程中,如果电量没有释放完毕,重新上电,可能会导致上电失败。文章来源:https://www.toymoban.com/news/detail-494119.html

在泄放电阻工作的速度和功率浪费量之间总是存在折衷。 较低的泄放电阻值会使您在设备断电时更快地达到安全电压,但在操作过程中会浪费更多功率。文章来源地址https://www.toymoban.com/news/detail-494119.html

到了这里,关于数字电路硬件设计系列(七)之泄放电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!