Vivado HLS是将基于C/C++描述的算法转化成相应的RTL代码,最终在FPGA上实现。这就要求软件工程师对FPGA的内部架构有一些基本的认识,目的在于保证生成的RTL代码在性能和资源上能够达到很好的平衡。实际上,C语言与FPGA是有一些对应关系的。比如:

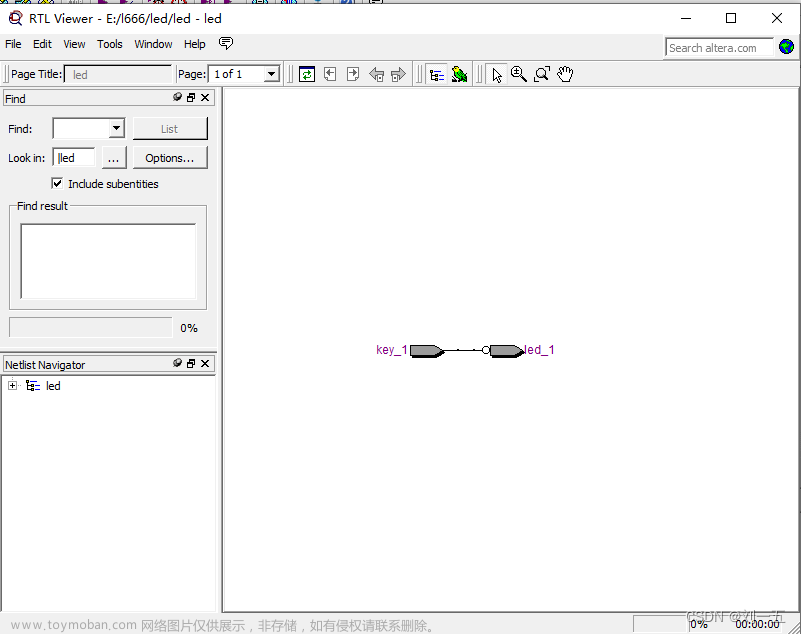

C语言中的数组可对应于FPGA中的寄存器、分布式RAM、Block RAM或者UltraRAM

C语言中的乘加运算可对应于FPGA中的乘加运算单元(DSP48)

但不同于硬件工程师,对于FPGA内部其他资源比如高速收发器等,软件工程师可不必了解。

本讲从软件工程师的视角重点介绍FPGA内部常规逻辑单元,包括查找表(LUT)、乘加运算单元(DSP48)、存储单元(Block RAM)。这三类资源在算法开发中或多或少都会用到,在Vivado HLS的综合报告中也有所体现。

1. VIVADO HLS的设计流程

2. C/C++表述算法时的代码风格

3.FOR循环的优化方法

4.数组的优化方法

5.I/O端口的实现方式

FPGA包括传统FPGA,其中包括7-series ,UltraScale,UltraScale+,而SOC系列包括Zynq-7000和 UltraScale+ MPSOC.FPGA被称为液态硬件。

UltraScale+ MPSOC.FPGA被称为液态硬件。

CPU,DSP和GPU都属于软件可编程。

CPU:管理和调度,文件的管理和人机交互。

DSP:算法方面有所加强

GPU:可以同时执行多个进行,适用于大块数据流传输。

面对大数据量时的解决方法:

1.提高主频

2.增加并行度

FPGA属于硬件可编程

1.内部包含大量乘法单元,算法方面有很高的并行度。

2.ARM内嵌,提高管理能力

3.功耗有所改善

4.采用C/C++编程

FPGA架构

其中包括可编程逻辑单元,布线资源和可编程I/O资源。

软件工程师应更多的关注存储单元,算术逻辑单元和逻辑单元。

逻辑单元:包括LUT,MUX,FF等

实现加法运算需使用查找表。

DSP资源实现乘法,乘累加等计算

对于大块数据存储使用BRAM,小于1kb时使用LUT资源即可。

其中BRAM由18kb单元构成,而18kb单元可以构成4种类型的存储单元,包括36kb的BRAM和36KB的FIFO,18kb的BRAM和18KB的FIFO,18kb的BRAM和18kb的BRAM。

可以通过6种模式进行体现,包括单端口ram,简单双端口ram,真双端口RAM,单端口ROM,双端口ROM和FIFO。

数组进行综合时会映射成RAM的资源。

软件工程师进行编程时需要了解的内容。

1. 应当了解FPGA内部每个单元的功能

2 具体算法的操作和FPGA单元功能对应的关系

3. 算法模型的资源利用率文章来源:https://www.toymoban.com/news/detail-494205.html

4. 优化的方法文章来源地址https://www.toymoban.com/news/detail-494205.html

到了这里,关于Vivado HLS 第1讲 软件工程师该怎么了解FPGA架构的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!