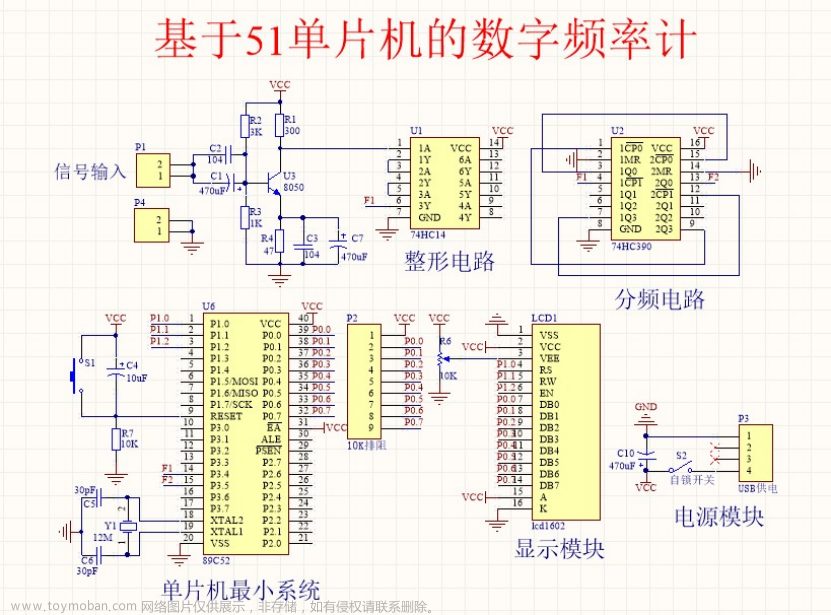

51单片机数字频率计仿真设计

(proteus仿真+程序+原理图+参考报告+器件清单)

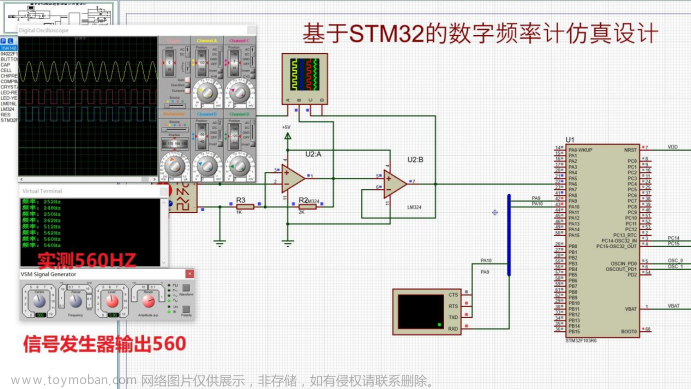

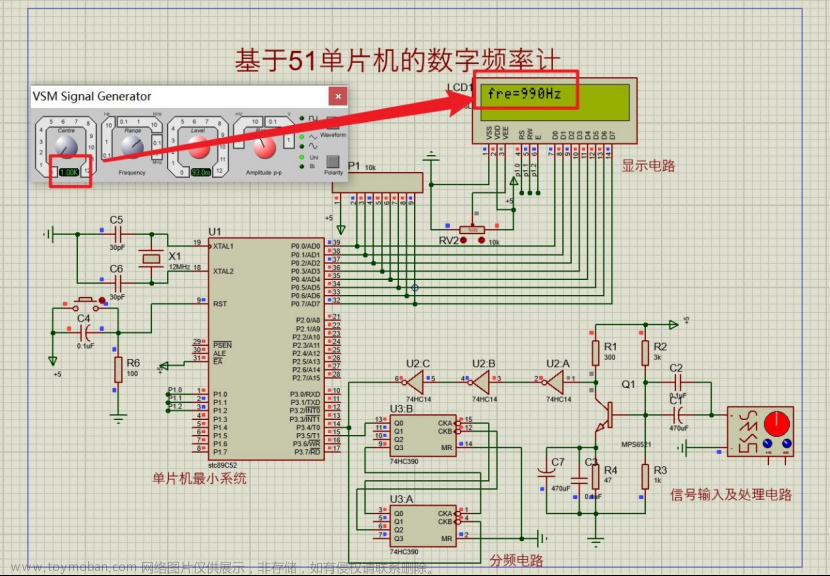

仿真图proteus 8.9

程序编译器:keil 4/keil 5

编程语言:C语言

设计编号:C0052

主要功能

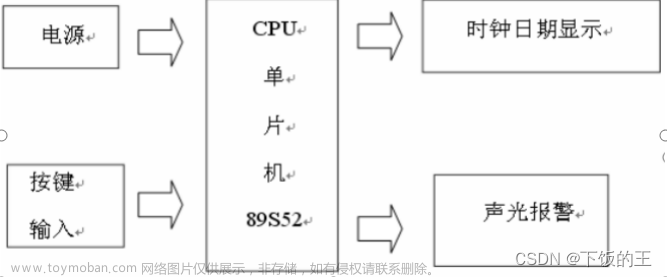

由51单片机+信号输入+74HC14整形电路+74HC390分频电路+LCD1602显示模块+电源构成。

1、能测出正弦波、三角波或方波等波形的频率;

2、频率的测量范围为1Hz—12MHz,且能检测幅度最小值为1Vpp的信号;

3、通过LCD1602液晶显示屏显示检测到的即时频率数值(最多8位数,单位为Hz)。

全部资料包括程序(注释)、AD原理图、protues仿真、参考论文、讲解、资料使用介绍等。

任务书

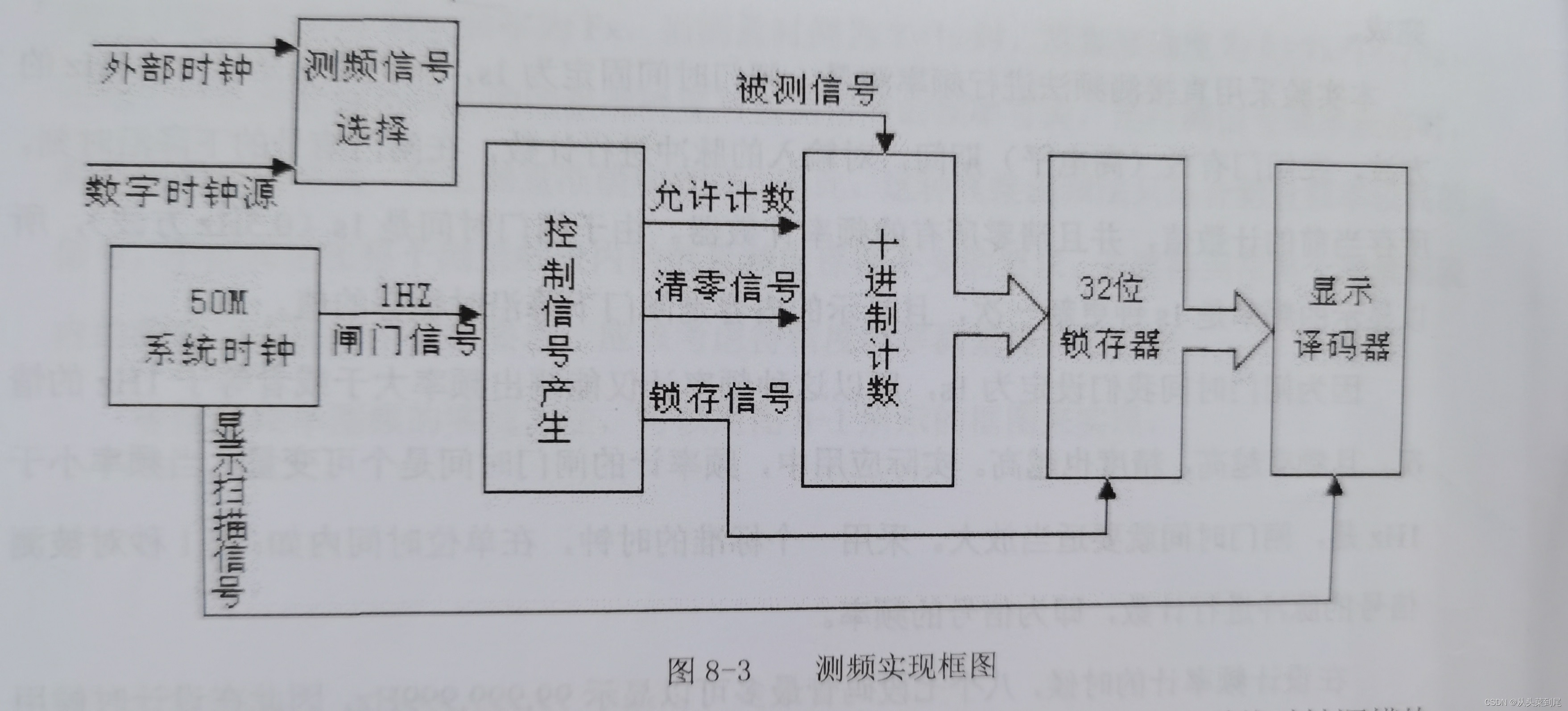

数字频率计是一种基本的测量仪器。它被广泛应用于航天、电子、测控等领域,还被应用在计算机及各种数学仪表中。一般采用的是十进制数字,显示被测信号频率。基本功能是测量正弦信号,方波信号以及其他各种单位时间内变坏的物理量。由于其使用十进制数显示,测量迅速精确,显示直观,所以经常被用来使用。

本文主要介绍数字频率计的设计和调试,本作品是基于52单片机作为平台,基本原理是通过52单片机进行频率的采集和分析工作,在通过程序使其显示在LCD1602的液晶显示屏上,通过液晶显示屏,让使用者能够直观的看到当前的输入频率是多少。

由于52单片机能处理的频率信号强度有限,所以这次我们先用74HC390芯片对输入的信号进行了分频,使其降低了100倍,才送去给单片机处理,而且为了使1602液晶显示屏能更好的兼容,在程序上我们做了三次初始化。

实物图

仿真图

在电子测量领域中,频率测量的精确度是最高的,可达10至10 数量级。因此,在生产过程中许多物理量,例如温度、压力、流量、液位、PH值、振动、位移、速度、加速度,乃至各种气体的百分比成分等均用传感器转换成信号频率,然后用数字频率计来测量,以提高精确度。

数量级。因此,在生产过程中许多物理量,例如温度、压力、流量、液位、PH值、振动、位移、速度、加速度,乃至各种气体的百分比成分等均用传感器转换成信号频率,然后用数字频率计来测量,以提高精确度。

国际上数字频率计的分类很多。按功能分类,因计数式频率计的测量功能很多,用途很广。所以根据仪器具有的功能,电子计数器有通用和专用之分。一、通用型计数器:通用型计数器是一种具有多种测量功能、多种用途的万能计数器。它可测量频率、周期、多周期平均值、时间间隔、累加计数、计时等;若配上相应插件,就可测相位、电压、电流、功率、电阻等电量;配上适当的传感器,还可进行长度、重量、压力、温度、速度等非电量的测量。二、专用计数器:专用计数器指专门用来测量某种单一功能的计数器。如频率计数器,只能专门用来测量高频和微波频率;时间计数器,是以测量时间为基础的计数器,其测时分辨力和准确度很高,可达ns数量级;特种计数器,它具有特种功能,如可逆计数器、阈值计数器、差值计数器、倒数计数器等,用于工业和自控技术等方面。数字频率计按频段分类:①低速计数器:最高计数频率<10MHz;②中速计数器:最高计数频率10—100MHz;③高速计数器:最高计数频率>100MHz;④微波频率计数器:测频范围1—80GHz或更高。

原理图

此次智能电子设计与制作实训本小组的题目为“数字频率计的设计”,在仔细研究了题目要求并通过小组内部积极细致的讨论之后,决定作品采用的功能方案如下:①能测出正弦波、三角波或方波等波形的频率。②频率的测量范围为1Hz—20MHz,且能检测幅度最小值为1Vpp的信号;③通过LCD1602液晶显示屏显示检测到的即时频率数值(最多8位数,单位为Hz)。值得一提的是,当输入频率大于20KHz的信号时,由于采用了100分频采样,显示结果稍有误差,如输入最大测量频率20MHz的信号时,LCD1602液晶显示屏上显示的测量结果为19998900HZ,误差不超过十万分之一,在可接受范围之内。

以下将以待测输入信号走向为顺序介绍电路中各个功能模块。

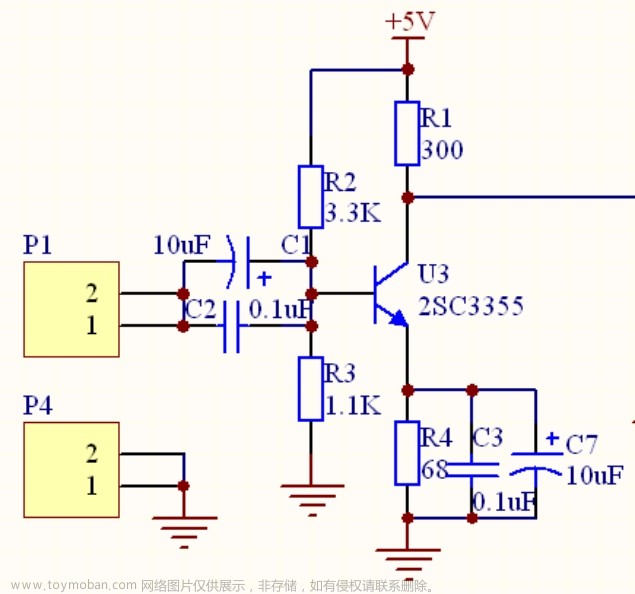

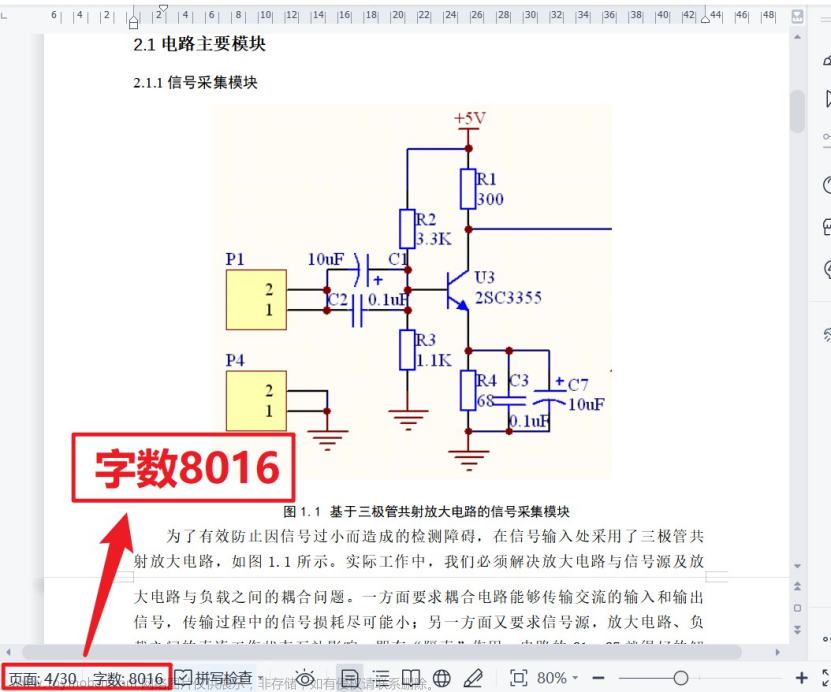

信号采集模块

为了有效防止因信号过小而造成的检测障碍,在信号输入处采用了三极管共射放大电路,如图1.1所示。实际工作中,我们必须解决放大电路与信号源及放大电路与负载之间的耦合问题。一方面要求耦合电路能够传输交流的输入和输出信号,传输过程中的信号损耗尽可能小;另一方面又要求信号源,放大电路、负载之间的直流工作状态互补影响,即有“隔直”作用,电路的C1、C7就很好的解决了这个问题即固定偏置共射极放大器。集电极电压通过基极偏置电阻R2使晶体管Je正偏;同时拖过R3使Jc反偏,从而实现信号源放大。

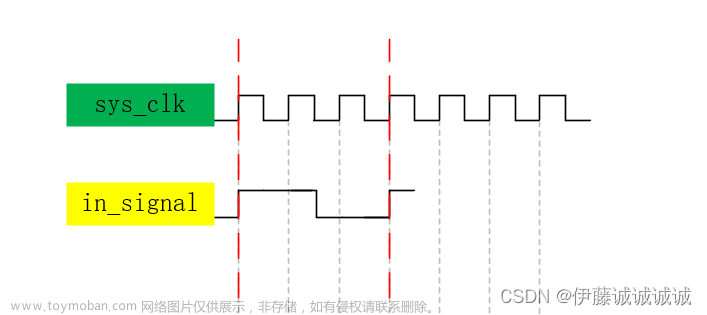

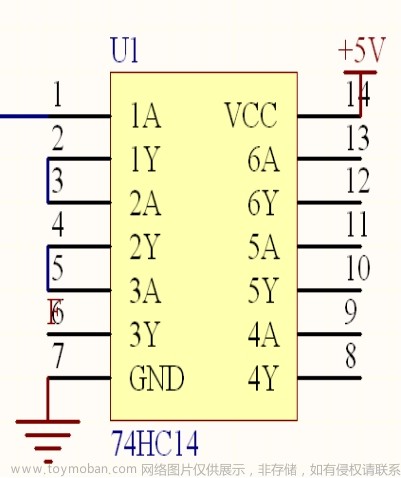

脉冲产生模块

脉冲产生模块采用74HC14实现了三次施密特触发并反相,从图1.2可以看出,来自信号采集模块的经过放大的信号从74HC14的1脚进入,经过1A→1Y、2A→2Y和3A→3Y三次施密特触发并反相最终将缓慢变化的输入信号转换成清晰、无抖动的信号从6脚输出。

分频模块

74HC390具有有八个主从触发器和附加门以构成两个独立的4位计数器,其中每个计数器皆包含两个部分:“除2计数部分”和“除5计数部分”,每个计数器又有一个清除输入和一个时钟输入。它可以实现等于2 分频、5 分频乃至100 分频的任何累加倍数的周期长度,且可以连成十进制计数器或二-五进制计数器以分别实现两种进制的数值输出。由于每个计数级都有并行输出,所以系统定时信号可以获得输入计数频率的任何因子。

74HC390具有以下特点:

①A和B触发器都有独立的时钟

②每个计数器都有直接清除

③有效提高系统密度

④缓冲输出减小集电极转换的可能性

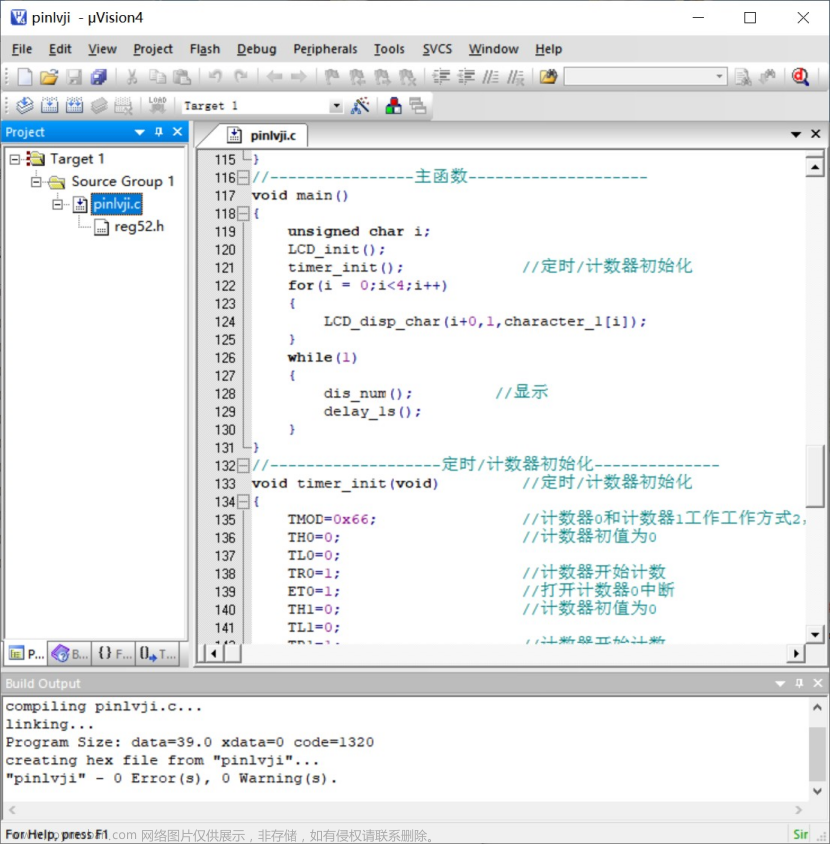

程序

主要代码

/----------------主函数--------------------

void main()

{

unsigned char i;

LCD_init();

timer_init(); //定时/计数器初始化

for(i = 0;i<4;i++)

{

LCD_disp_char(i+0,1,character_1[i]);

}

while(1)

{

dis_num(); //显示

delay_1s();

}

}

//-------------------定时/计数器初始化--------------

void timer_init(void) //定时/计数器初始化

{

TMOD=0x66; //计数器0和计数器1工作工作方式2,自动重装初值

TH0=0; //计数器初值为0

TL0=0;

TR0=1; //计数器开始计数

ET0=1; //打开计数器0中断

TH1=0; //计数器初值为0

TL1=0;

TR1=1; //计数器开始计数

ET1=1; //打开计数器1中断

RCAP2H=(65536-62500)/256; //在程序初始化的时候给RCAP2L和RCAP2H赋值,

RCAP2L=(65536-62500)%256; //TH2和TL2将会在中断产生时自动使TH2=RCAP2H,TL2=RCAP2L。

TH2=RCAP2H; //12M晶振下每次中断62.5ms(1s=1000ms=62.5ms×16)

TL2=RCAP2L;

ET2=1; //打开定时器2中断

TR2=1; //定时器2开始计时

EA=1; //开总中断

}

//------------------中断函数----------------------

void timer2(void) interrupt 5 //定时器2中断(62.5ms)

{

time++;

TF2=0; //定时器2的中断标志位TF2不能够由硬件清零,所以要在中断服务程序中将其清零

if (time==16) //定时1s时间到

{

time=0; //计时清0

EA=0; //关中断

fre=(long)count1*256+TL1; //count*256强制转换成long型,否则将不产生进位~先判断分频后(计数器1)

FLAG = 0;

if(fre<2000)//如果不到200KHz则读取分频前(计数器0)频率(200K÷100=2000)

{

fre = (long)count*256+TL0;

FLAG = 1;

}

if(!FLAG)

{

fre = fre *100;//100分频

}

TL0=0; //清零计数器0计数

TH0=0;

TL1=0;

TH1=0;

count=0; //清零计数器0计数

count1=0;

EA=1; //开中断

}

}

//----------------------------------------------------------------

void timer0(void) interrupt 1 //计数器0中断(100分频前)

{

count++;

}

//----------------------------------------------------------------

void timer1(void) interrupt 3 //计数器1中断(100分频后)

{

count1++;

}

设计报告

文章来源:https://www.toymoban.com/news/detail-494578.html

文章来源:https://www.toymoban.com/news/detail-494578.html

全部参考资料

资料下载链接

文章来源地址https://www.toymoban.com/news/detail-494578.html

文章来源地址https://www.toymoban.com/news/detail-494578.html

到了这里,关于基于51单片机数字频率计仿真设计(proteus仿真+程序+原理图+参考报告+器件清单)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!