这篇具有很好参考价值的文章主要介绍了《数字逻辑电路》期末考试。希望对大家有所帮助。如果存在错误或未考虑完全的地方,请大家不吝赐教,您也可以点击"举报违法"按钮提交疑问。

一、单项选择题(每小题 2 分,共 30 分)

1

、与八进制数

(24.4)8

对应的二进制数是( )。

A

.

(10101.1)

2

B

.

(10110.1)

2

C

.

(10100.1)

2

D

.

(11011.01)

2

2

.将

(01000011.00101000)

5421BCD

转换为八进制数为( )。

A

.

(43.25)

8

B

.

(53.2)

8

C

.

(35.25)

8

D

.

(56.5)

8

3

、若输入变量

A

、

B

只有全为

1

时,输出

F=0

,则其输入与输出的关系是( )。

A

.异或

B

.同或

C

.或非

D

.与非

4

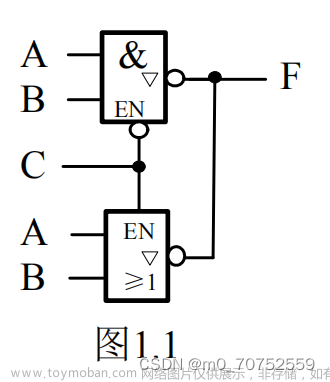

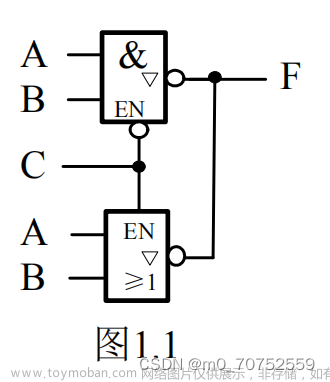

、逻辑电路如图

1.1

所示,其输出函数 F 为( )。

A

.

C=0

F =

A =

B

C=1

F =

AB

B

.

C=0

F =

0

C=1

F

=

1

C

.

C=0

F =

A =

B

C=1

F =

AB

D

.

F

=

AB =

C =

(

A

=

B

)

C

5

、逻辑函数用卡诺图化简时,八个逻辑相邻项合并可消去( )。

A

.一个变量

B

.二个变量

C

.三个变量

D

.四个变量

6

、

F =

AB

BC

的最小项表达式是( )。

A

.

F =

(0,2,3,4)

B

.

F =

(1,5,6,7)

C

.

F =

(0,1,4,6)

D

.

F =

(2,3,5,7)

7

、逻辑函数

F

=

(

AB

+

AB

)

+

(

A

Å

B

)

的最简与或式为( )。

A

.

A

+

B

B

.

A

+

B

C

.

A

+

B

D.

1

8

、逻辑函数

F

(

A

,

B

,

C

,

D

)

=

å

m

(0,1,2,4,6,7,8,9,10,12,14)

的最简与非式为

( )。

A

.

B

×

C

×

BD

×

BD

×

ABC

B

.

D

×

B

×

C

×

ABC

C

.

D

×

BC

×

ABC

D

.

D

×

BC

×

AB

×

C

9

、某函数的反函数是

F

A

B

AC

BD

,其原函数为( )。

A

.

F =

(

A +

B

)

A +

C

(

B +

D

)

B

.

F =

(

A +

B

)

A +

C

(

B +

D

)

C

.

F =

(

A +

B

) +

A +

C

(

B +

D

)

D

.

F =

(

A +

B

)

A +

CB +

D

10

、函数

F

(

ABCD

)

=

AC .

D +

AB .

C +

A.

BC +

ACD

约束条件

BD =

0

的最简与或

式为( )。

A

.

F =

AC +

AC

B

.

F =

ACD +

ABC +

ABC +

ABC

C

.

F =

AC +

AC

D

.

F =

BC +

BC

11

、在下列逻辑电路中,属于组合逻辑电路的是( )。

A

.寄存器

B

.编码器

C

.触发器

D

.计数器

12、所谓同步计数器是指( )。

A.各触发器的时钟端连在一起,统一由系统时钟控制

B.可用前级的输出做后级触发器的时钟

C.由同类型的触发器构成

D

.可用后级的输出做前级触发器的时钟

13

、为使

JK

触发器的状态由

0

到

0

,其激励端

JK

取值为( )。

A

.

x0 B

.

0X C

.

x1 D

.

1x

14、四位移位寄存器现态为

1101

,左移进两个

0

后再右移进一个

1

。其移位寄存器的状

态是( )。

A.0110

B.0111

C.0100

D

.1010

15

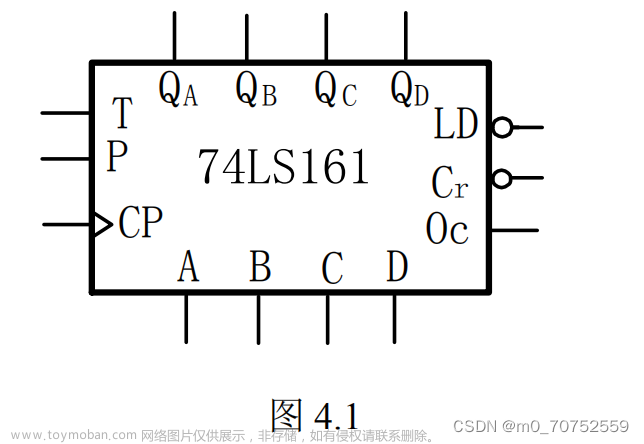

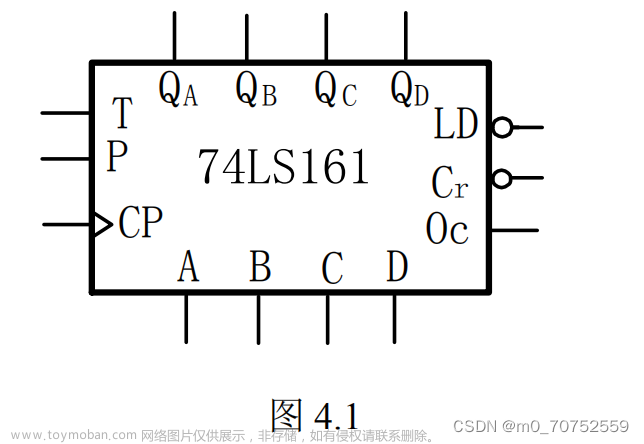

、

74

LS

161

当

C

r =

1;

LD =

0;

P =

1;

T =

1

。其功能是( )。

A.计数 B.预置数 C.清零 D.保持

二、填空题

16

、开路门输出并联完成

_______

逻辑功能。

17、一个自然二进制码为 1110,该格雷码是 。

18、F=A

Å

0

Å

A

Å

1

Å

0

Å

1=________________。

19

、时序电路的输出与当前输入有关,与电路过去状态

________________

。

20

、

150KHZ

输入信号,其分频的分频系数为

3

,输出频率为

____________

。

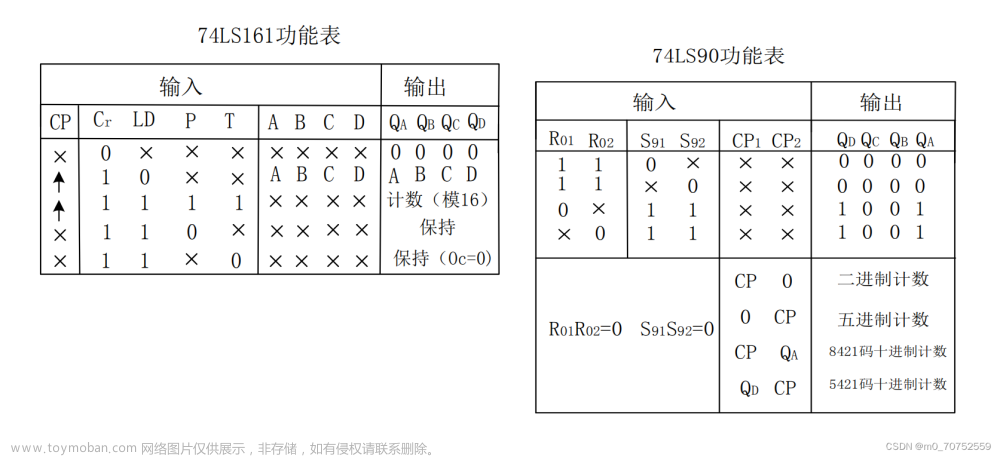

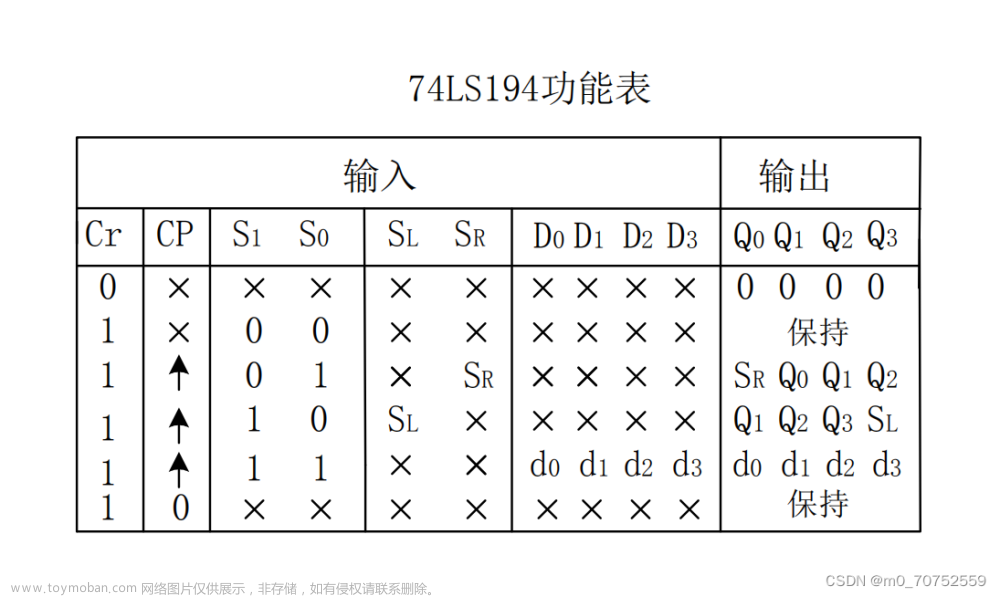

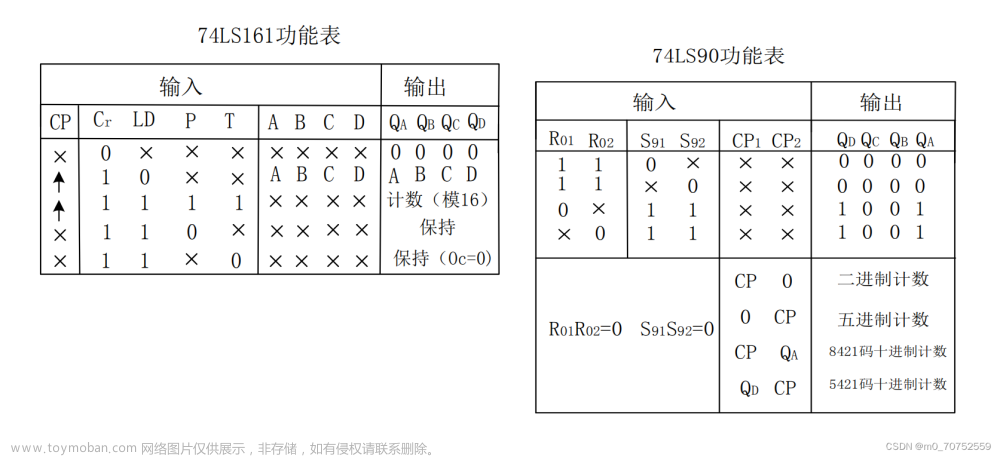

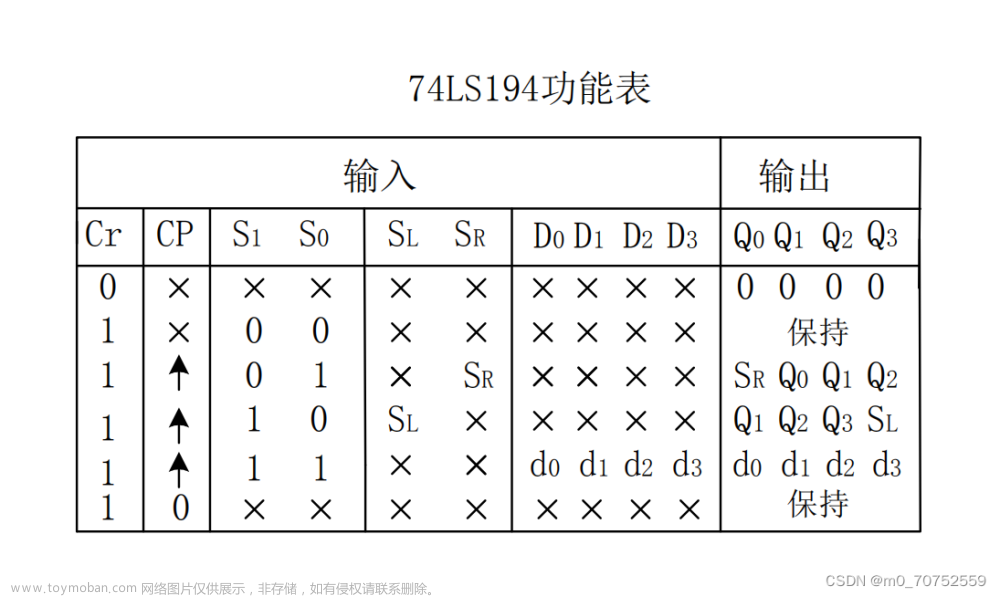

三、分析题

说明:中规模器件

74LS90

、

74LS161

和

74LS194

的功能见附页

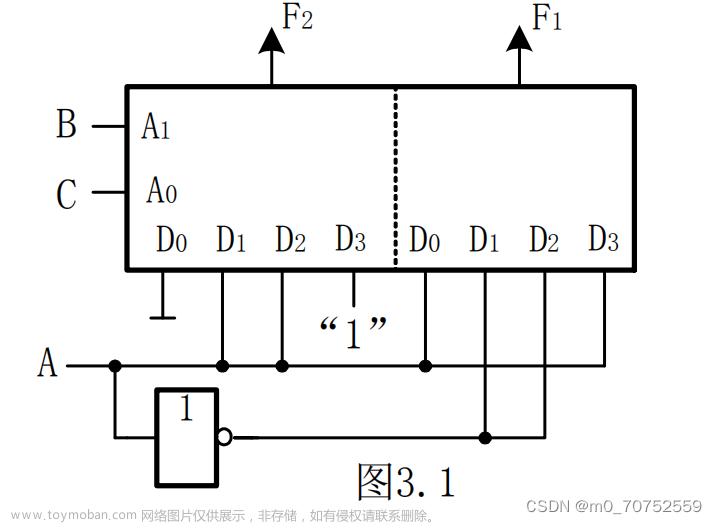

21

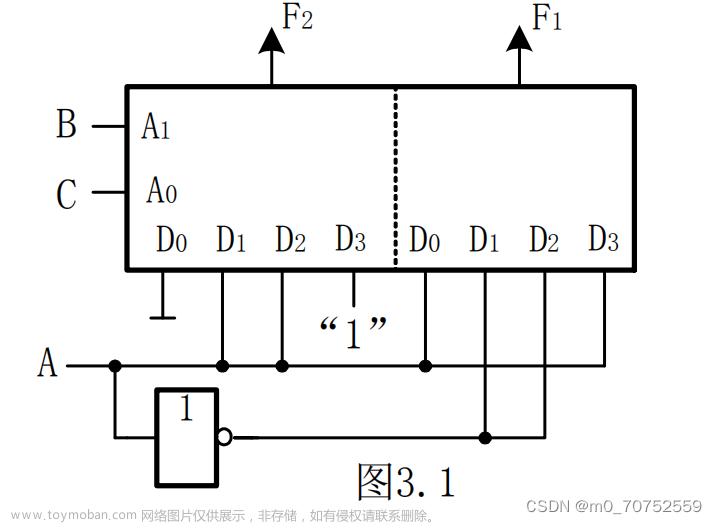

、由双

4

选

1

数据选择器组成电路如图

3.1

所示。

①写出输出函数

F

1

、

F

2

表达式;

②列出真值表;

③说明其功能。

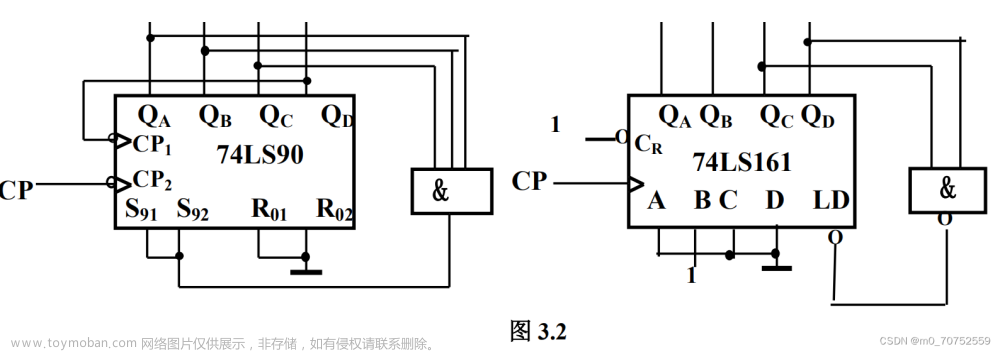

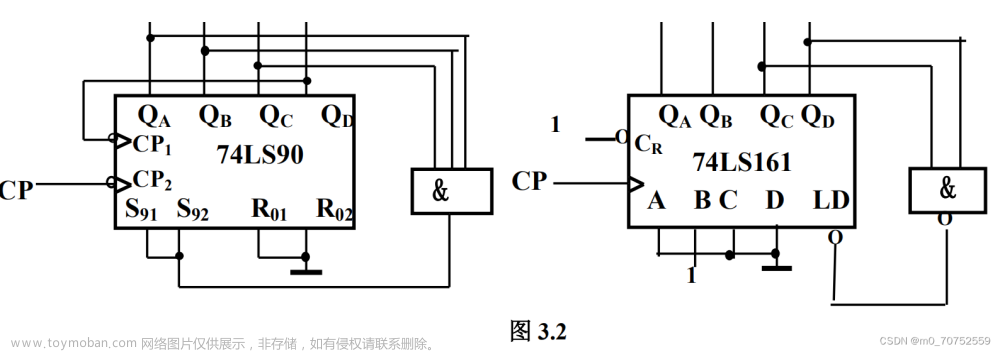

22

.电路如图

3.2

所示。

①分别列出图所示电路的状态迁移关系;

②分别指出电路的功能。

23

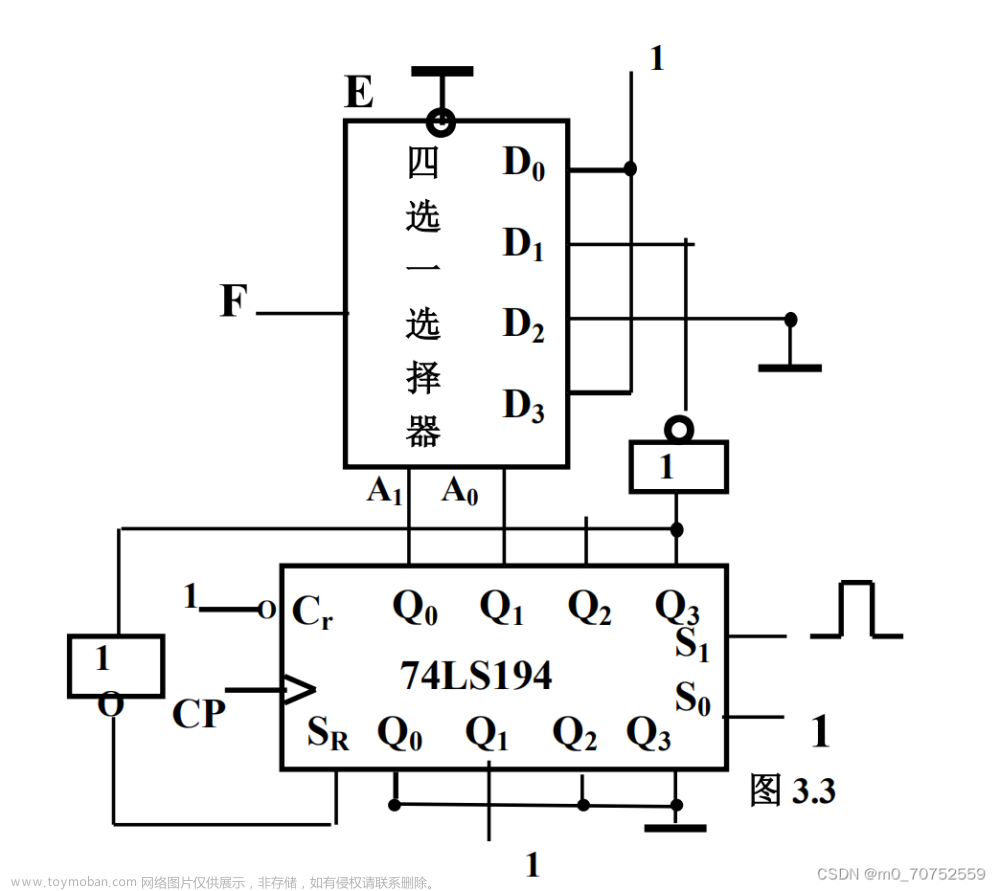

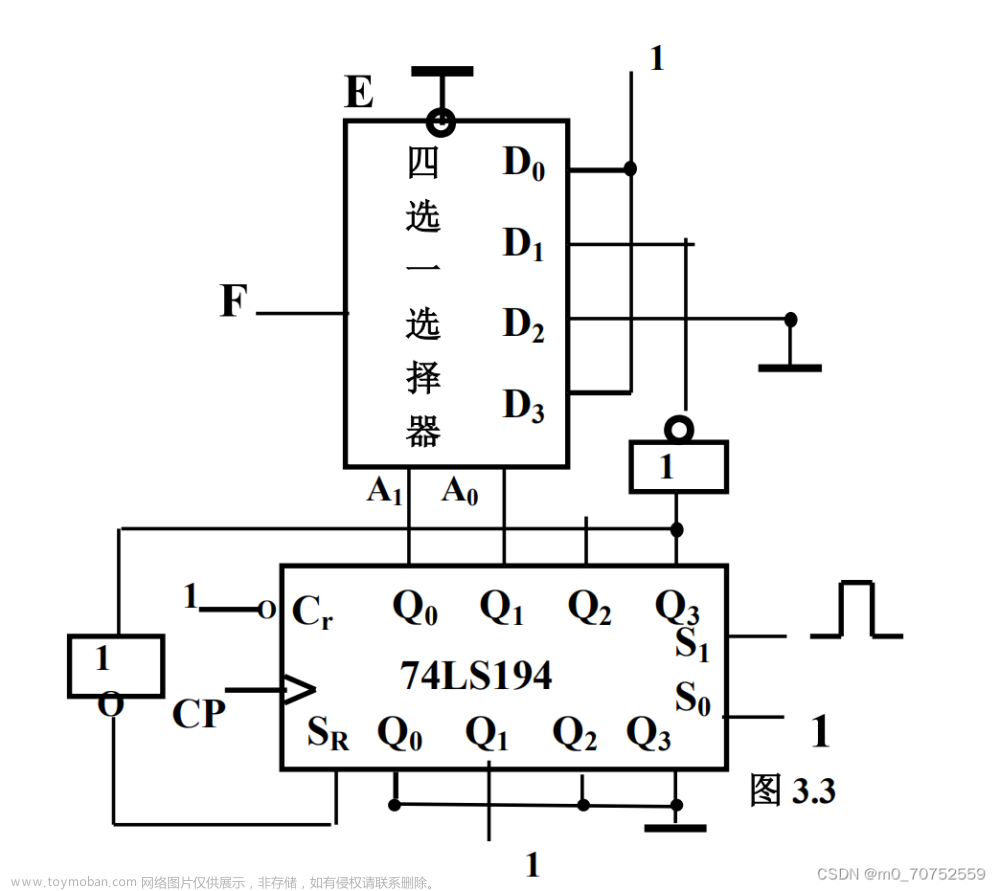

、由四选一数据选择器和移位寄存器

74LS194

组成电路如图

3.3

所示。

①列出

74LS194

的状态迁移关系;

②写出输出

F

的序列信号。

四、设计题

24、用 74LS138 译码器和少量的门电路设计一个转换电路,将输入的三位格雷码 G2G1G0

转换为三位二进制 B2B1B0。

①列出真值表;

②画出逻辑图。

25、试用 74LS161 设计一个起始态为 0100 的 9 进制计数器。

①列出状态迁移表;

②画出逻辑电路图。

26

、利用

JK

触发器设计同步三进制加法计数器。

①做出状态迁移表;

②确定每级触发器的激励函数;

③画出逻辑图。

文章来源:https://www.toymoban.com/news/detail-496474.html

文章来源:https://www.toymoban.com/news/detail-496474.html

文章来源地址https://www.toymoban.com/news/detail-496474.html

到了这里,关于《数字逻辑电路》期末考试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处: 如若内容造成侵权/违法违规/事实不符,请点击违法举报进行投诉反馈,一经查实,立即删除!

文章来源:https://www.toymoban.com/news/detail-496474.html

文章来源:https://www.toymoban.com/news/detail-496474.html

文章来源:https://www.toymoban.com/news/detail-496474.html

文章来源:https://www.toymoban.com/news/detail-496474.html